SEGA Confidential

General Notice

When using this document, keep the following in mind:

1. This document is confidential. By accepting this document you acknowledge that you are bound

by the terms set forth in the non-disclosure and confidentiality agreement signed separately and /in

the possession of SEGA. If you have not signed such a non-disclosure agreement, please contact

SEGA immediately and return this document to SEGA.

2. This document may include technical inaccuracies or typographical errors. Changes are periodi-

cally made to the information herein; these changes will be incorporated in new versions of the

document. SEGA may make improvements and/or changes in the product(s) and/or the

program(s) described in this document at any time.

3. No one is permitted to reproduce or duplicate, in any form, the whole or part of this document

without SEGA'S written permission. Request for copies of this document and for technical

information about SEGA products must be made to your authorized SEGA Technical Services

representative.

4. No license is granted by implication or otherwise under any patents, copyrights, trademarks, or

other intellectual property rights of SEGA Enterprises, Ltd., SEGA of America, Inc., or any third

party.

5. Software, circuitry, and other examples described herein are meant merely to indicate the character-

istics and performance of SEGA's products. SEGA assumes no responsibility for any intellectual

property claims or other problems that may result from applications based on the examples

describe herein.

6. It is possible that this document may contain reference to, or information about, SEGA products

(development hardware/software) or services that are not provided in countries other than Japan.

Such references/information must not be construed to mean that SEGA intends to provide such

SEGA products or services in countries other than Japan. Any reference of a SEGA licensed prod-

uct/program in this document is not intended to state or simply that you can use only SEGA's

licensed products/programs. Any functionally equivalent hardware/software can be used instead.

7. SEGA will not be held responsible for any damage to the user that may result from accidents or any

other reasons during operation of the user's equipment, or programs according to this document.

(6/27/95- 002)

NOTE: A reader's comment/correction form is provided with this

document. Please address comments to :

SEGA of America, Inc., Developer Technical Support (att. Evelyn Merritt)

150 Shoreline Drive, Redwood City, CA 94065

SEGA may use or distribute whatever information you supply in any way

it believes appropriate without incurring any obligation to you.

|

SEGA Confidential

TM

© 1994 SEGA. All Rights Reserved.

Saturn

SCSP

User's Manual

Doc. # ST-77-R2-052594

|

SEGA Confidential

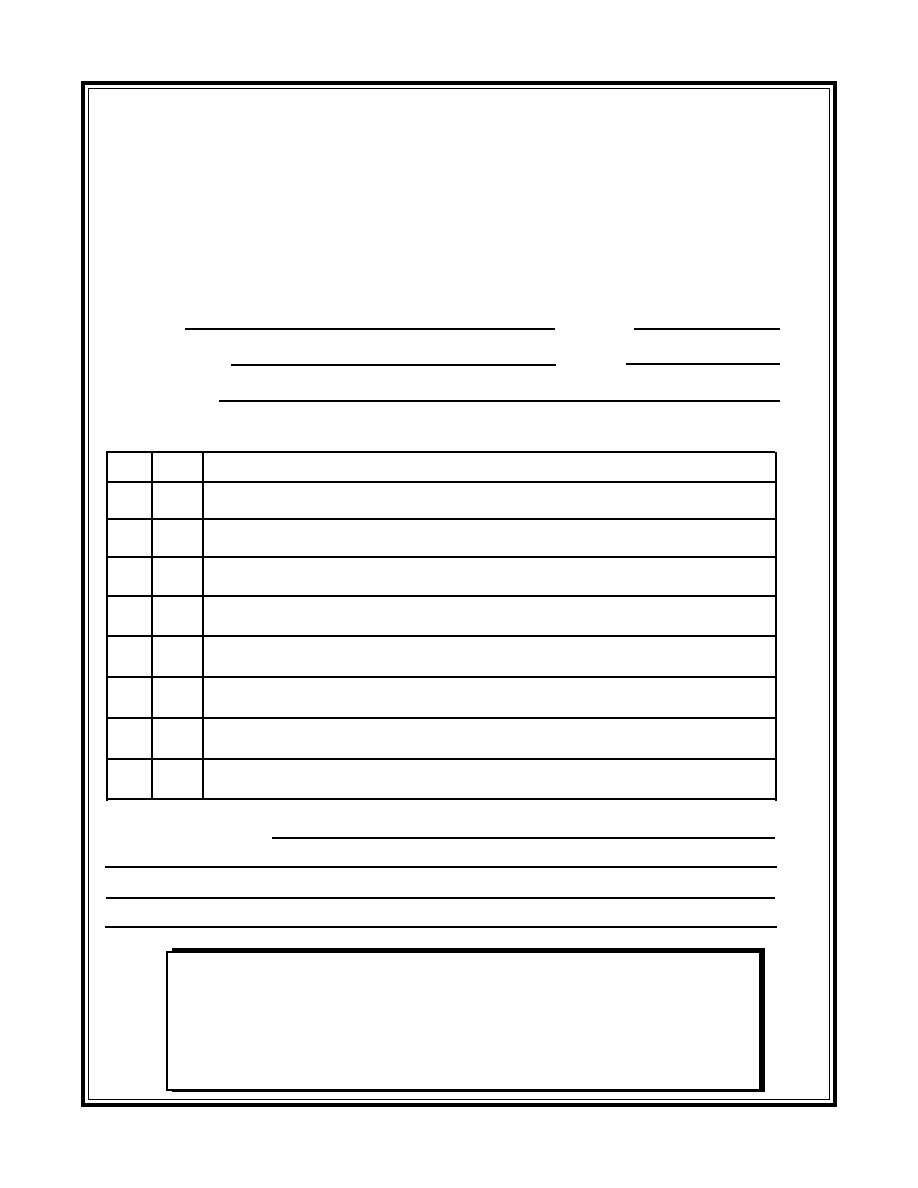

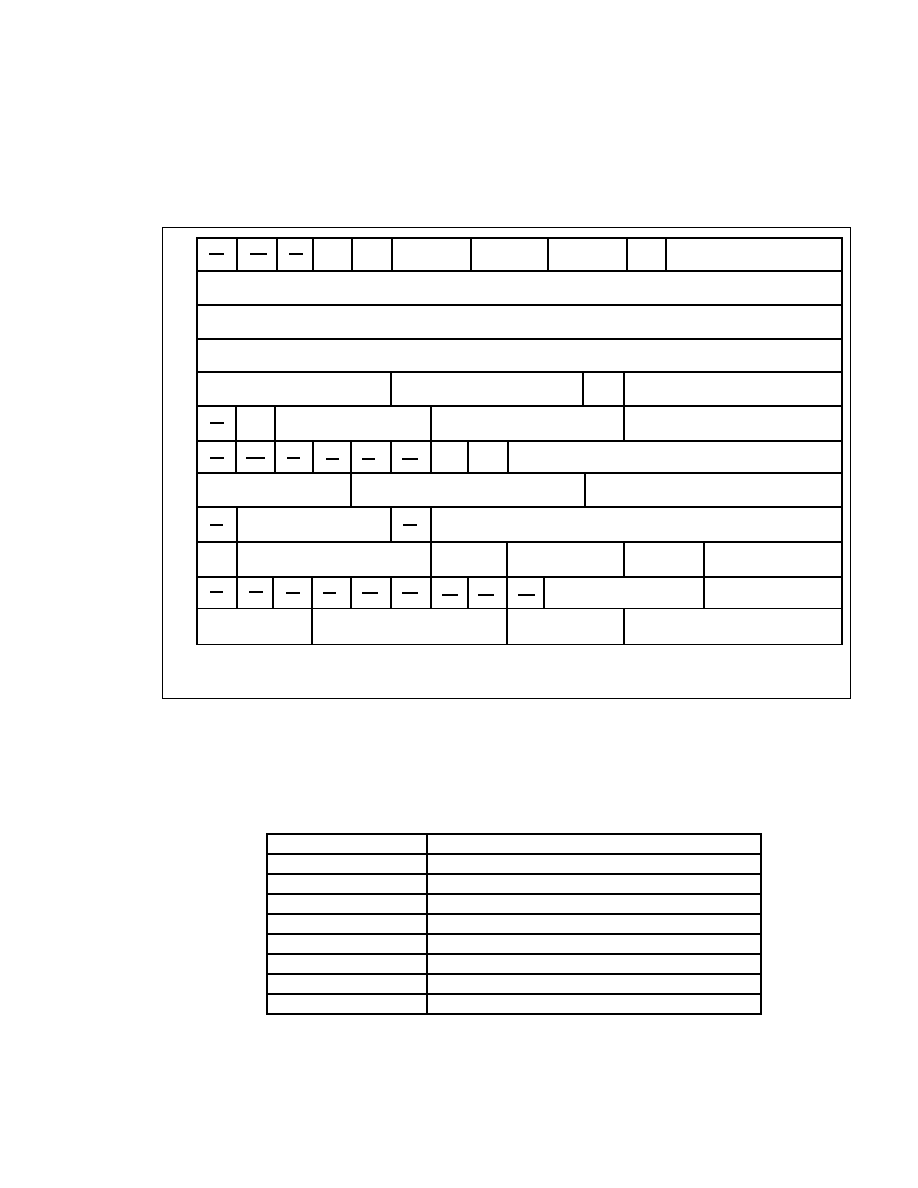

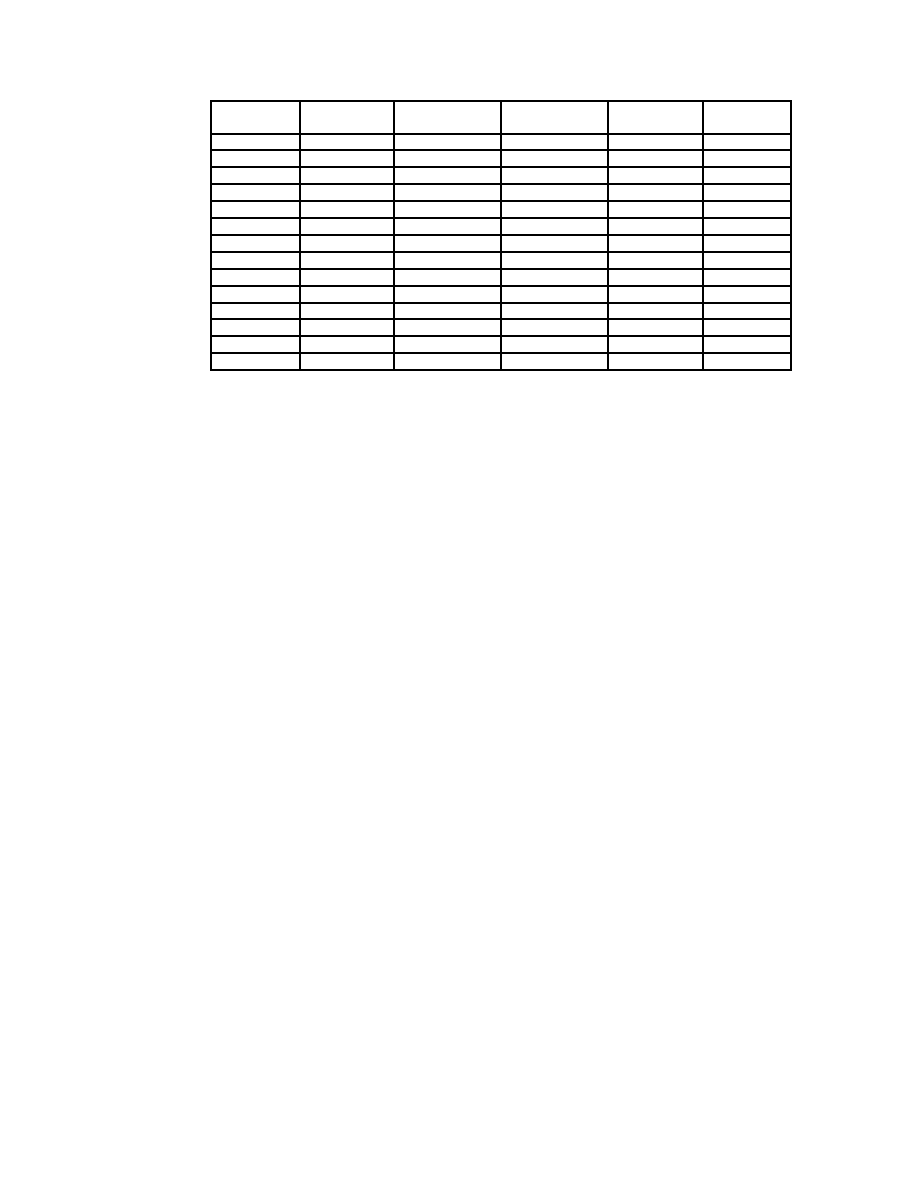

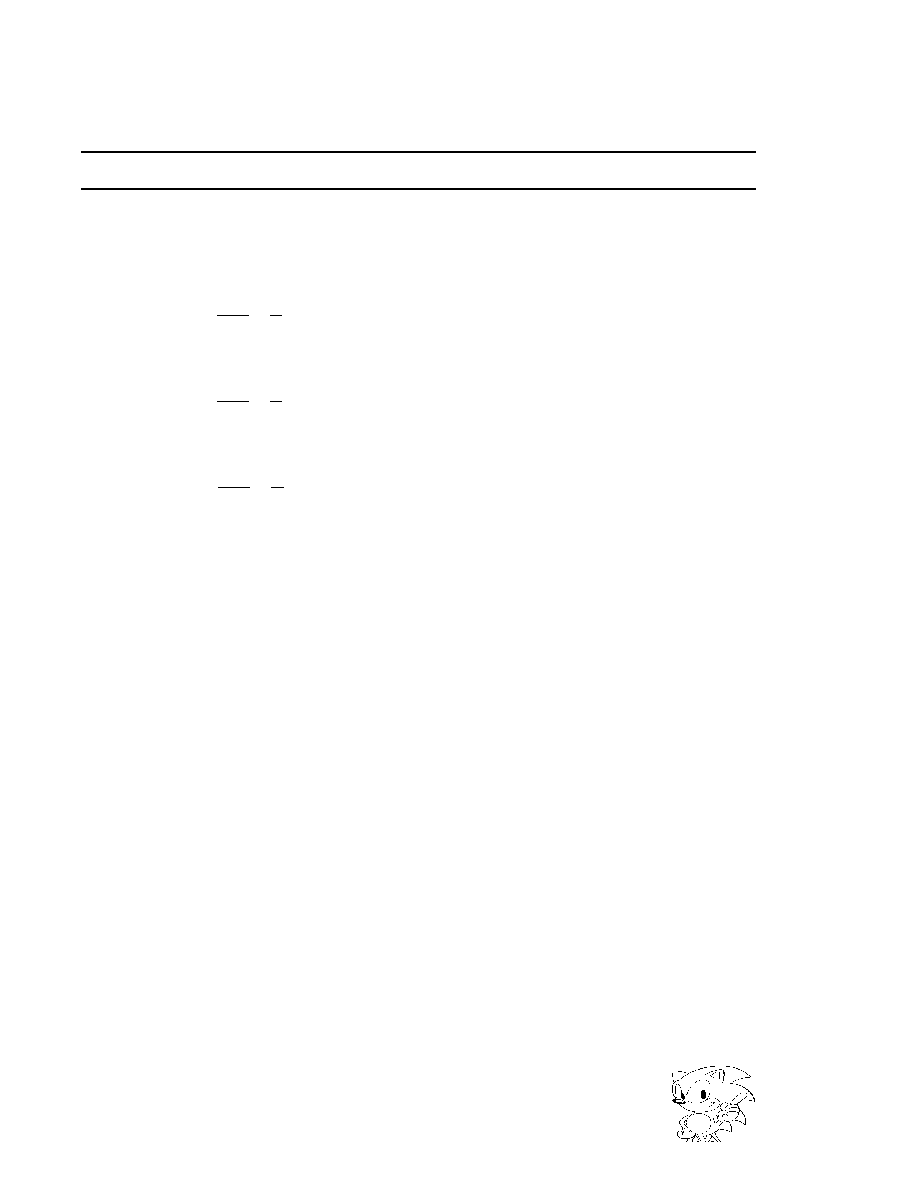

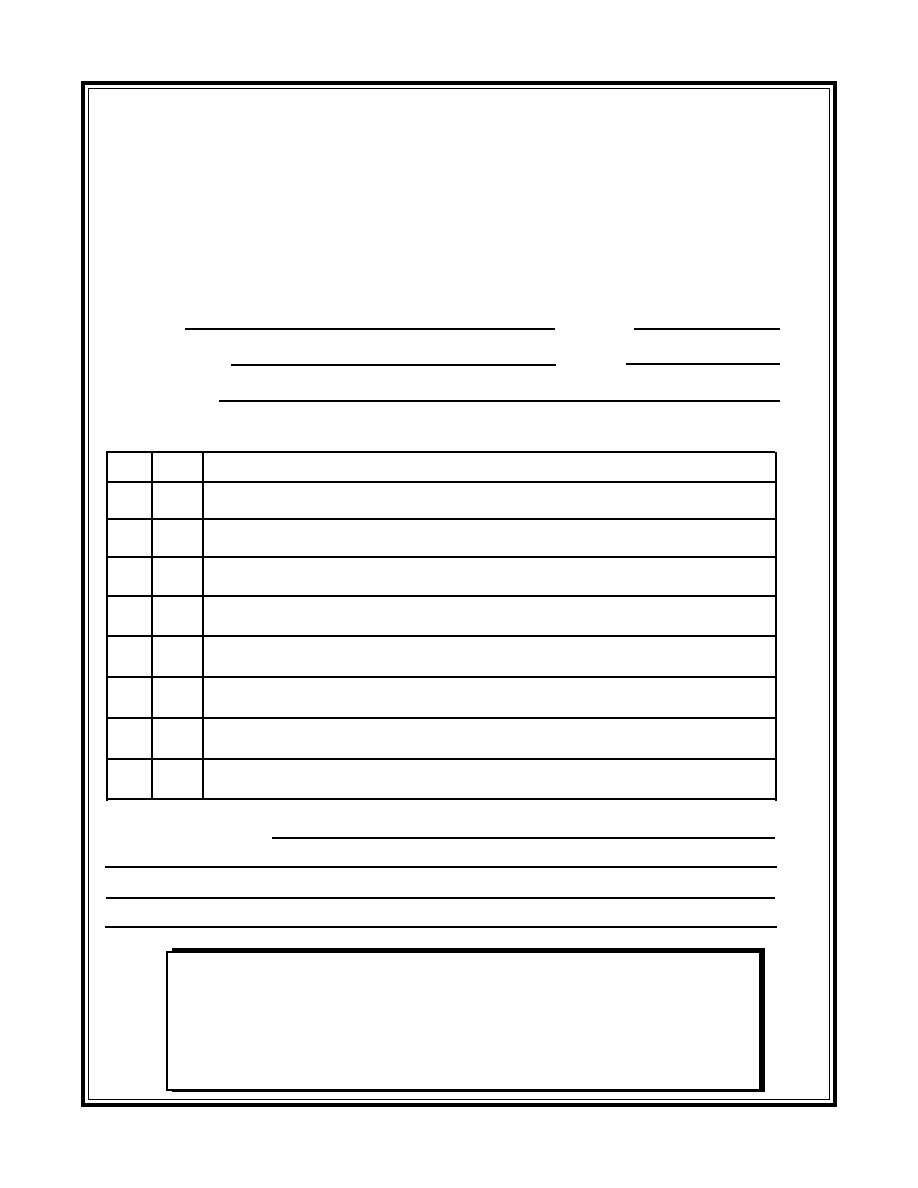

READER CORRECTION/COMMENT SHEET

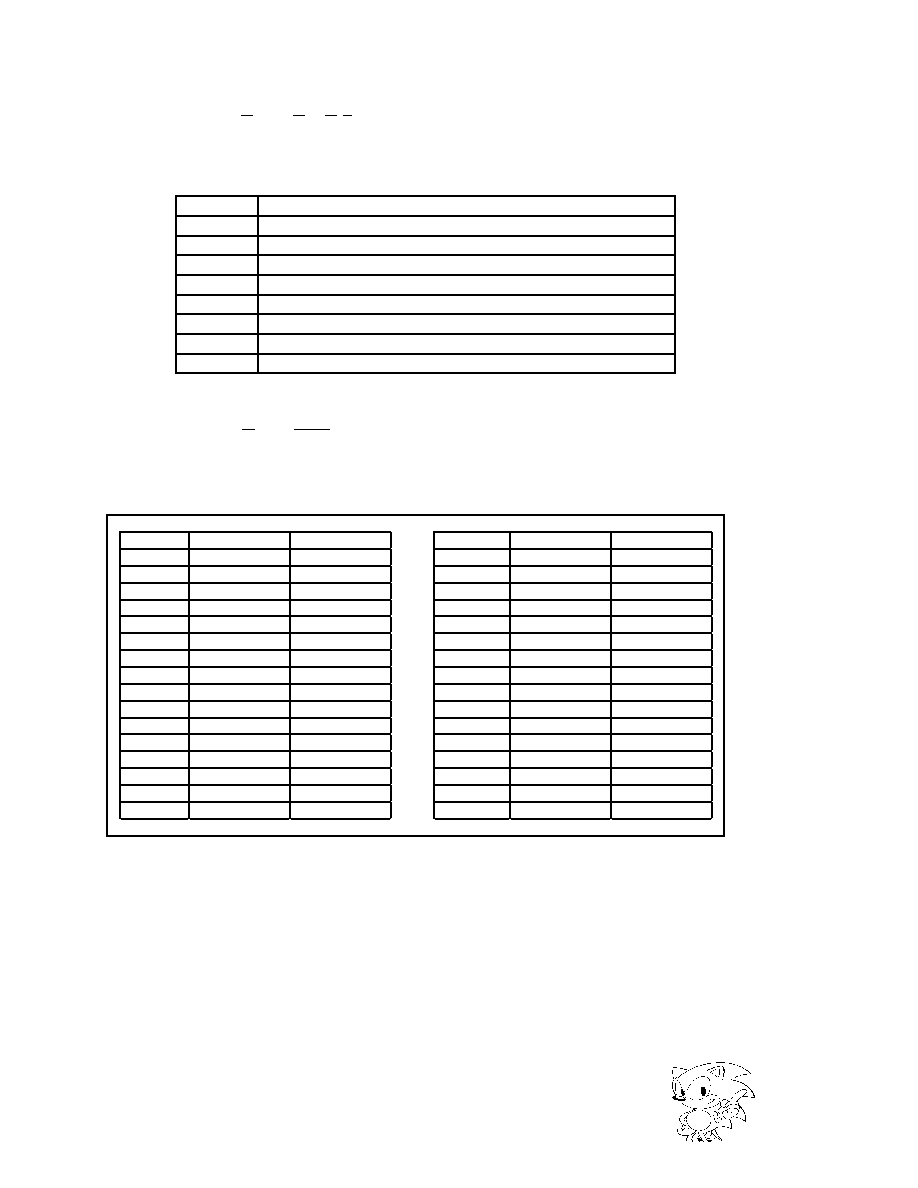

Chpt.

pg. #

Correction

Corrections:

General Information:

Your Name

Phone

Document number

Date

Document name

Questions/comments:

Keep us updated!

If you should come across any incorrect or outdated information while reading through the attached

document, or come up with any questions or comments, please let us know so that we can make the

required changes in subsequent revisions. Simply fill out all information below and return this form to

the Developer Technical Support Manager at the address below. Please make more copies of this form if

more space is needed. Thank you.

Fax:

(415) 802-3963

Attn: Manager,

Developer Technical Support

Mail:

SEGA OF AMERICA

Attn: Manager,

Developer Technical Support

275 Shoreline Dr. Ste 500

Redwood City, CA 94065

Where to send your corrections:

ST-77-R2-052594

Saturn SCSP User's Manual

|

SEGA Confidential

History

First Edition: (November 30, 1993)

· New manual

Second Edition:

(January 8, 1994)

· Corrected page numbers

Third Edition:

(February 24, 1994)

· Revisions based on the Feb. 8, 1994, meeting.

|

SEGA Confidential

Introduction

Definitions

Terms used in this manual are defined below.

SCSP (Saturn Custom Sound Processor)

A multi-function game sound generator LSI that combines a PCM

sound generator and sound DSP.

Data

A bit indicates 0 or 1 and is the smallest unit. 8 bits combined

together is called a byte, and 16 bits (or 2 bytes) is called a word.

When upper and lower grade is divided into 4 bits respectively,

they are called nibbles.

PAN-POT

Determines the direction or location from which the sound seems to

come from in localization.

Direct Data

Sound that does not pass through the DSP, or even if it did, no

effects were applied. Also called "dry data".

Effect Data

The sound generated, as a result of sending it through DSP with an

effect created in the sound generator. Also called "wet data".

MIDI Standard (Musical Instrument Digital Interface)

Conversion standard for sound interval and sound length used to

communicate between electronic instruments and computers.

Pulse Code Modulation Sound Generator

Sound is converted to PCM data and stored in memory. Refers to

the sound source in a method by which sound data is read from

memory during performance to generate the sound output. PCM

divides the sound (wave form) along the time axis and converts

each of the wave high values to digital data. The data that results

from this operation is called PCM data.

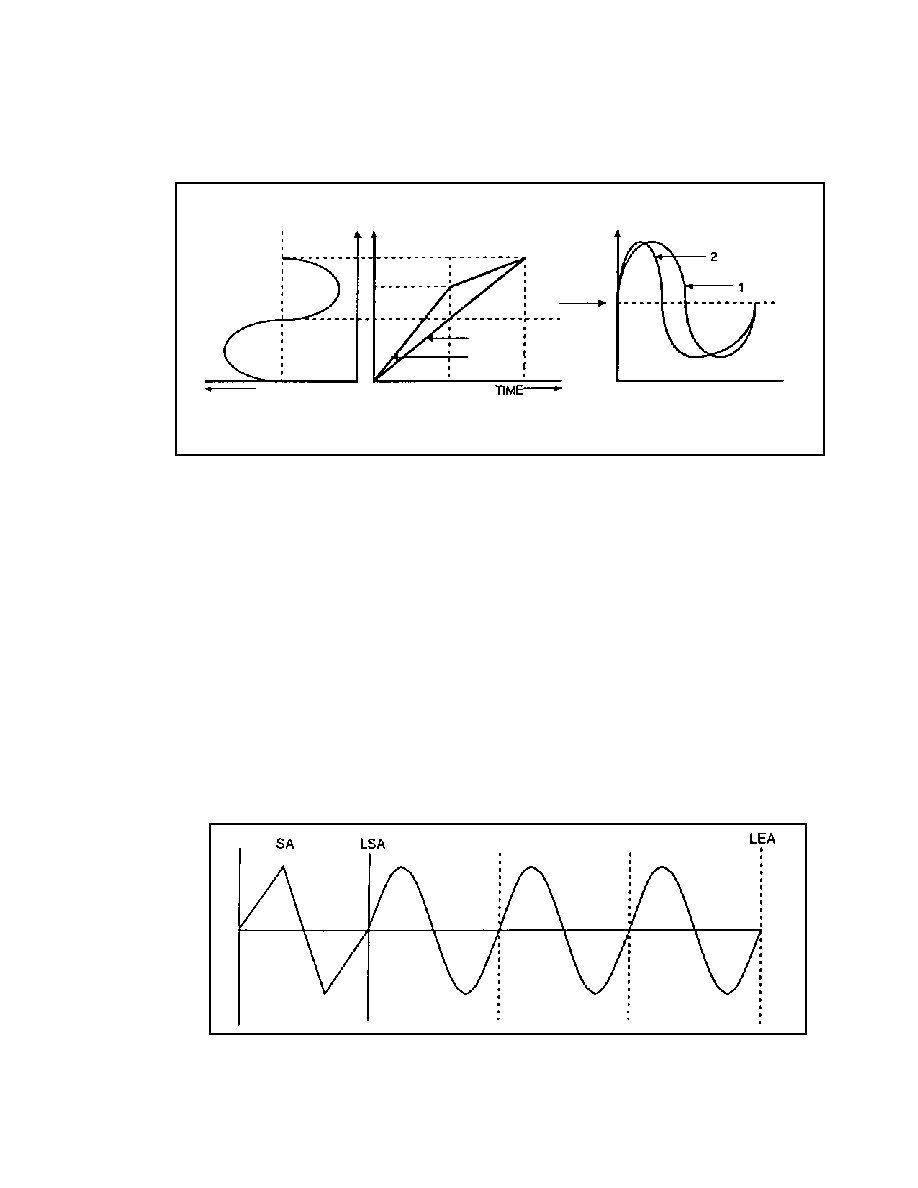

FM (Frequency Modulation)

Indicates frequency modulation. In the context of a sound genera-

tor, it indicates the FM sound generator.

i

|

SEGA Confidential

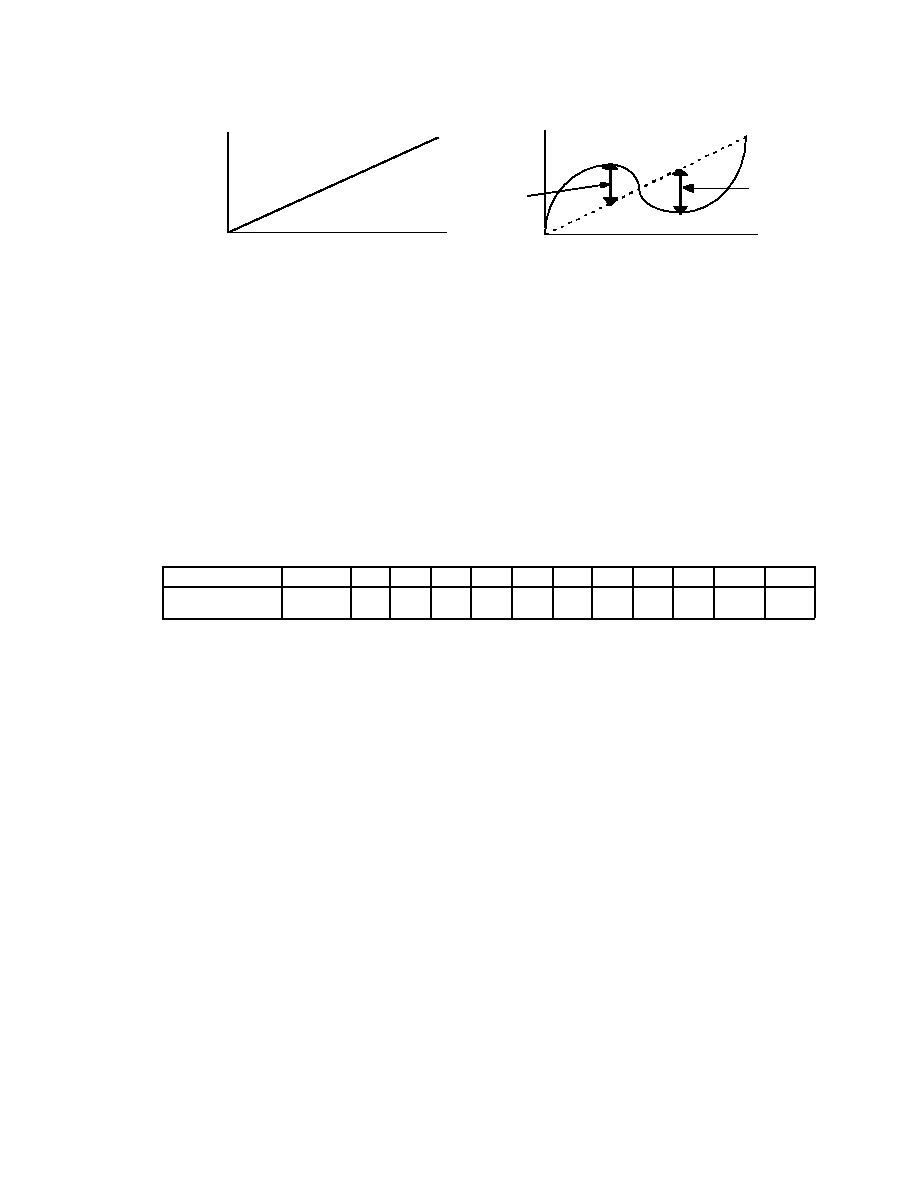

Linear

Shows a straight line. This means that the relation of the input and

output are proportional. Therefore, if the wave form data is linear,

a high wave value proportional to the size of the data is produced.

In other words, the quantized step is in equal intervals.

LFO (Low Frequency Oscillator)

Indicates a functional frequency generator that generates wave

forms with frequencies that are below the range that is audible to

the human ear. The output wave form of this LFO is used for

amplitude and modulation of frequency.

DSP (Digital Signal Processor)

This is mainly for calculation (multiplication and addition) and

contains a circuit for high-speed calculations. The DSP within

SCSP is specially customized for audio editing functions and is

used when directing sound effects such as echo, reverb, chorus and

filter.

Sample Count

Indicates the data count of the wave form data.

dB (Decibel)

A unit for expressing the relative intensity of sounds by using a

logarithm to show that unit. The equation would be:

Sound Ratio [dB] = 20

·

LOG

10

N N =

Sound Volume being compared

Standard Sound Volume

Specifically, if the comparative volume is twice the standard vol-

ume (wave form amplitude). the sound comparitor would be 6

[dB]. Once would be 0 [dB], and three times would be 10 [dB] · · ·.

On the other hand, if the comparative volume is smaller than the

standard, the value [dB] would be negative (minus value). For

example, if it was 1/2 of the standard, it would be -6 [dB].

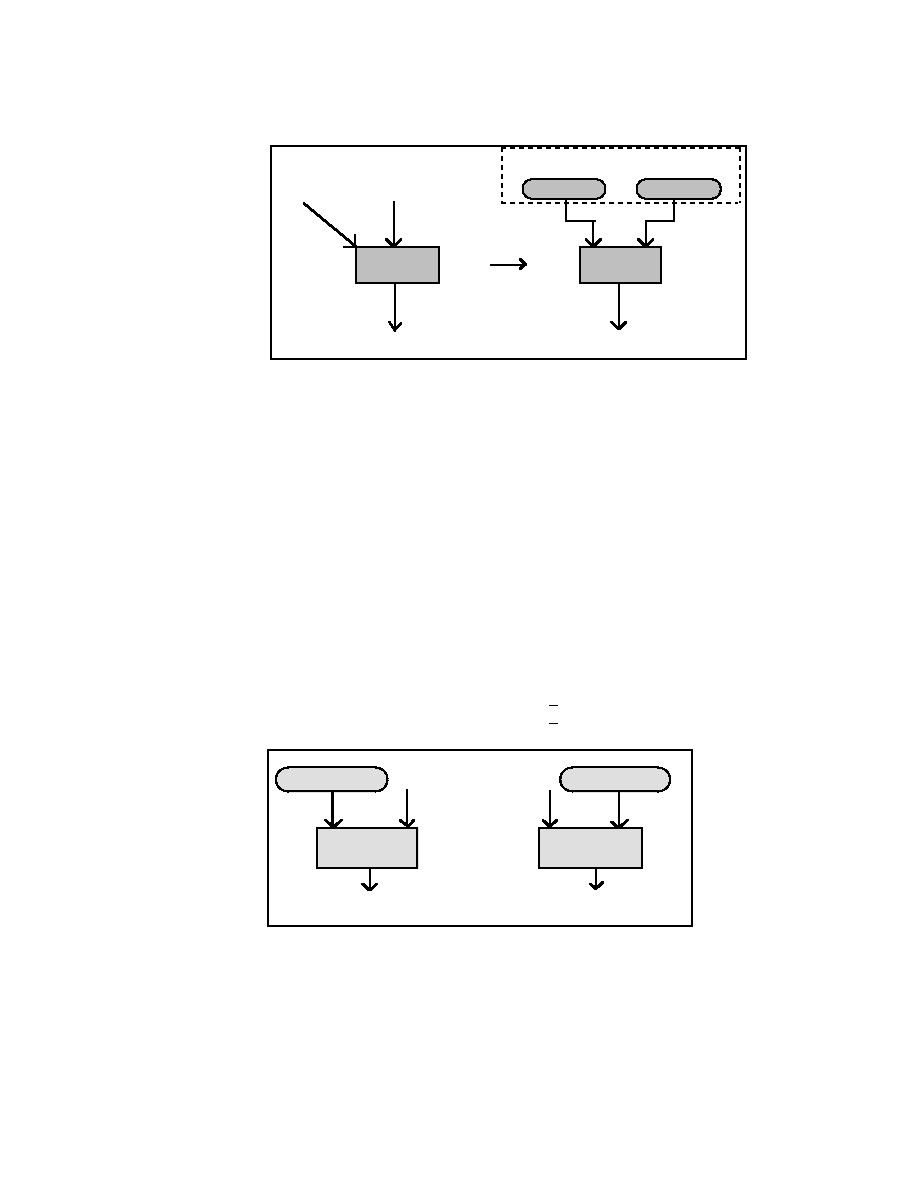

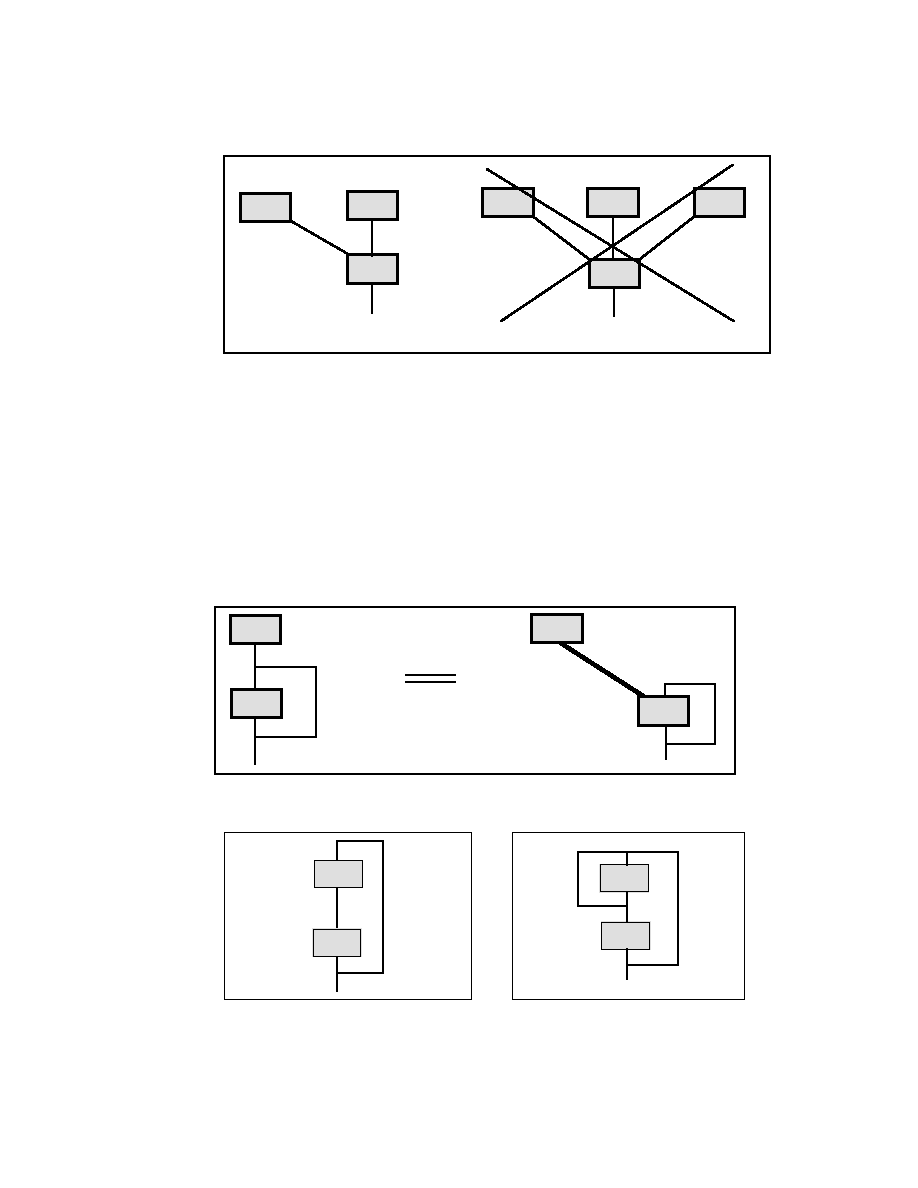

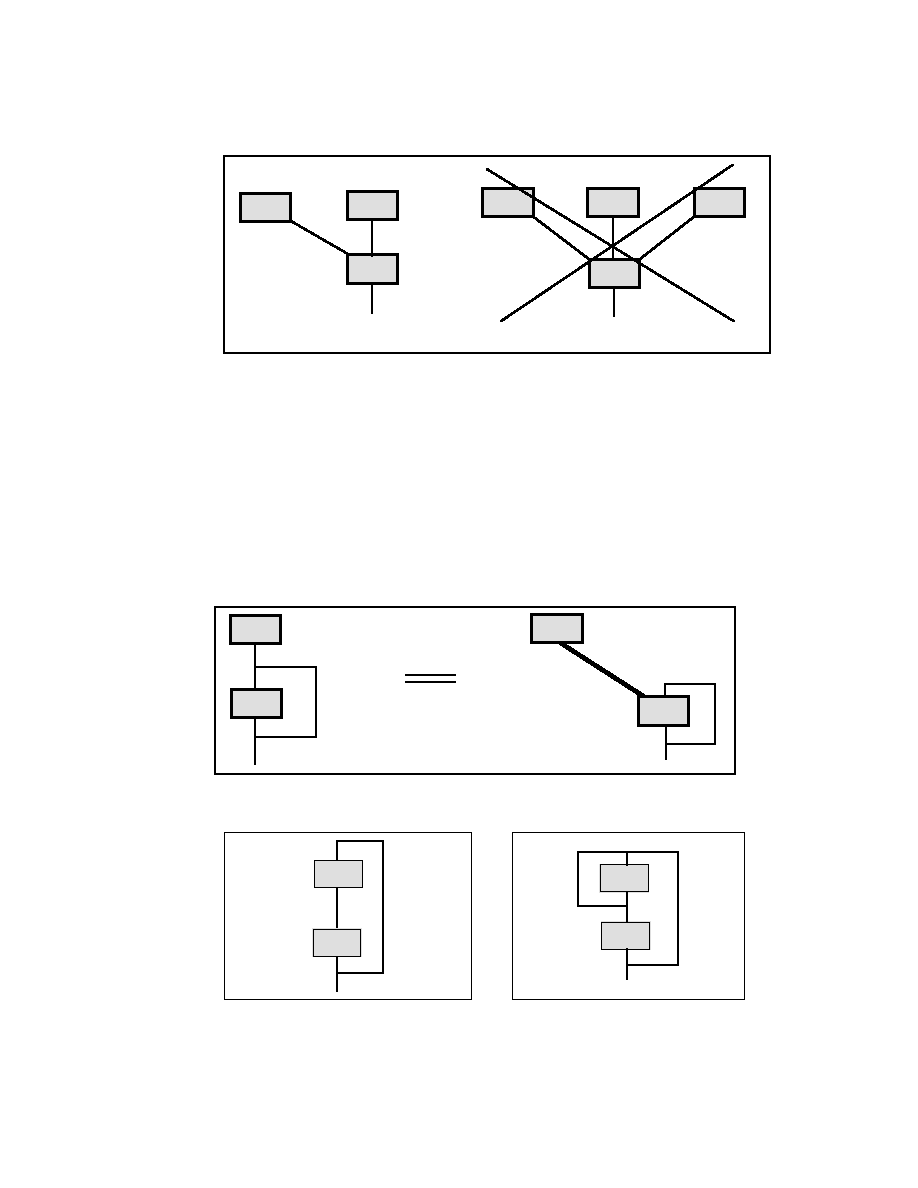

Modulator

Indicates the modulator slot when multiple slots are connected. In

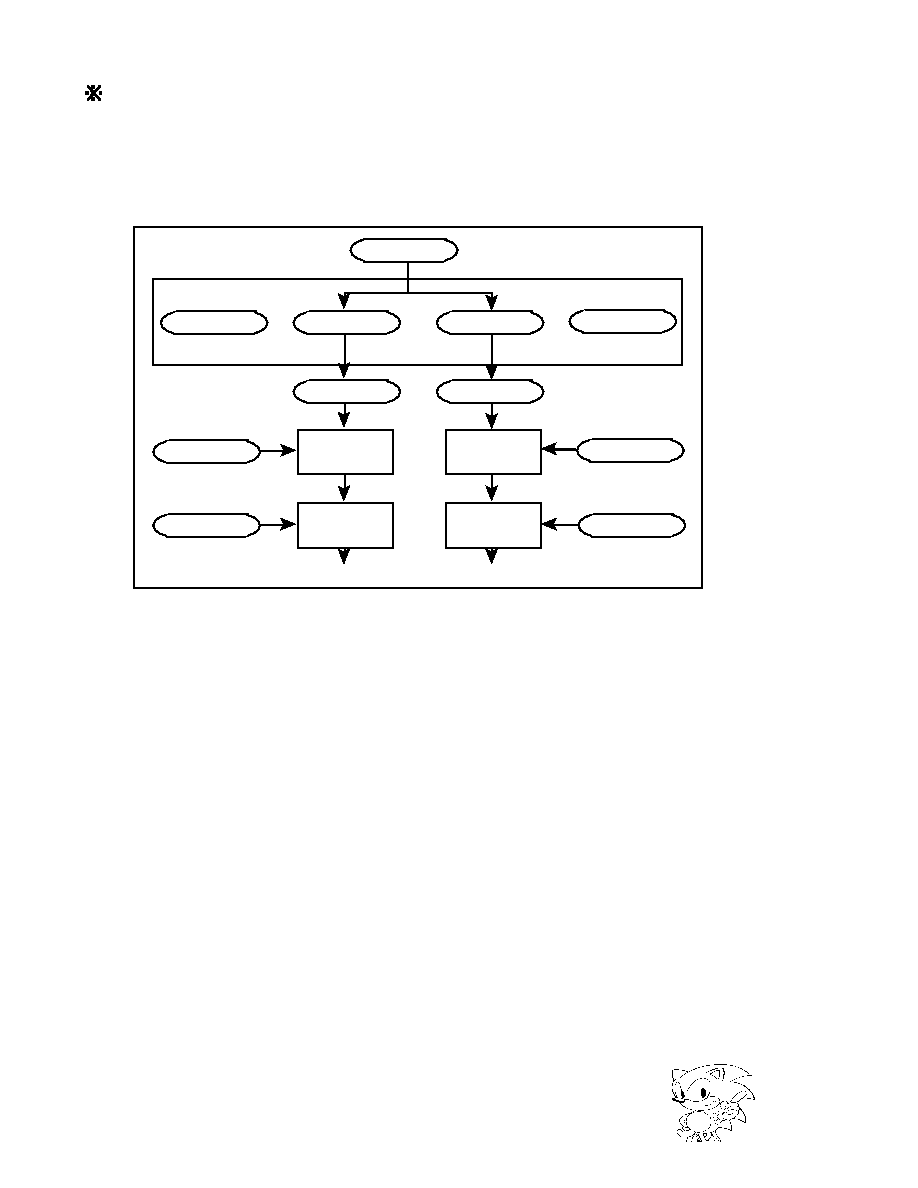

the diagram below, SLOT0 and SLOT1 are modulators.

Carrier

Indicates the slot which is modulated when multiple slots are

connected. In the diagram below, SLOT2 is the carrier.

Prescaler

This function allows required time to be set when the counter

increases one increment. Time selection and settings are done for

each timer.

ii

|

SEGA Confidential

Symbols

The following symbols are used in this manual.

Binary

Displayed with a "

B

"

at the end. For example, 100

B

. However, in

the case of 1bit, it may be shortened to just

B

.

Hexadecimal

Displayed with an "

H

"

at the end. For example, 00

H

, FF

H

.

Units

1KByte indicates 1,024 Bytes; 1Mbit indicates 1,048,576bits.

MSB, LSB

In byte and word configuration, left is the high bit (MSB, Most

Significant Bit), while right is the low bit (LSB, Least Significant

Bit).

Undefined bits

In the sound generator block register or the DSP block register, bits

that are not defined are shown with "". When writing data to

undefined bits, please write a "0

B

".

iii

|

SEGA Confidential

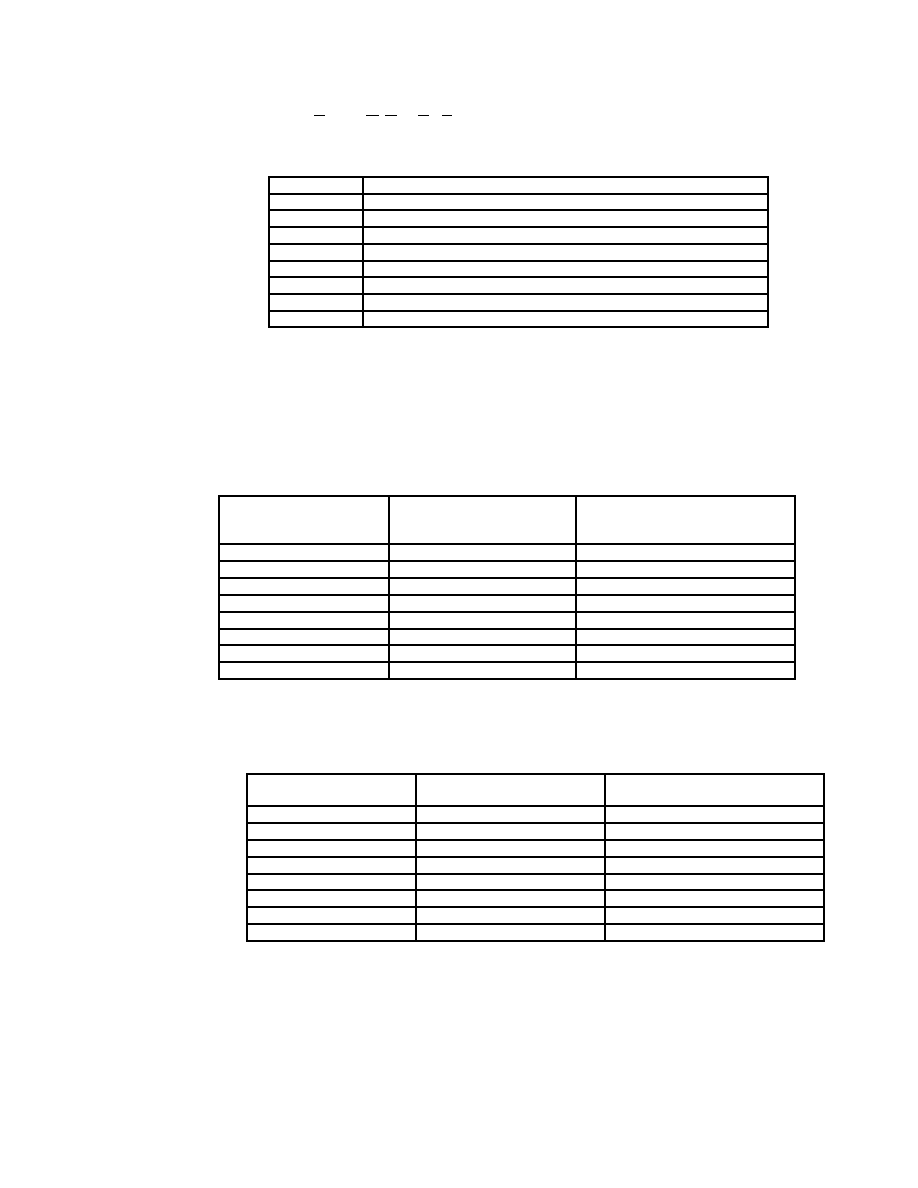

Table of Contents

Introduction

i

Definitions

i

Symbols

iii

Contents

iv

Figures

v

Tables

vii

Chapter 1 Sound System Configuration

1

1.1 System Configuration

2

Relation to the Main CPU

3

Relation to the Sound CPU

3

Sound Memory Map

3

Relation to the D/A Converter

4

Positioning of the Sound System

4

Starting Up the Sound System

5

Sound System Communication

6

Chapter 2 SCSP Overview

9

2.1 LSI Overview

10

2.2 LSI Specifications

11

2.3 SCSP Chip Block Diagram

13

Chapter 3 SCSP Functions

17

3.1 Interface

18

Sound CPU Interface

18

Main CPU Interface

18

3.2 Memory Access Control

20

Chapter 4 SCSP Registers

23

4.1 Register Map

24

4.2 Sound Source Register

34

Loop Control Register

35

EG Register

40

FM Modulation Control Register

46

Using the FM Sound Generator Method

47

Volume Register

72

PITCH Register

73

LFO Register

76

MIXER Register

80

Slot Status Register

89

Sound Memory Configuration Register

89

MIDI Register

89

Timer Register

92

Interrupt Control Register

95

DMA Transfer Register

101

4.3 DSP Memory Control Register

103

Chapter 5 DSP Operation in the SCSP

105

5.1 DSP Configuration

106

5.2 DSP Internal RAM

107

iv

|

SEGA Confidential

Figures

(Chapter 1 Sound System Configuration)

Figure 1.1 Sound System and Peripherals

2

Figure 1.2 Sound System Configuration

3

Figure 1.3 Memory Map of the Sound Memory Register

4

Figure 1.4 Sound Memory Range

5

Figure 1.5 Interrupt Relations

6

(Chapter 2 SCSP Overview)

Figure 2.1 SCSP Chip Block Diagram

13

(Chapter 3 SCSP Functions)

Figure 3.1 Access Overview

18

Figure 3.2 Memory Access Priority

20

(Chapter 4 SCSP Registers)

Figure 4.1 SCSP Memory Map (1906W)

24

Figure 4.2 Individual Slot Control Register

25

Figure 4.3 SCSP Common Control Register

28

Figure 4.4 Sound Data Stack

30

Figure 4.5 DSP Control Register

31

Figure 4.6 DSP Micro Program Map

32

Figure 4.7 DSP Internal Buffer Map

33

Figure 4.8 KEY_ON and KEY_OFF Sequence

35

Figure 4.9 Block Diagram Relating to Noise Occurrence and LFO

36

Figure 4.10 Loop Types

38

Figure 4.11 Loop Wave Forms

39

Figure 4.12 KEY_OFF During Attack State Transition

40

Figure 4.13 KEY_OFF During Decay State Transition

41

Figure 4.14 Change in the Attenuation Volume

42

Figure 4.15 Transition (1) from the Attack State to Decay 1

44

Figure 4.16 Transition (2) from the Attack State to Decay 1

44

Figure 4.17 Transition (3) from the Attack State to Decay 1

45

Figure 4.18 SLOT Block Diagram

47

Figure 4.19 Wave Form Address Creation Calculation Block

48

Figure 4.20 Creating Wave Form Addresses and Reading Wave Form Data

48

Figure 4.21 Expanded Address Pointer Output Diagram

49

Figure 4.22 Frequency Address Pointer Output Value

50

Figure 4.23 Address Pointer Output Value During FM Voice Mixing (1)

50

Figure 4.24 Address Pointer Output Value During FM Voice Mixing (2)

51

Figure 4.25 Normal Loop

51

Figure 4.26 Reversal Loop

52

Figure 4.27 Alternative Loop

52

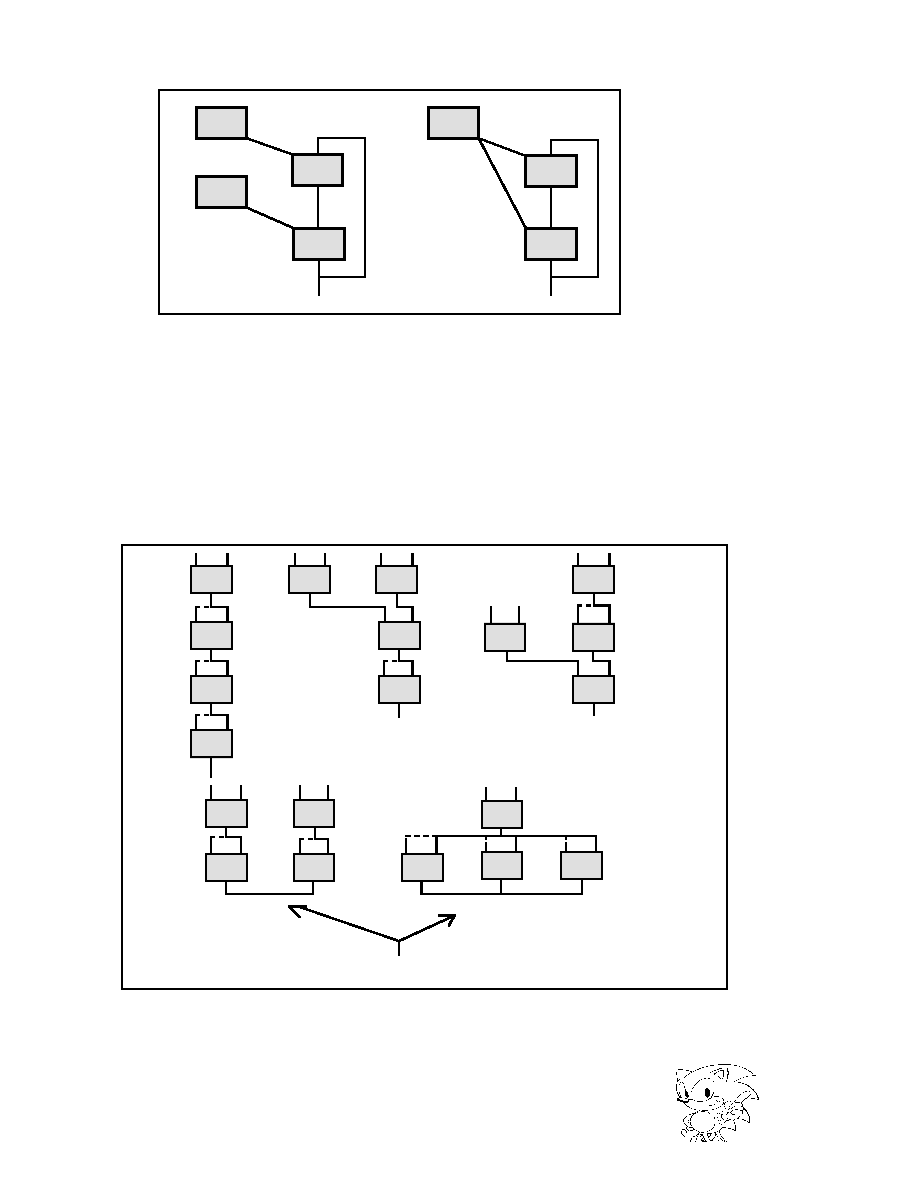

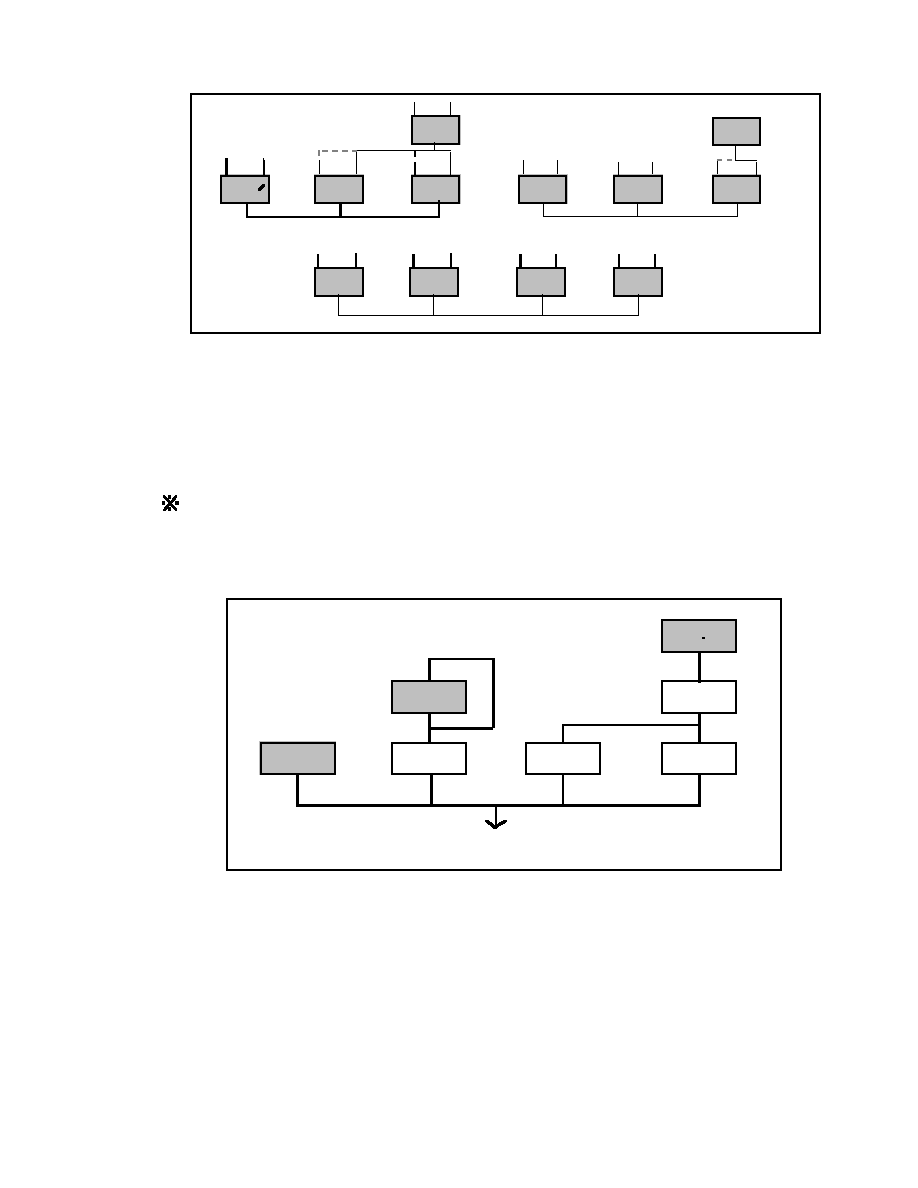

Figure 4.28 FM Sound Generator Configuration

53

Figure 4.29 Averaging Calculation Equation

54

Figure 4.30 Slot Calculation and Sound Stack Conditions

56

Figure 4.31 Time Lag until the Slot Is Written to the Sound Stack

57

Figure 4.32 Slot Averaging Calculation

58

Figure 4.33 4Slot Configuration Algorithm

59

Figure 4.34 SLOT0 Algorithm

60

Figure 4.35 SLOT2 Algorithm

61

Figure 4.36 SLOT2 Algorithm (by Input Slot)

61

Figure 4.37 SLOT3 Algorithm

62

Figure 4.38 MDL Modulation Rate

66

Figure 4.39 Maximum Displacement of the Wave Form Read Address

67

v

|

SEGA Confidential

Figure 4.40 Address Displacement during FM Voice Mixing

68

Figure 4.41 Wave Data During Clipping Process

68

Figure 4.42 Slot Connection Count

69

Figure 4.43 Self-Feedback Modulation

69

Figure 4.44 Step Feedback

69

Figure 4.45 Composite Feedback

69

Figure 4.46 Composite Modulation

70

Figure 4.47 FM Configuration Algorithm Pattern 1

70

Figure 4.48 FM Configuration Algorithm Pattern 2

71

Figure 4.49 7 SLOT FM Configuration

71

Figure 4.50 Wave Data when TL bit 4=1

72

Figure 4.51 Relation of OCT and FNS

73

Figure 4.52 LFO Block Diagram

76

Figure 4.53 Digital MIXER Block Diagram

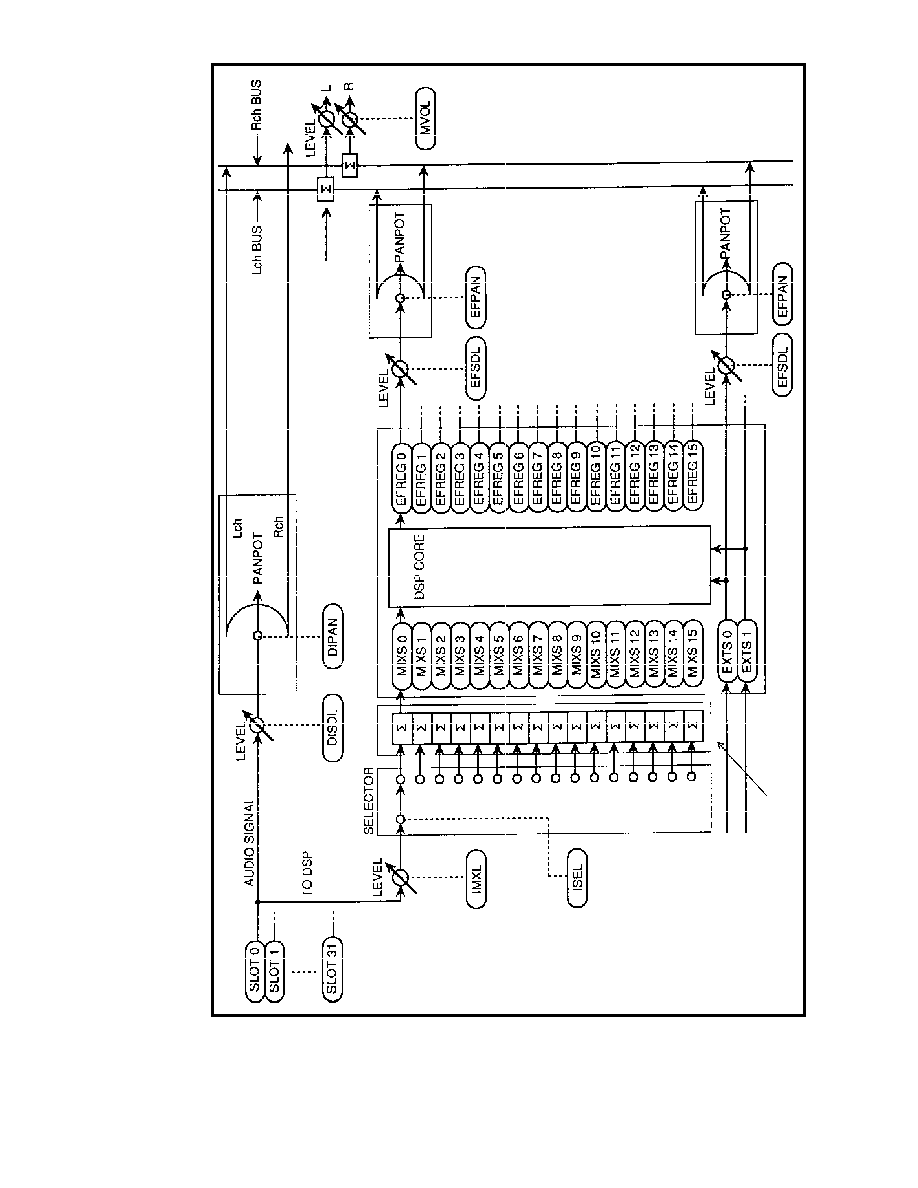

80

Figure 4.54 Direct Component and Effect Component Circuits

81

Figure 4.55 Fixed Position Calculation through the DSP

82

Figure 4.56 Digital Mixing Block Diagram

83

Figure 4.57 SCSP and DAC Connections

88

Figure 4.58 Memory Address Mapping Diagram

88

Figure 4.59 MIDI-I/F Block Diagram

90

Figure 4.60 MIDI IN Block and the Interrupt Generation Block

91

Figure 4.61 MIDI OUT Block and the Interrupt Generation Block

91

Figure 4.62 Sound Interrupt Signal Connection Diagram

95

Figure 4.63 Interrupt Register Bit Accomodation

97

Figure 4.64 3 bit Code and Register Accomodation

98

Figure 4.65 Format of the Interrupt Level Setting Register

99

Figure 4.66 DMA Controller Block Diagram

101

(Chapter 5 DSP Operation in the SCSP)

Figure 5.1 DSP Configuration Diagram

106

vi

|

SEGA Confidential

Tables

(Chapter 1 Sound System Configuration)

Table 1.1 Sound CPU Address 100400H, 100401H

5

Table 1.2 Sound CPU Interrupt Vector Table

7

(Chapter 2 SCSP Overview)

Table 2.1 Sound CPU Specifications

11

Table 2.2 SCSP LSI Specifications (1)

11

Table 2.3 SCSP LSI Specifications (2)

12

(Chapter 4 SCSP Registers)

Table 4.1 Individual Slot Control Register (1)

25

Table 4.2 Individual Slot Control Register (2)

26

Table 4.3 Individual Slot Control Register Address Map

27

Table 4.4 SCSP Common Control Register

29

Table 4.5 Sound Data Stack

30

Table 4.6 DSP Control Register

31

Table 4.7 DSP Micro Program

32

Table 4.8 DSP Internal Buffer

33

Table 4.9 Sound Generator Block Register Allocation

34

Table 4.10 KYONB Function

35

Table 4.11 SBCTL Function

36

Table 4.12 SSCTL Internal Configuration

37

Table 4.13 Types of Sound Data

37

Table 4.14 Types of Loops

38

Table 4.15 Register Set Values and the Modulation Rate

46

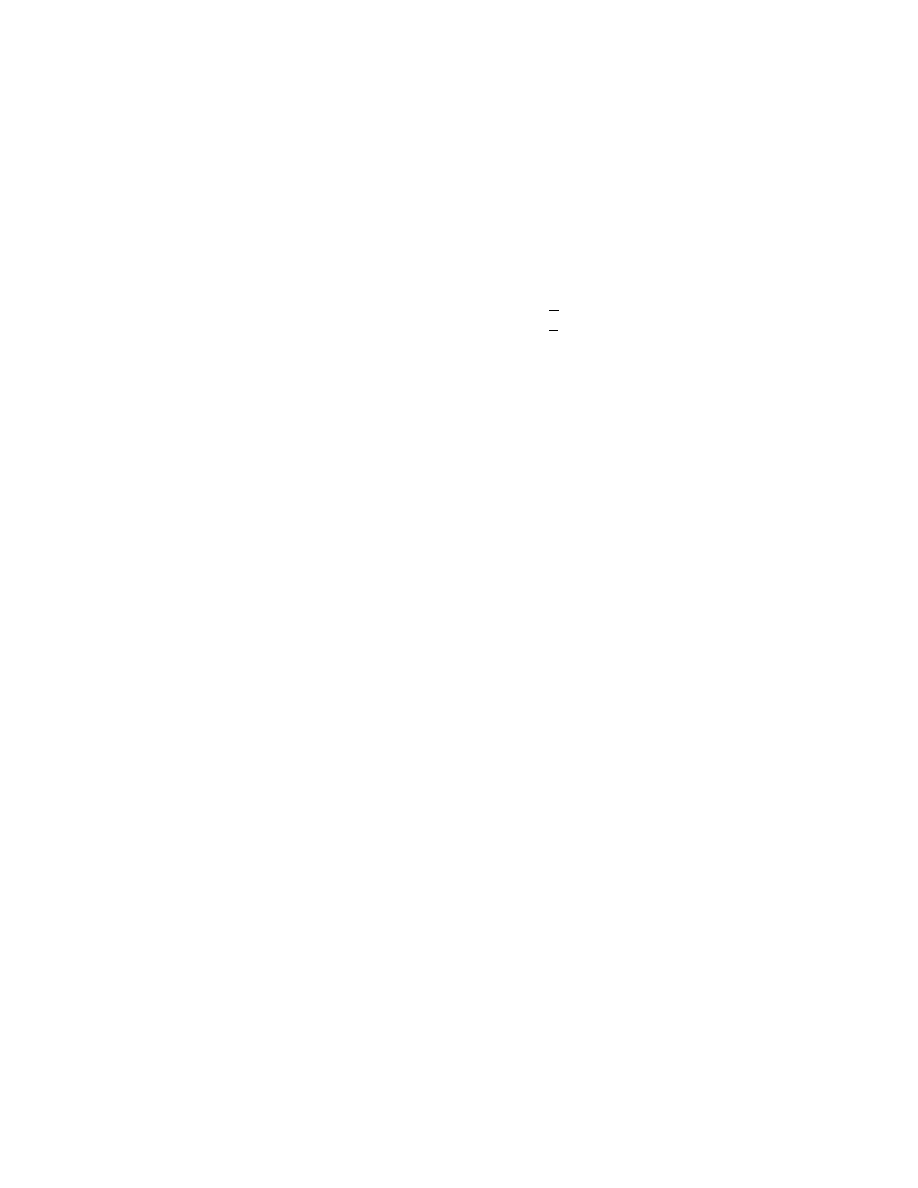

Table 4.16 Relation of MDXSL/MDYSL and SLOT

65

Table 4.17 Address Maximum Displacement Value According to the Register Setting

67

Table 4.18 TL, Attenuation, and Waveform Amplitude

72

Table 4.19 Actual Frequency in Relation to Cent Count

74

Table 4.20 FNS.OCT Parameter Table

75

Table 4.21 Oscillation Frequency of the Oscillator

77

Table 4.22 LFO AM Modulation Wave Form

78

Table 4.23 LFO PM Modulation Wave Form

78

Table 4.24 Degrees of Amplitude and Frequency Modulation

79

Table 4.25 Relation of the Sources Available to Input into "IMXL" and "MIXS"

84

Table 4.26 Mix Stack Register Input level

85

vii

|

SEGA Confidential

viii

|

SEGA Confidential

Saturn SCSP User's Manual

1

Chapter 1

Sound System Configuration

Chapter 1 Contents

1.1 System Configuration .................................. 2

Relation to the Main CPU ............................ 3

Relation to the Sound CPU ......................... 3

Sound Memory Map ....................................

3

Relation to the D/A Converter ..................... 4

Positioning of the Sound System ................ 4

Starting Up the Sound System ................... 5

Sound System Communication ................... 6

|

SEGA Confidential

2

1.1

System Configuration

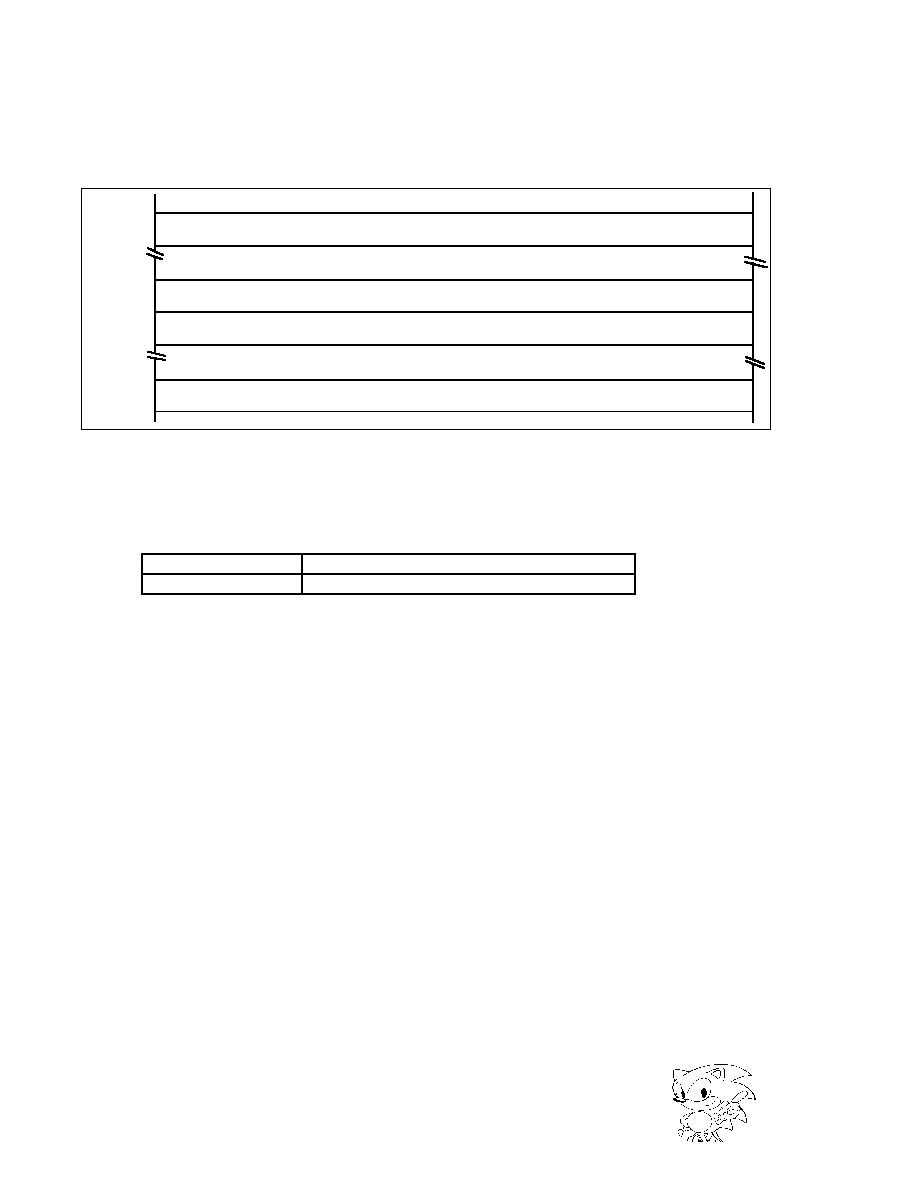

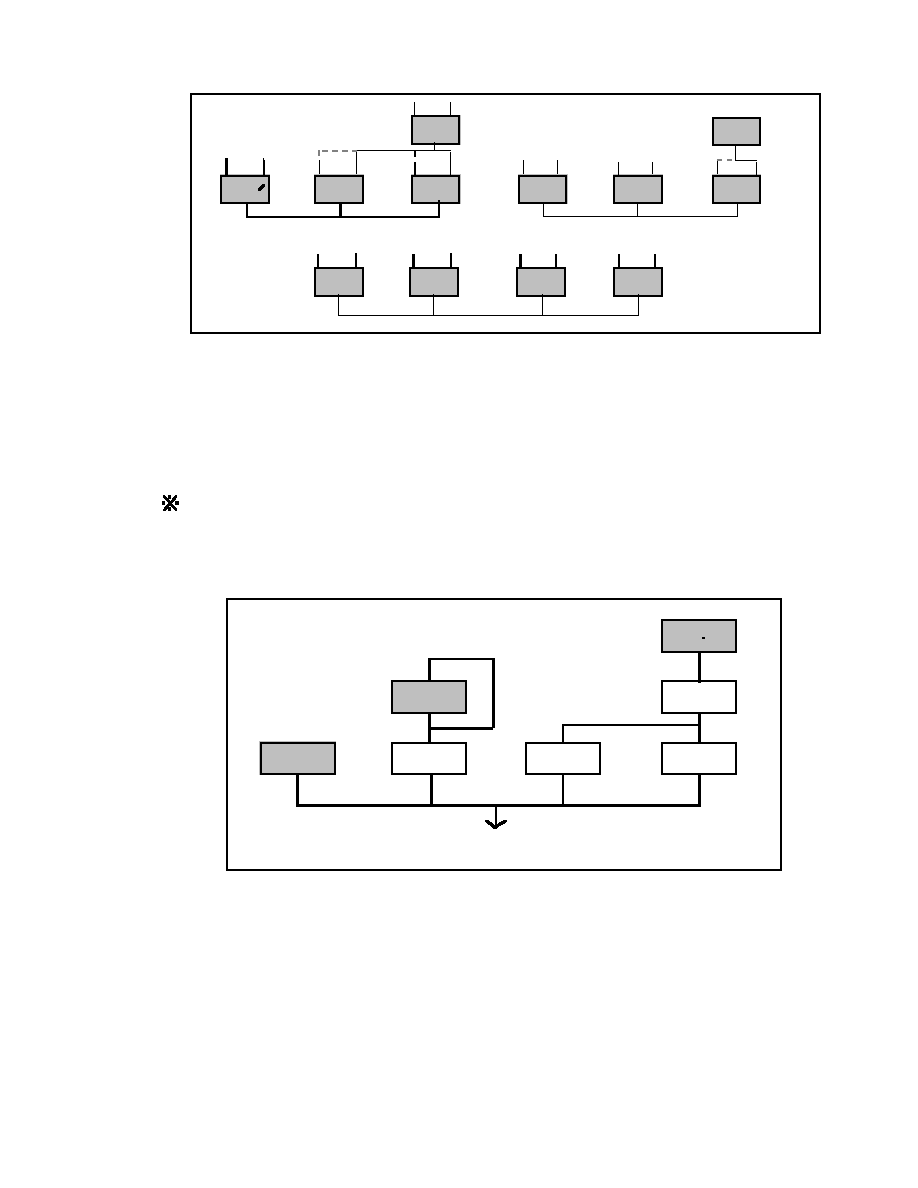

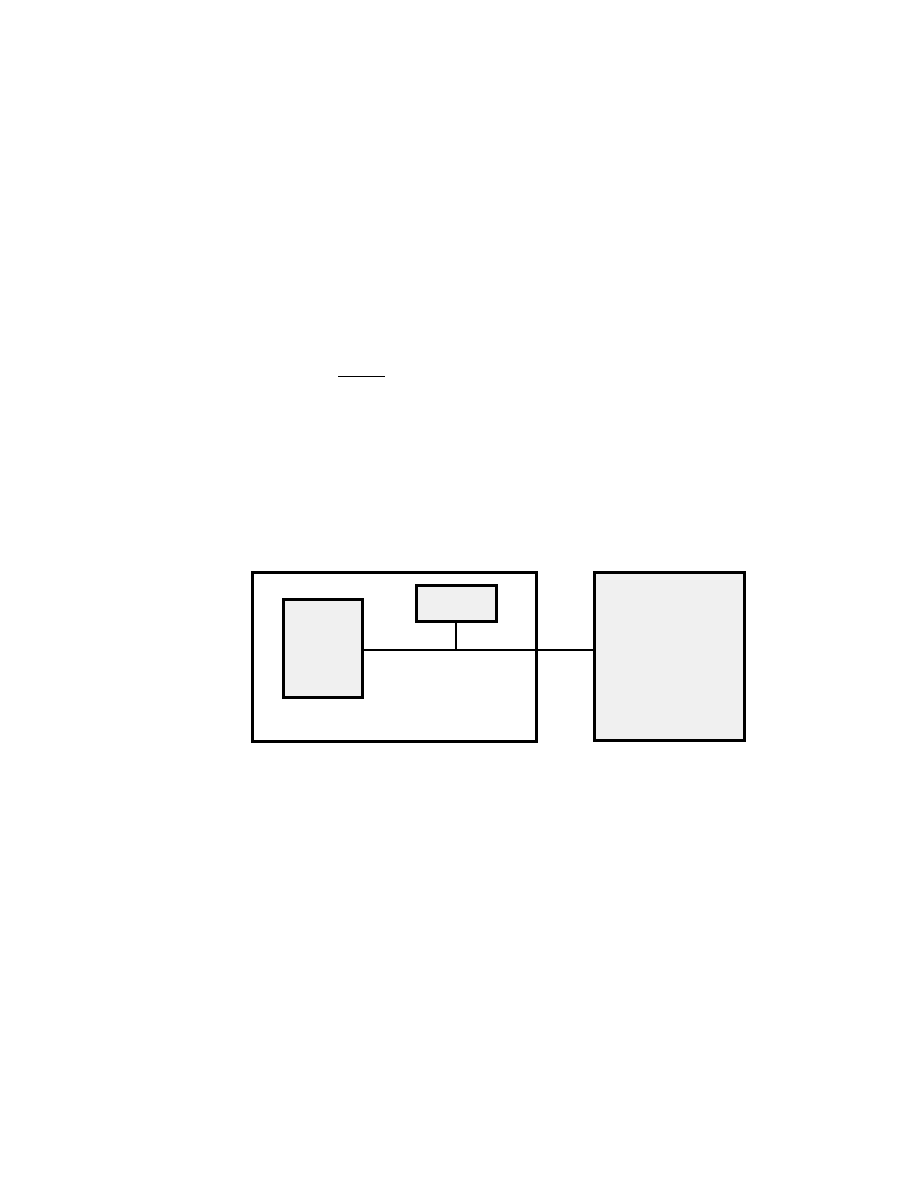

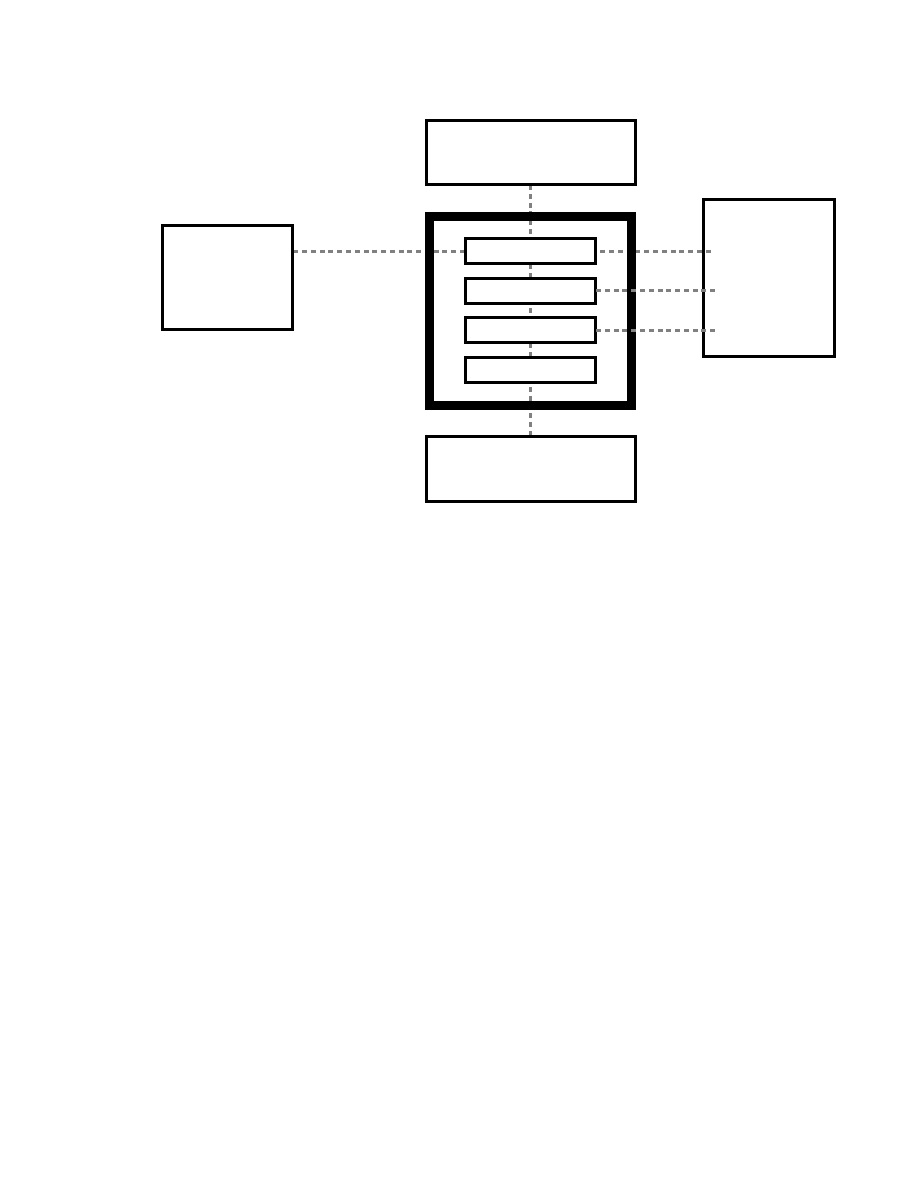

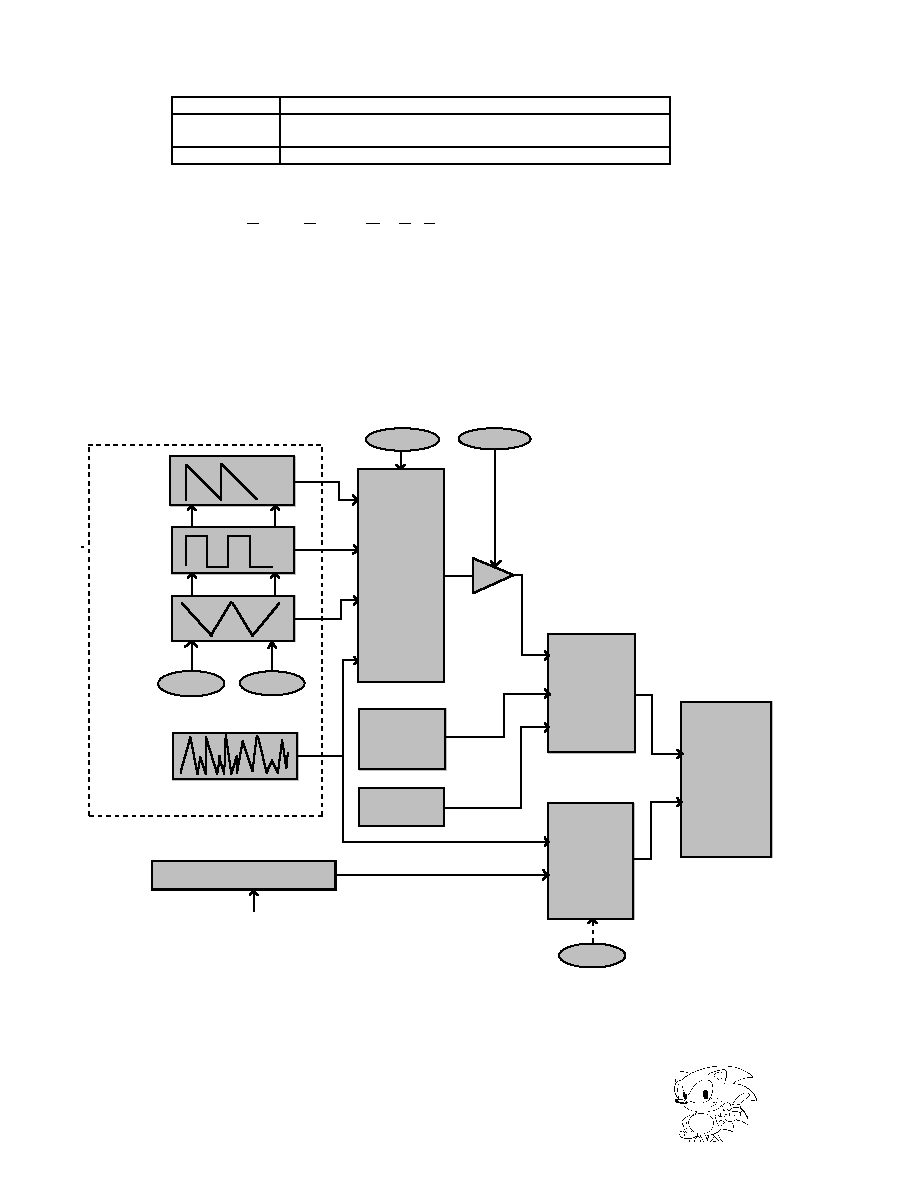

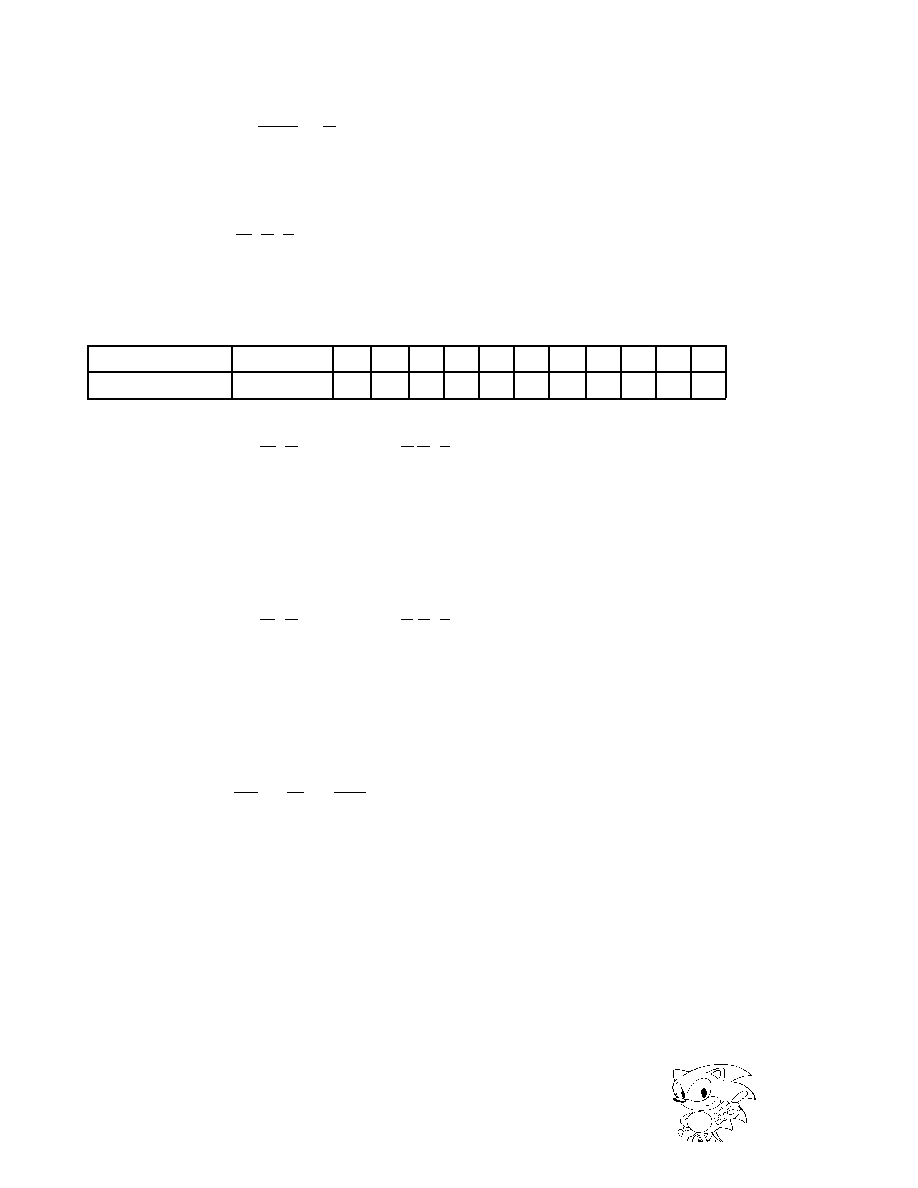

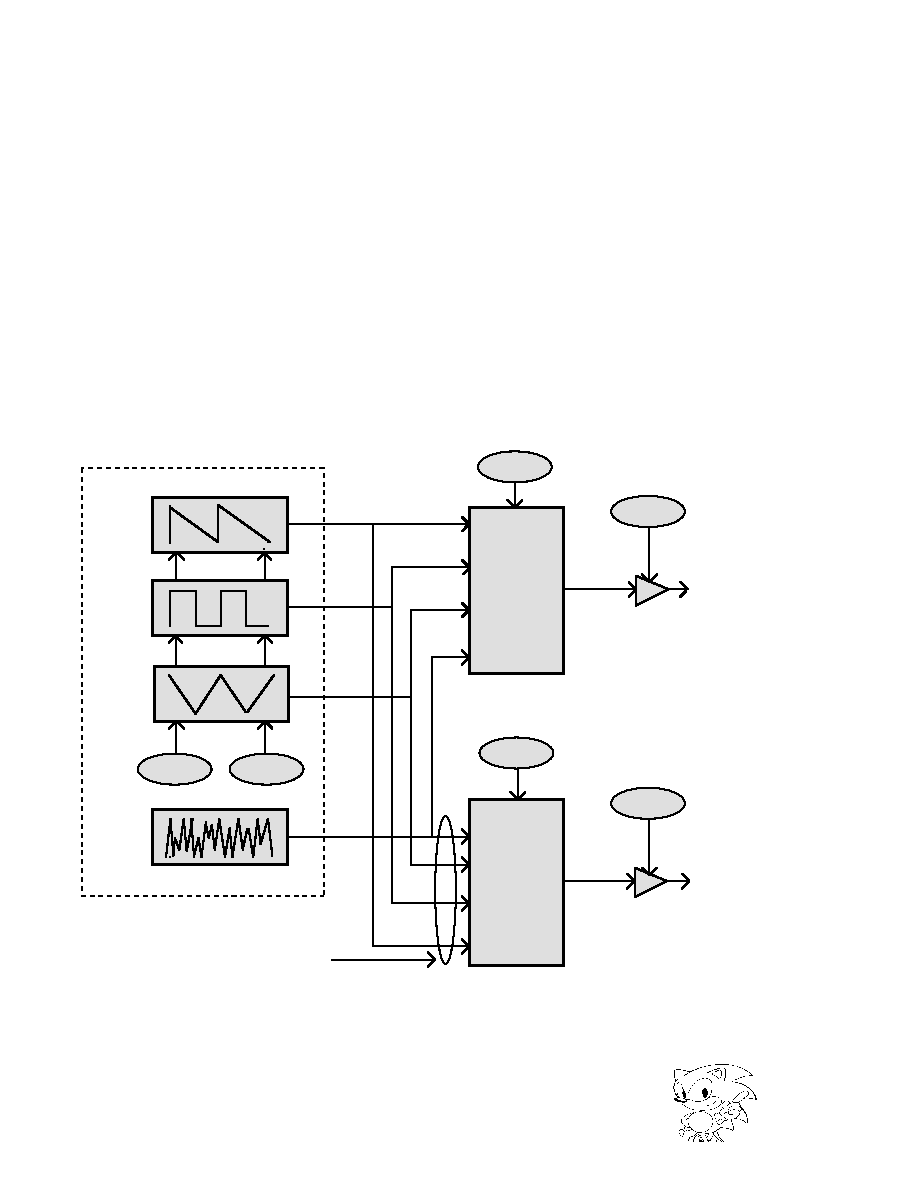

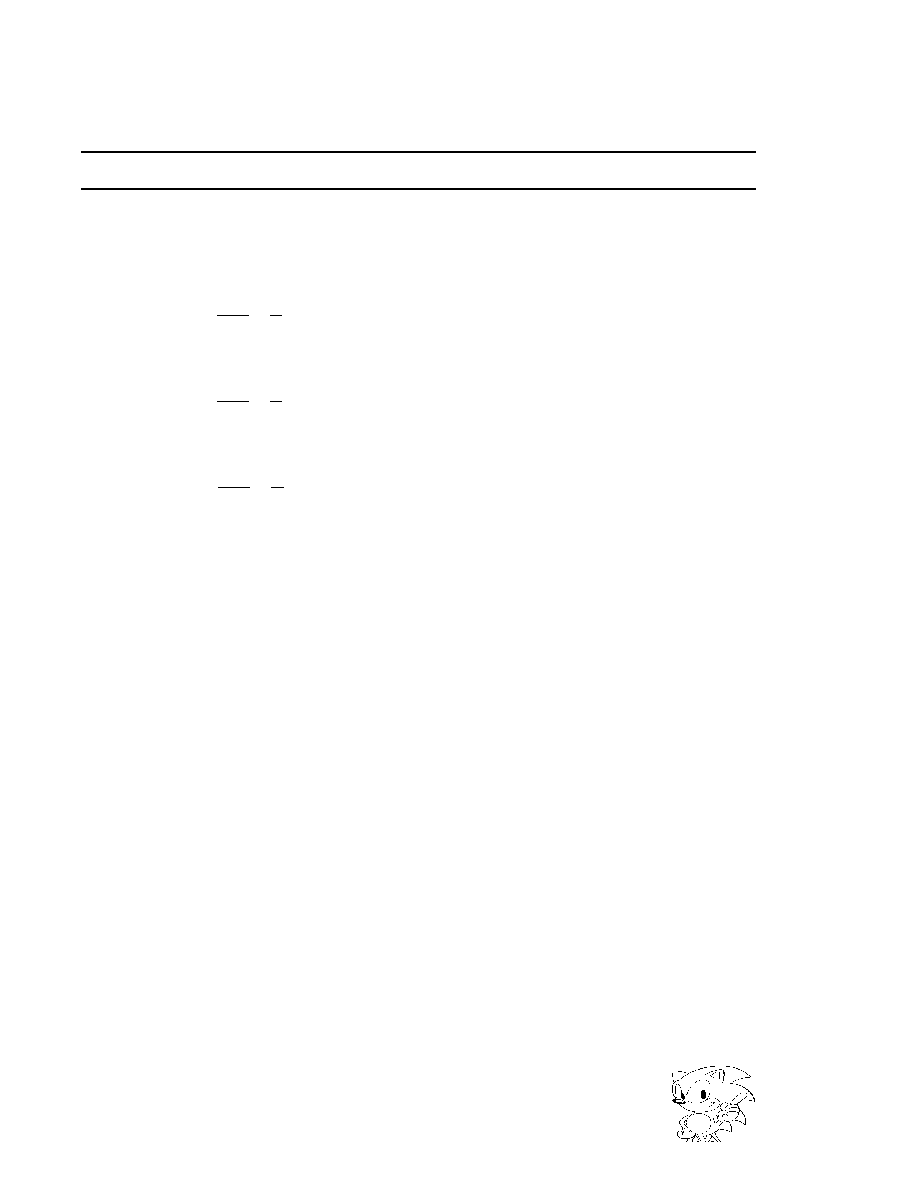

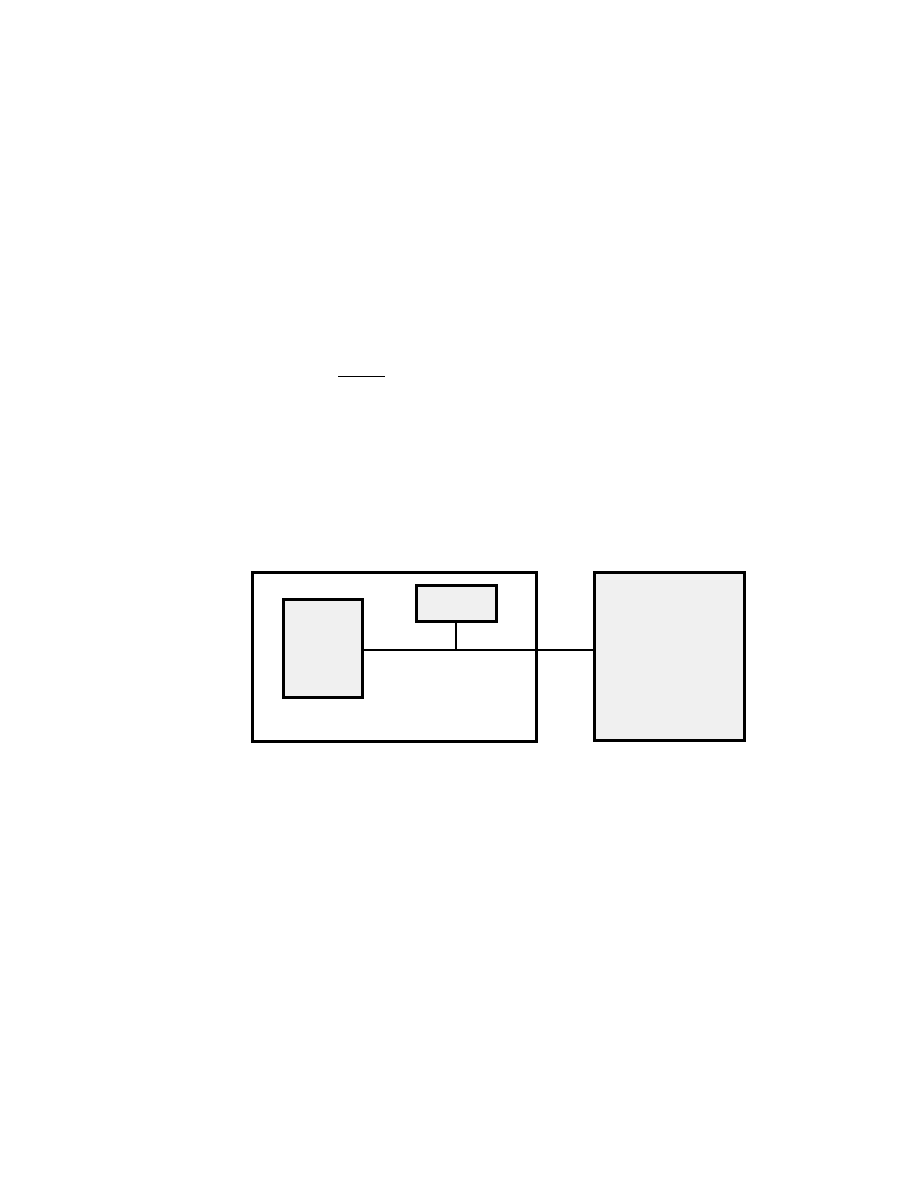

SCSP is a multi-function game sound generator LSI that consists of a PCM sound

generator and a sound DSP. Figure 1.1 shows the sound system and peripheral

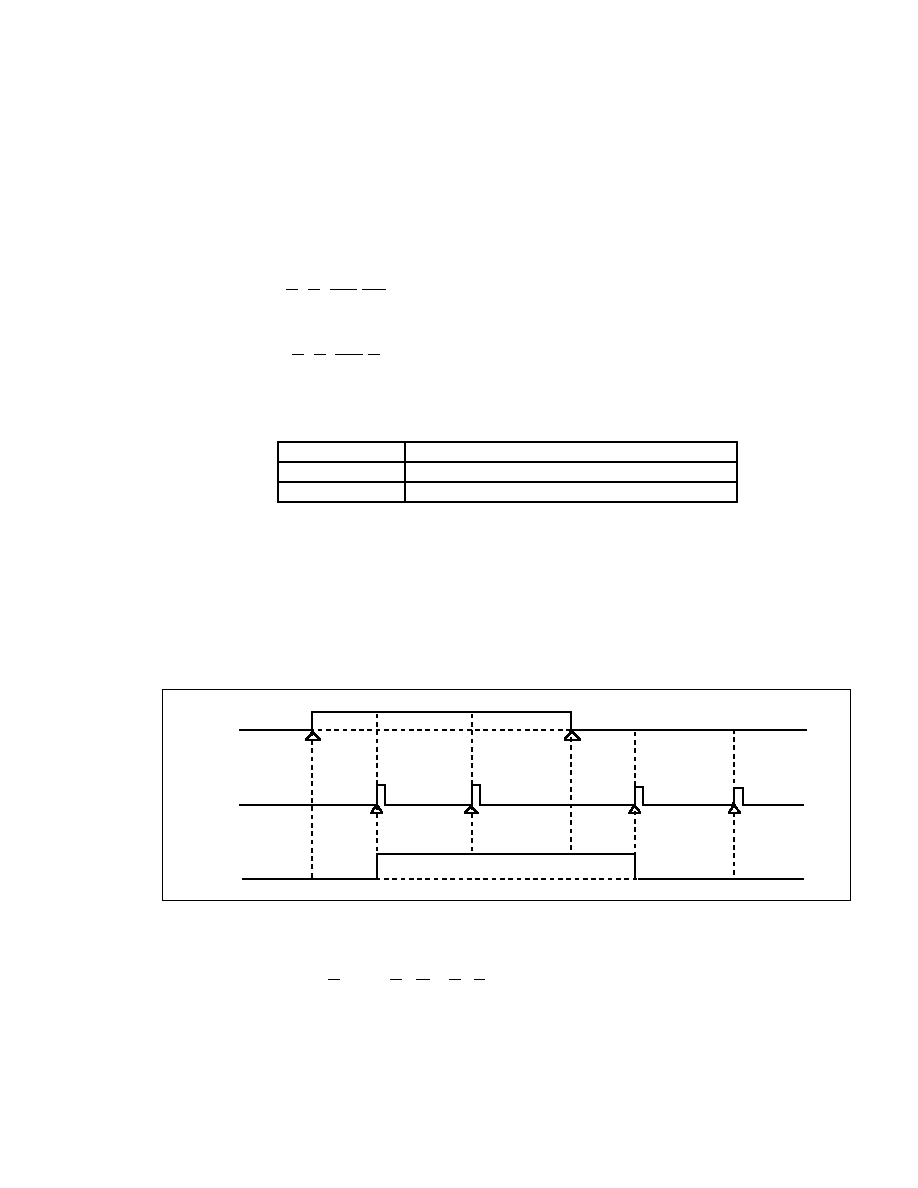

configuration. The sound processing CPU that makes up the Saturn sound block is

the MC68EC000. This CPU controls the various sound blocks.

The SCSP creates and processes sound mixes. It contains a 32 slot sound generator

and sound effect DSP, digital mixer and timer, and an interrupt controller.

The sound memory is connected directly to the SCSP. It has a capacity of 4Mbit

(512KByte) and is used to store the sound programs and data sound wave form data,

etc. This memory is accessed by the sound CPU, SCSP and the main CPU (SH-2,

SCU). Besides the memory, the SCSP is connected to the main CPU, sound CPU and

the D/A converter. The sound system can function independently of the main

system.

SH-2

SDRAM

WORK-RAM

SMPC

MC68EC000

4MbitDRAM

MASK-ROM

CD-ROM

DAC

SCSP

SCU

B-BUS

RESET

Audio Out

Rch OUTPUT

Lch OUTPUT

A-BUS

RESET

Figure 1.1 Sound System and Peripherals

|

SEGA Confidential

Saturn SCSP User's Manual

3

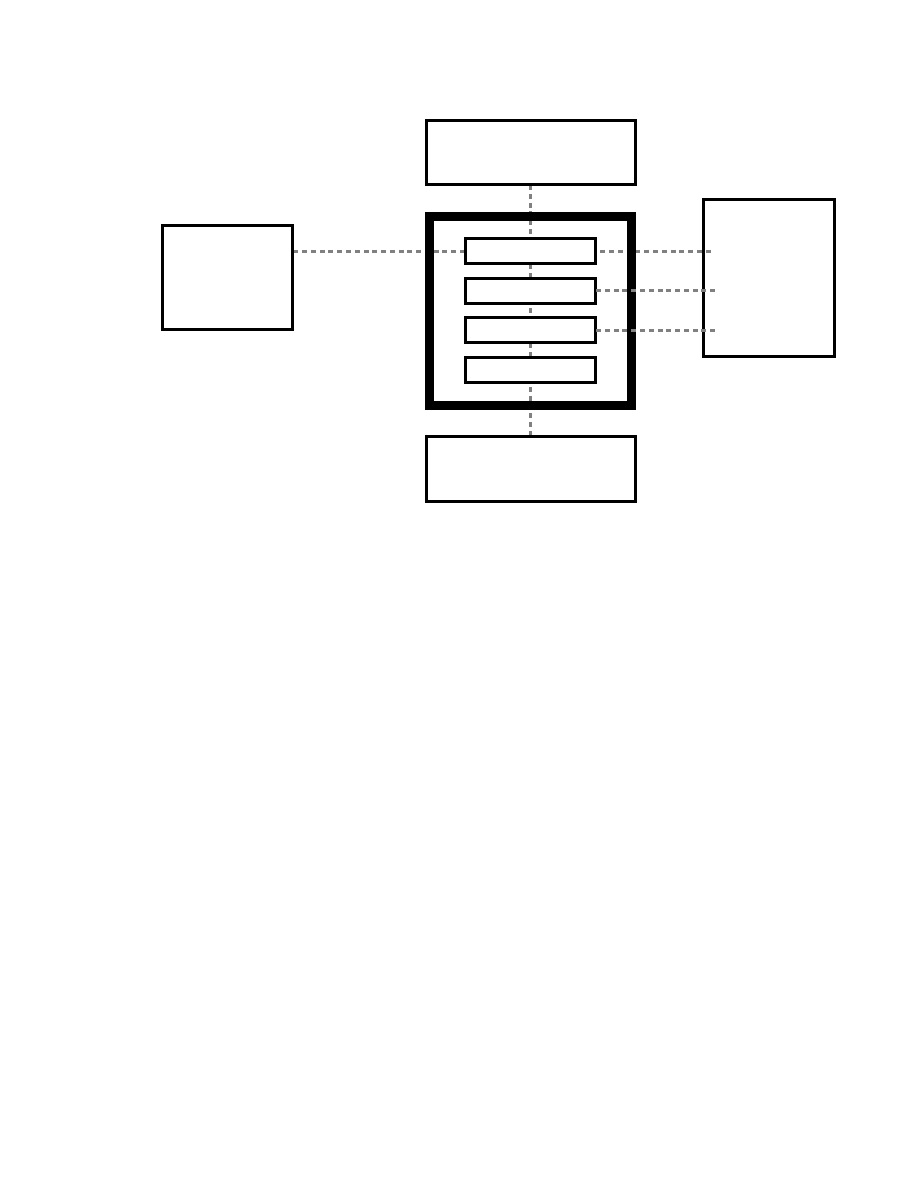

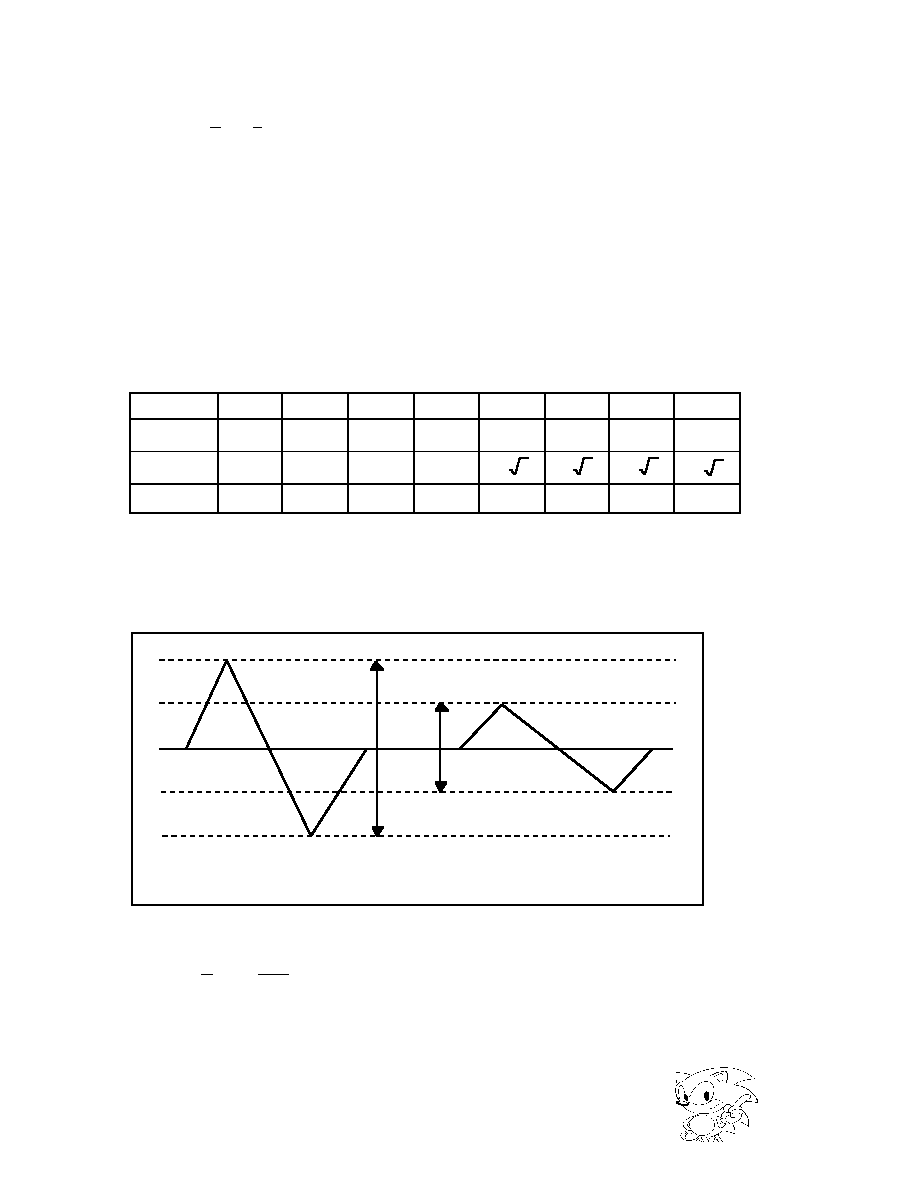

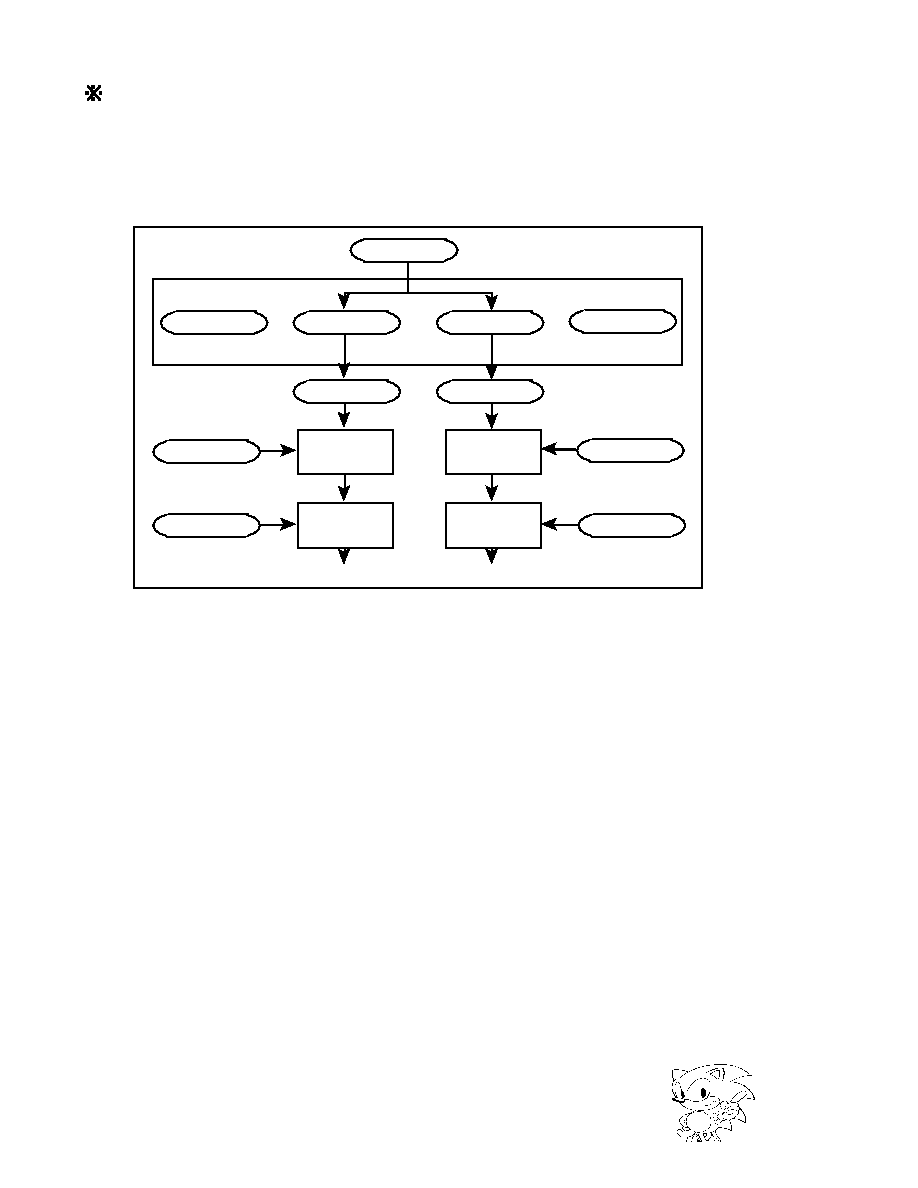

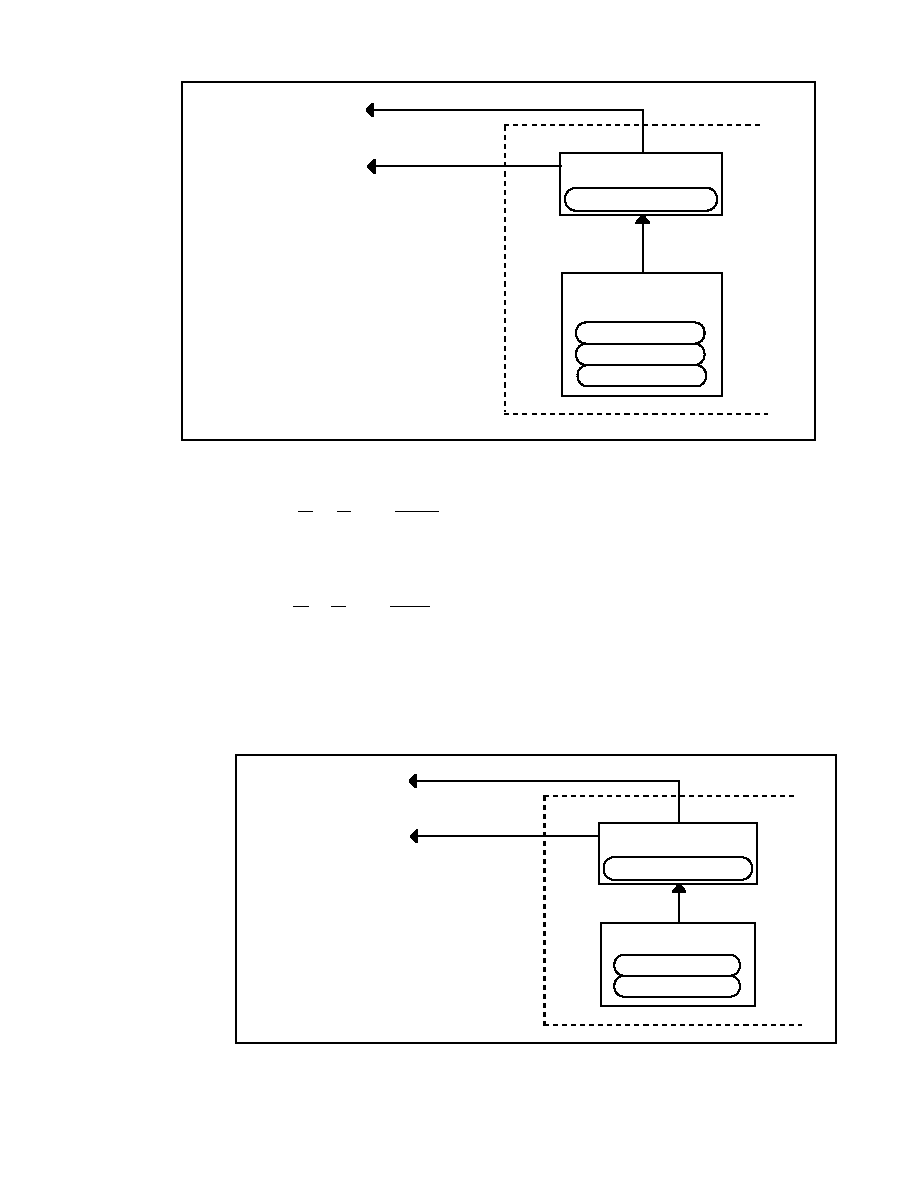

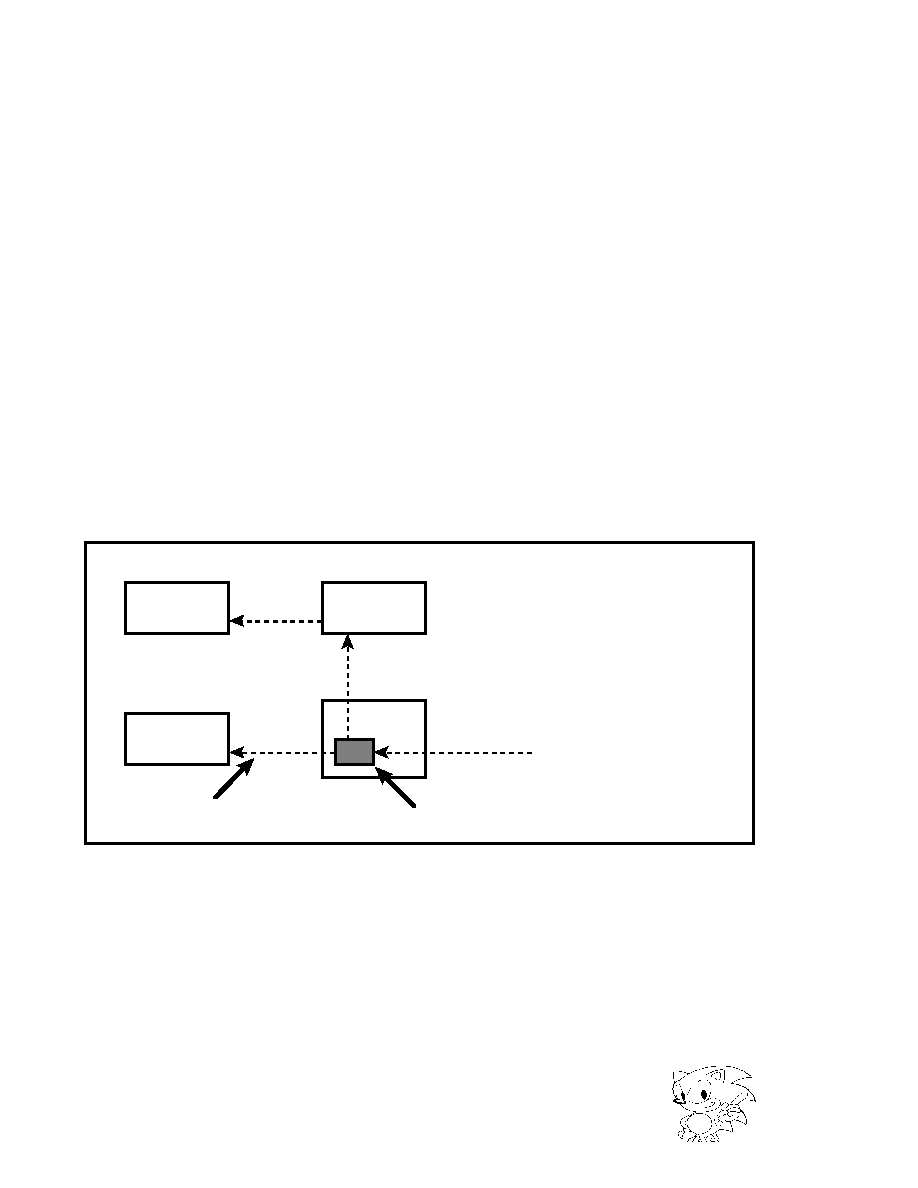

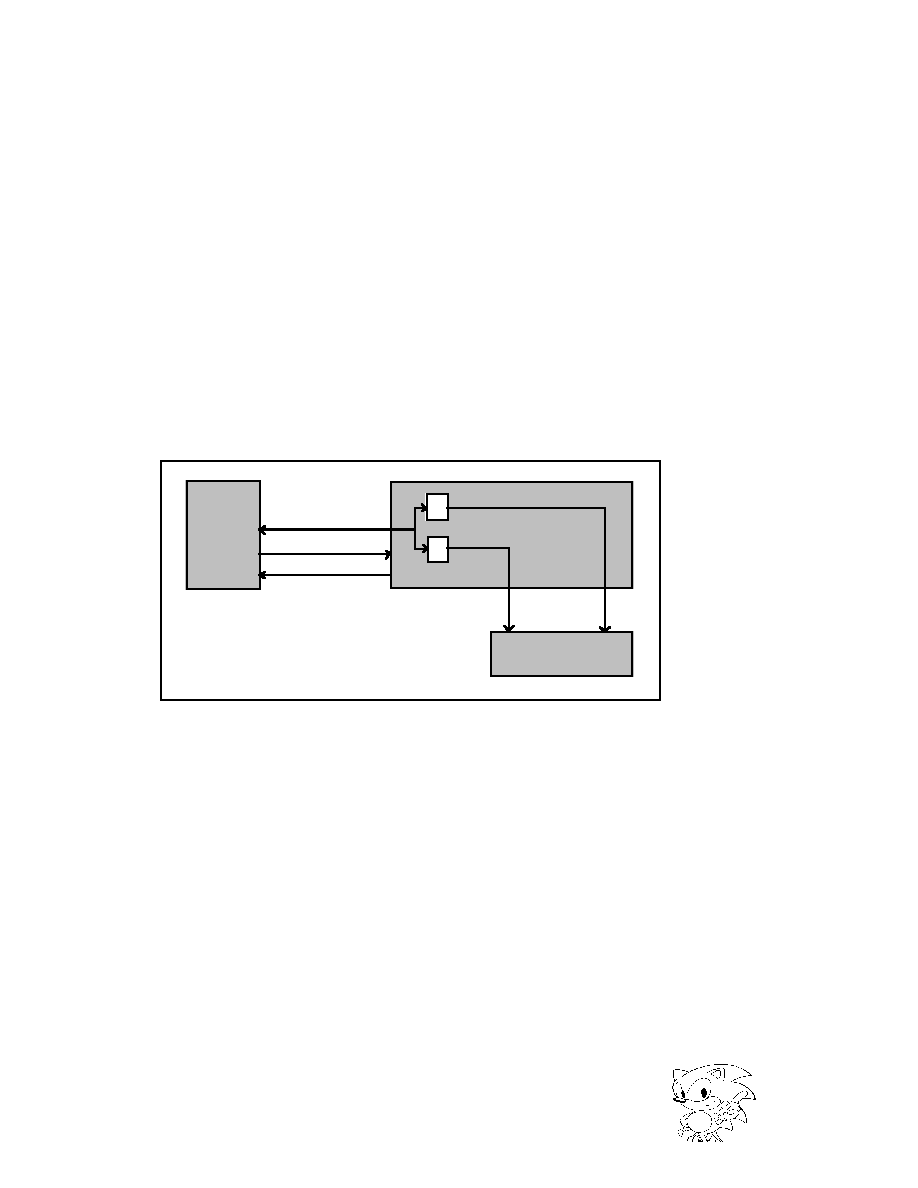

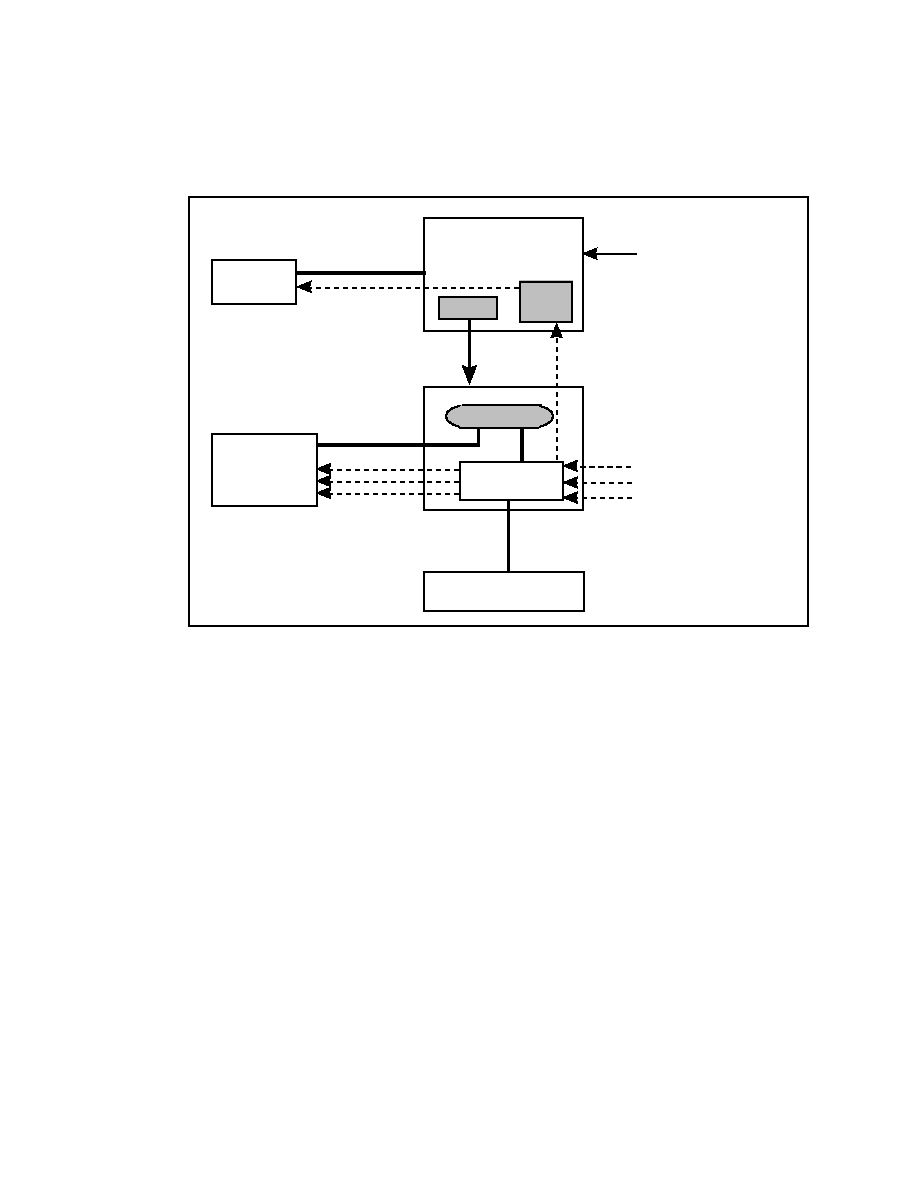

Sound CPU

Main CPU

(Game Program)

Interface

PCM (FM)

DSP

MIXER

D/A Converter

SCSP

Sound Memory

(DRAM)

SCPU Program

PCM Sound Data

DSP Delay Data

MC68EC00

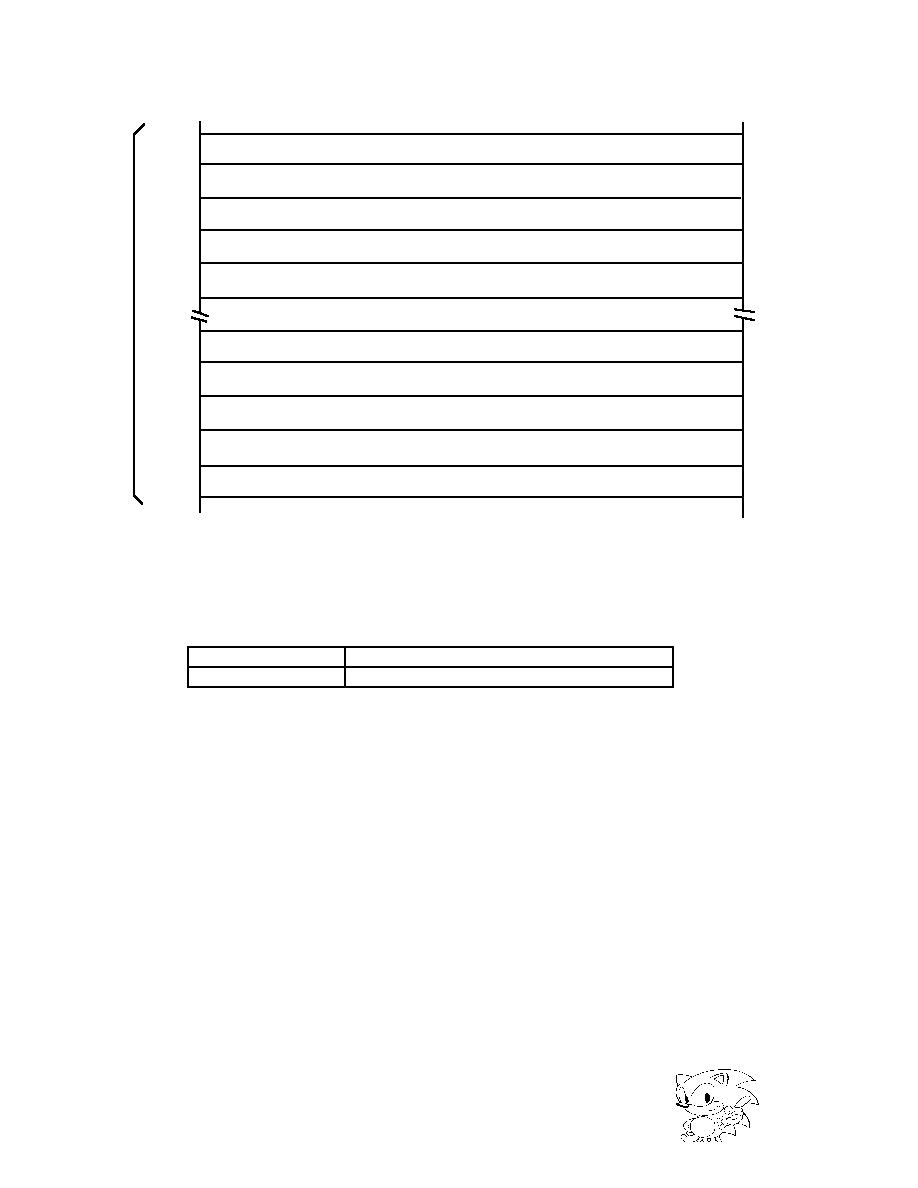

Figure 1.2 Sound System Configuration

Relation to the Main CPU

The SCSP has a main CPU interface incorporated to allow communication between

the sound system and the main system (including the main CPU). As shown in

Figure 1.2, the main system can access the memory and registers controlled by the

SCSP through the main CPU interface.

Relation to the Sound CPU

The SCSP also incorporates a dedicated sound processing CPU interface (for the

MC68EC000) to allow independent operation of the sound system against the main

system. From the SCSP's point of view, the sound CPU is like a controller.

Sound Memory Map

Saturn has 4Mbit of internal sound memory. The sound memory can be accessed by

the sound CPU, the SCSP, and the main CPU (SH-2, SCU). Similarly, the SCSP

control register that controls the SCSP sound source (block) and DSP control that are

used in the generation and processing of sound can also be accessed.

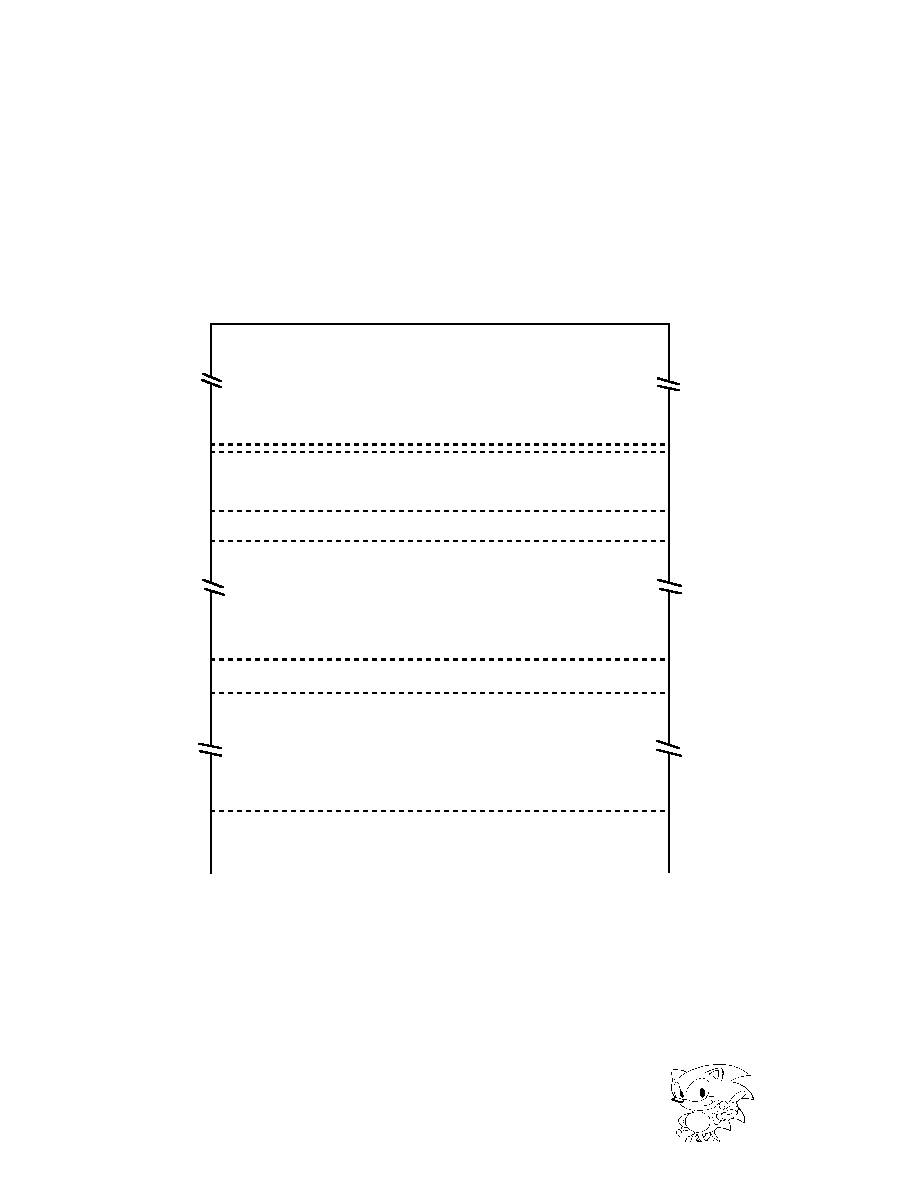

Figure 1.3 shows a sound memory map. Be aware that the memory map is refer-

enced from the sound block side, making the addresses different when accessing

from the main CPU. (See the SCU user's manual for more details.)

|

SEGA Confidential

4

Address

000000H

07FFFFH

080000H

0FFFFFH

100000H

100EE3H

Sound Memory Map

Sound Memory (RAM) Usable

Capacity : 4Mbit

Sound Memory Expansion Area

Not installed. Access is Forbidden

Control Register Area

Figure 1.3 Memory Map of the Sound Memory Register

CPU programs and data, wave form data, and DSP work area (DSP delay area) are

stored in the sound memory.

Relation to the D/A Converter

The D/A converter converts and outputs the digital sound signal created by the

SCSP to analog sound signal.

Positioning of the Sound System

The sound system (sound CPU, SCSP), based on the sound memory, can operate

independently from the main system (main CPU, video system, etc.) During this

time, the sound system operates on a RAM base and so it must get the programs and

data required for the sound CPU from the main system. Furthermore, since syn-

chronization between the image and sound is required, an interface for two-way

communication is also required.

To facilitate this communication the SCSP has an interface for the main system

included to enable communication with the main system.

The sound CPU cannot independently read data from or write data to the main

system. Information exchange between the main system and the sound system is

accomplished by the main system reading data from or writing data to the sound

memory (RAM).

|

SEGA Confidential

Saturn SCSP User's Manual

5

Starting Up the Sound System

After the sound system power is turned on, it is reset by the SMPC. In this state,

neither the sound CPU or SCSP will operate.

RESET

The sound system will operate after the SCSP reset has been released by the SMPC.

The SCSP will initialize the internal registers, etc. for about 30

µ

sec after the reset has

been released. For this reason, access is not allowed during the 30

µ

sec.

After the internal registers, etc., are initialized, the SCSP can be accessed by the main

CPU (SH-2, SCU). Once in this state, the sound program can be downloaded. Be-

fore downloading anything, make sure to set MEM4MB bit to 1 and DAC18B bit to 0

within the sound CPU (address) 10400H address. Once done, accessing the memory

and downloading files can be begun.

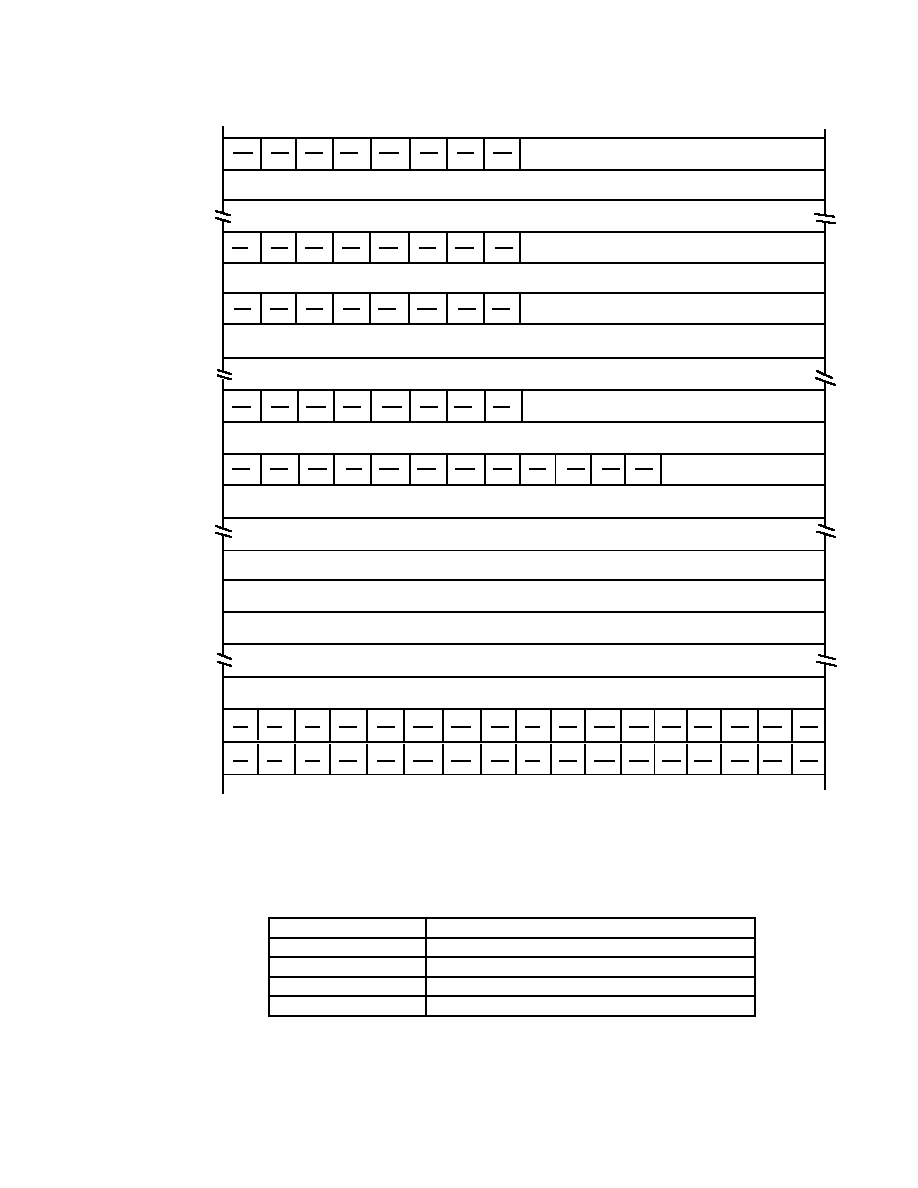

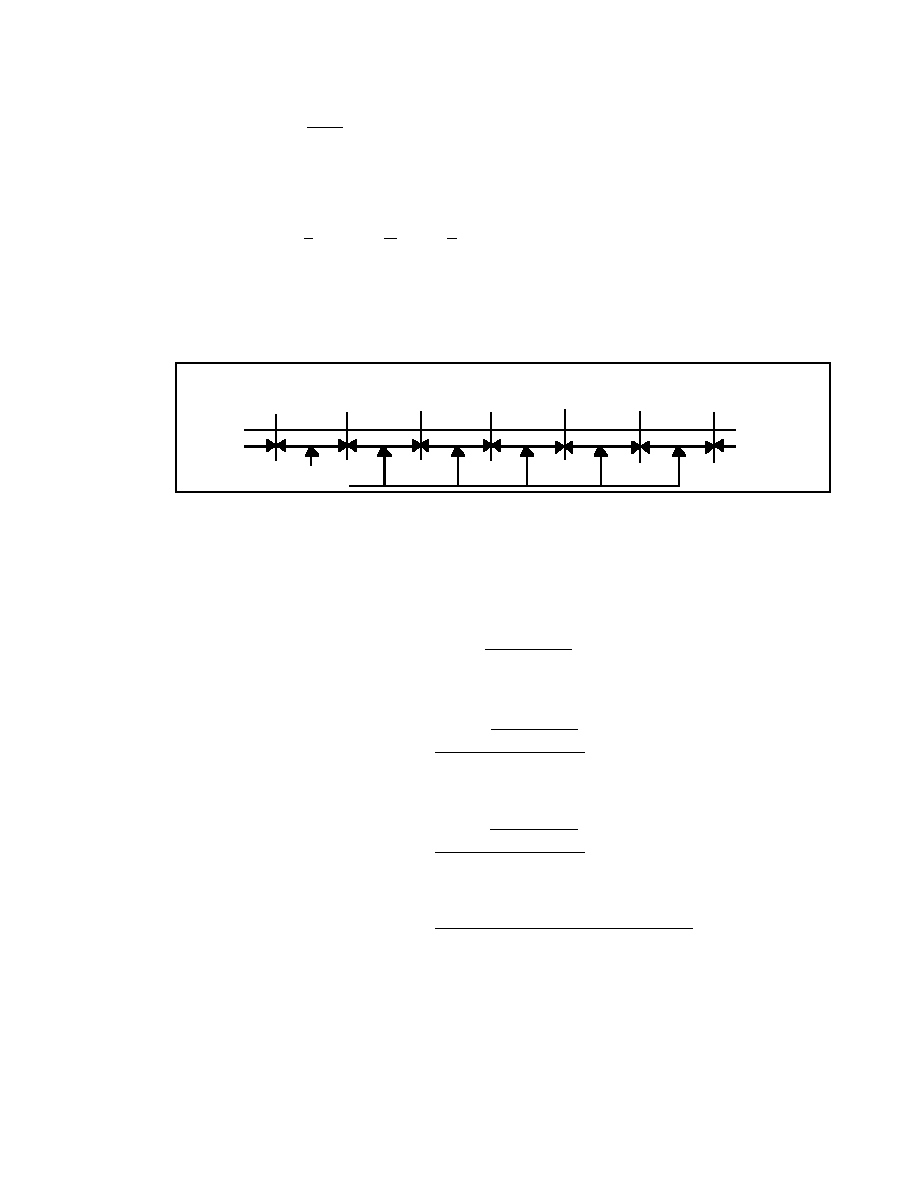

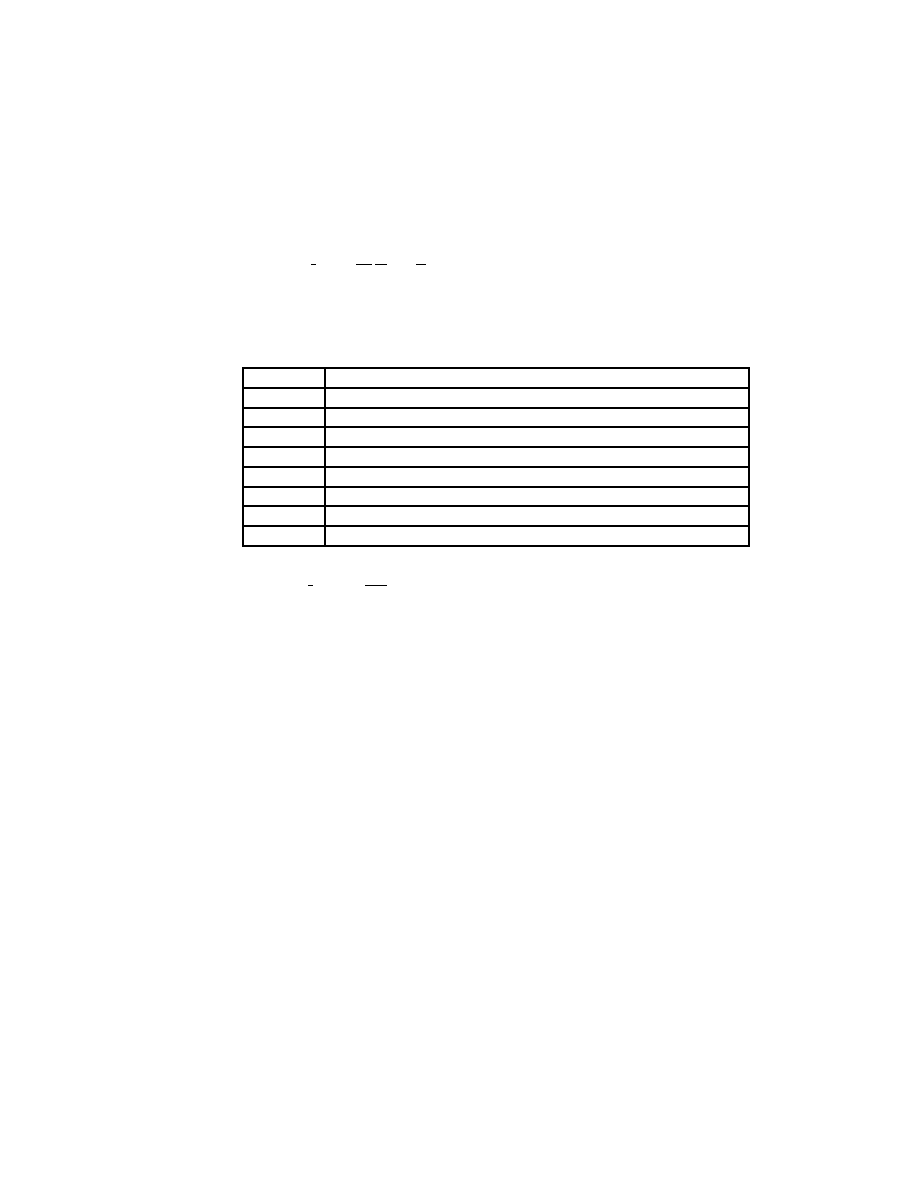

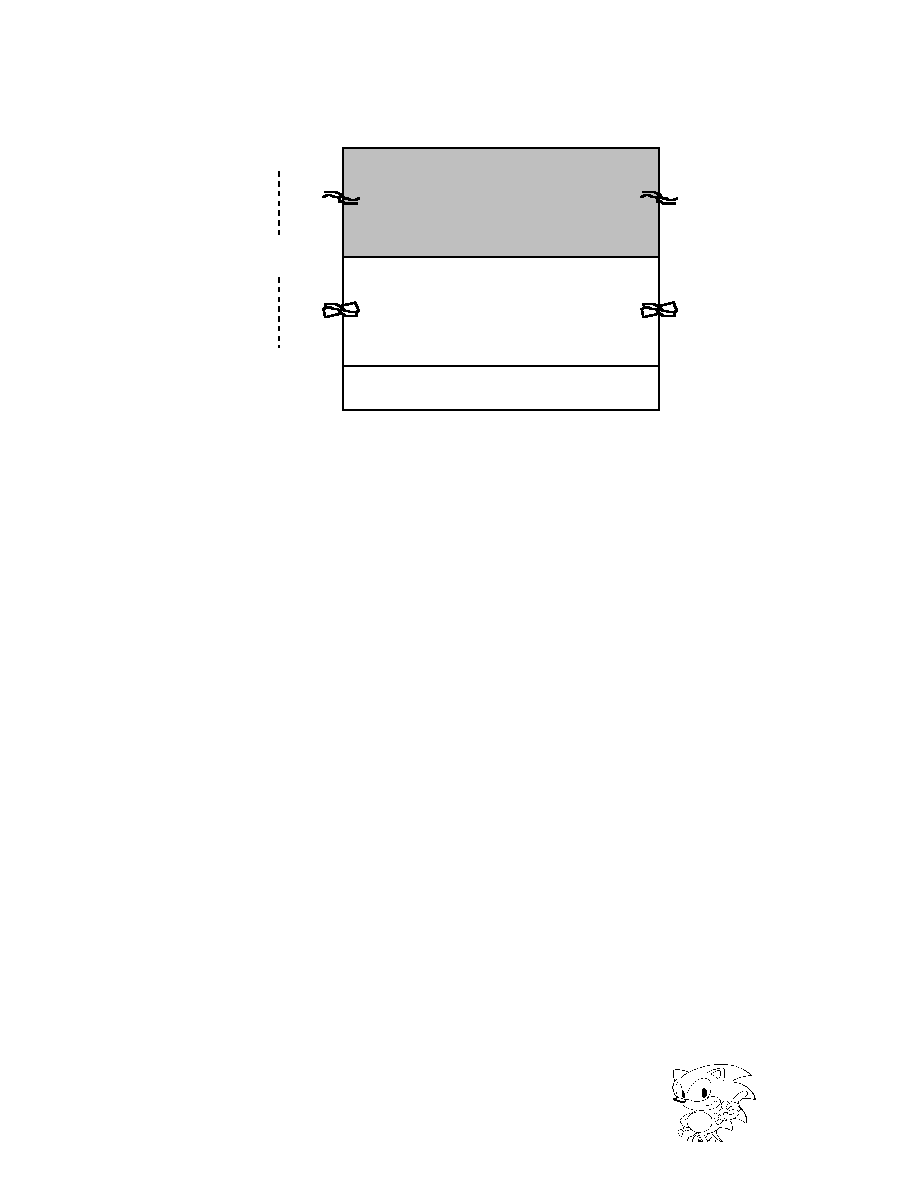

Table 1.1 Sound CPU Address 100400H, 100401H

M4: MEM4MB

D8:DAC18B

The sound CPU reads the reset vector from the 8 bits of the sound CPU address

(000000H~000007

H

), so always transfer the CPU reset vector to this area.

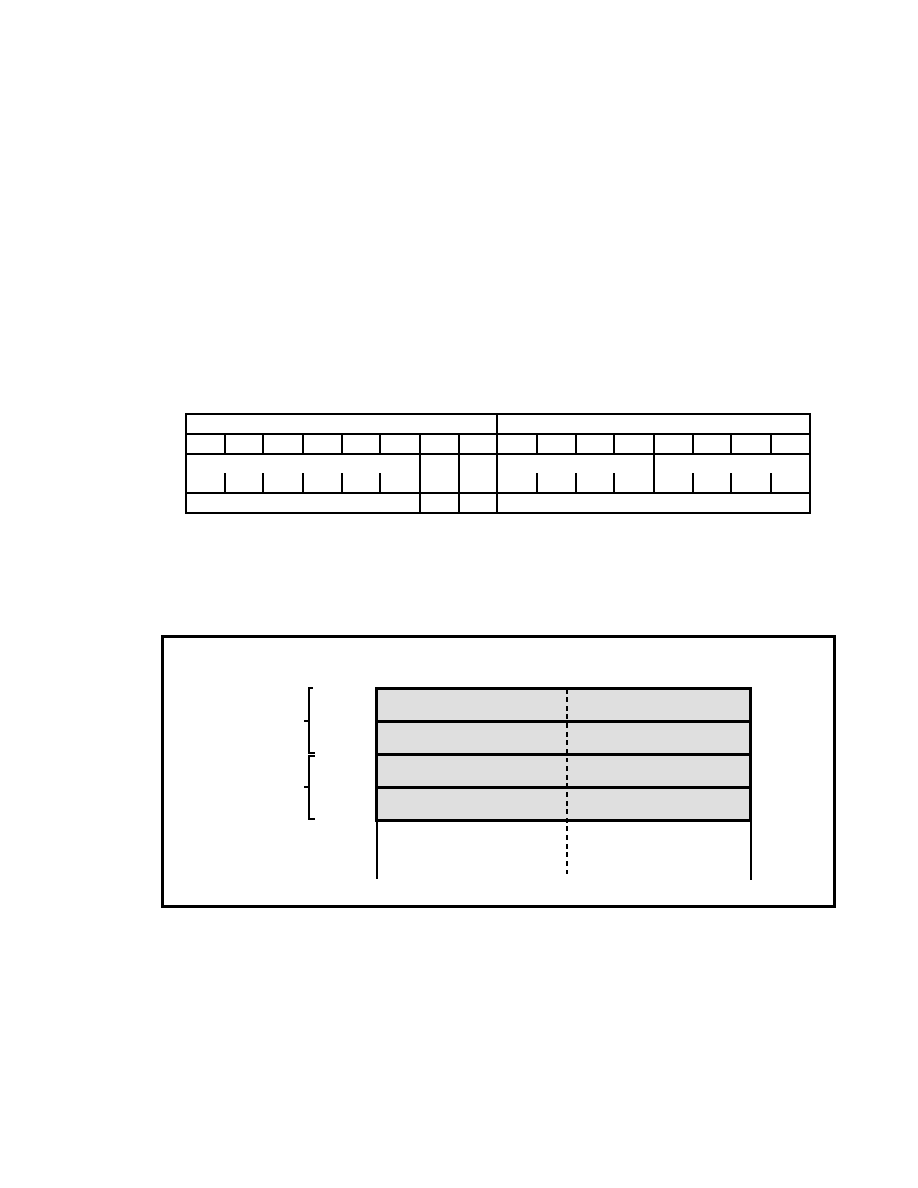

RESET VECTOR 0

RESET VECTOR 1

000000

000002

000004

000006

15

· · · · · · · · · · · · · ·

8 7

· · · · · · · · · · · · · ·

0

Stack Address

Stack Address

Program Counter

Program Counter

Upper Word

Lower Word

Upper Word

Lower Word

000001

000003

000005

000007

H

H

H

H

H

H

H

H

Address in the

MC68EC000

DRAM Area

·

·

·

·

·

·

Figure 1.4 Sound Memory Range (MC68EC000, SCSP)

After the reset is released, the sound CPU reads the reset vector and jumps to the PC

value address.

(100400

H

)

(100401

H

)

b15

b14

b13

b12

b11

b10

b9

b8

b7

b6

b5

b4

b3

b2

b1

b0

VER [3 : 0]

MVOL [3 : 0]

M4

D8

D3

D2

D1

D0

D3

D2

D1

D0

0

0

0

0

0

0

1

0

|

SEGA Confidential

6

After download has finished, the sound CPU is reset by the SMPC enabling the

sound CPU to operate.

Sound System Communication

Communication with the Main System

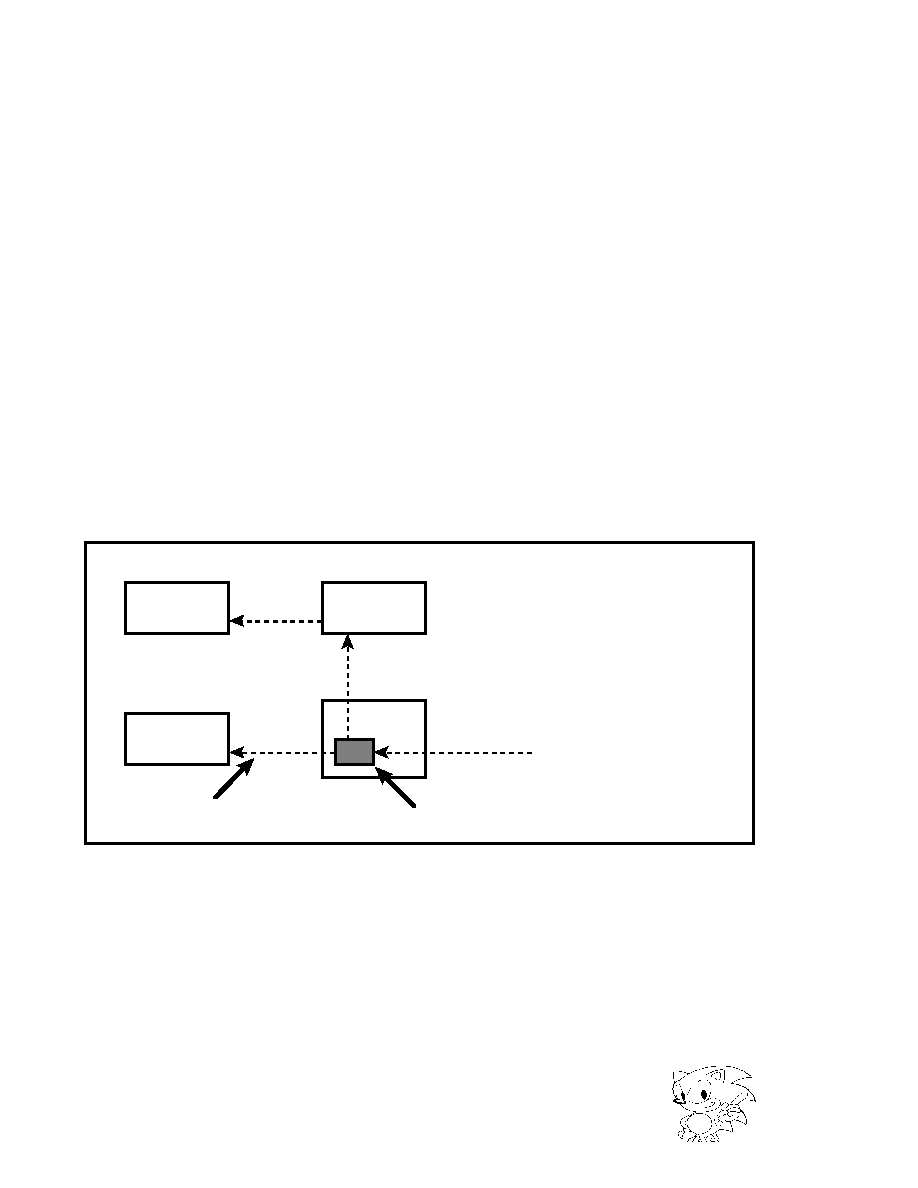

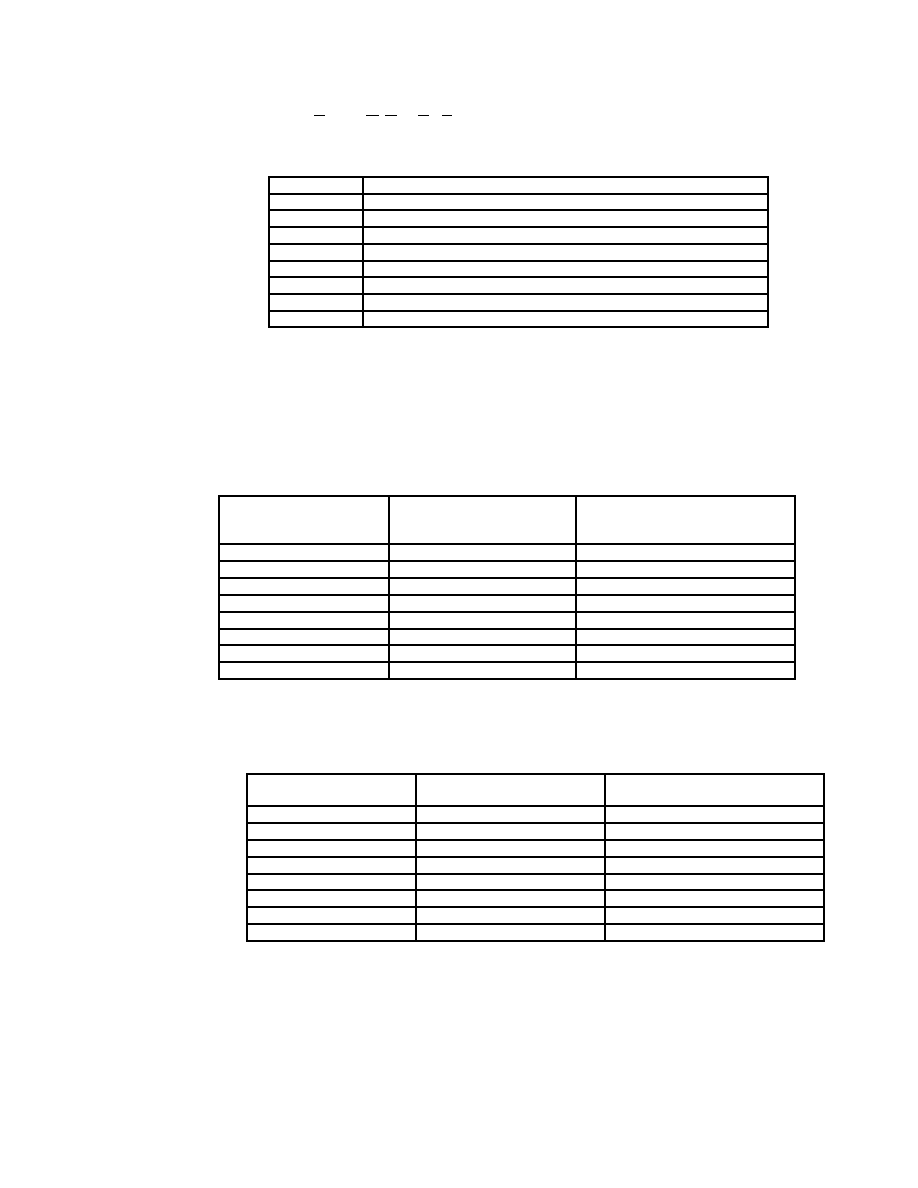

Communication between the main system and the sound system takes place

through the SCU. The sound CPU cannot access the main system through the SCSP.

Access is limited to access from the main system only.

Interrupt Signal

The main system uses the SCSP interrupt register when it sends an interrupt to the

sound CPU (explained in detail later on). This is executed by writing a "1B" to bit 5

of the interrupt register (SCIPD).

All interrupts that can be applied to the sound CPU can be used as interrupts for the

main CPU.

Please refer to the register explanations for sending interrupts from the sound sys-

tem to the main system.

SH-2

SCU

SCSP

MC68EC000

Sound CPU Interrupt

Interrupt Control Block

Interrupt

Main System (Main CPU) Interrupt

Main System

External Expansion Interrupt

(Not yet connected in Saturn)

Figure 1.5 Interrupt Relations

Interrupts to the sound CPU use an auto vector method. Vector data is shown in

Table 1.2.

Interrupt levels for the sound CPU can be set at different levels for each interrupt

factor. (See register explanations for settings.)

|

SEGA Confidential

Saturn SCSP User's Manual

7

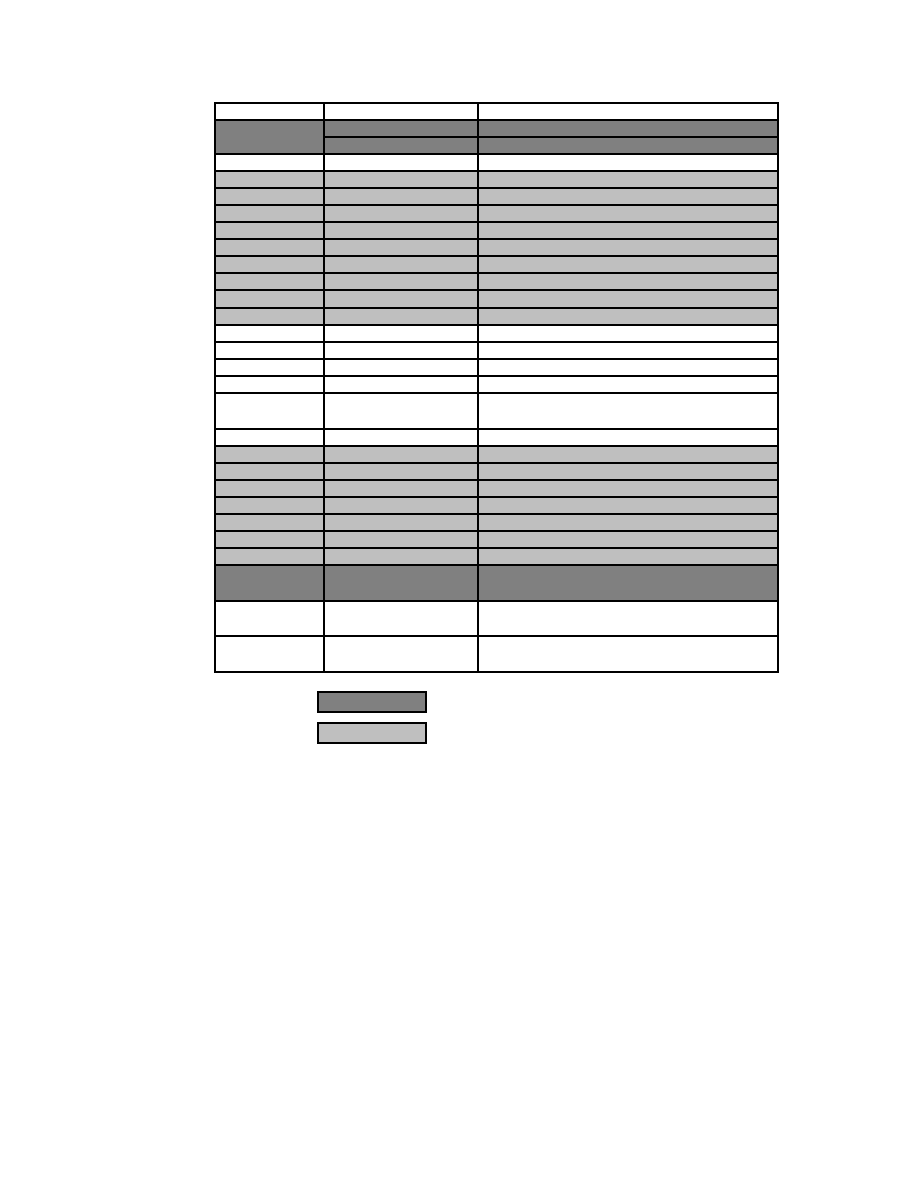

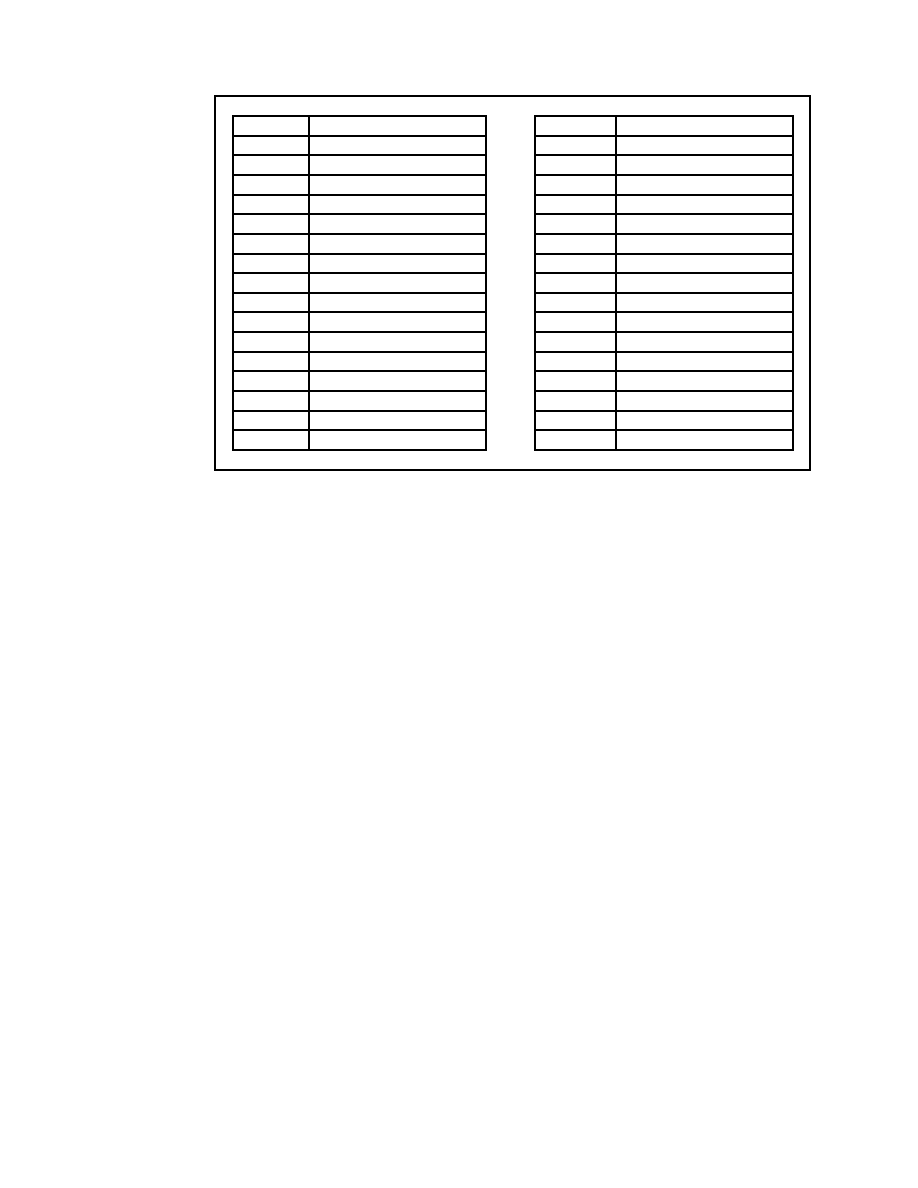

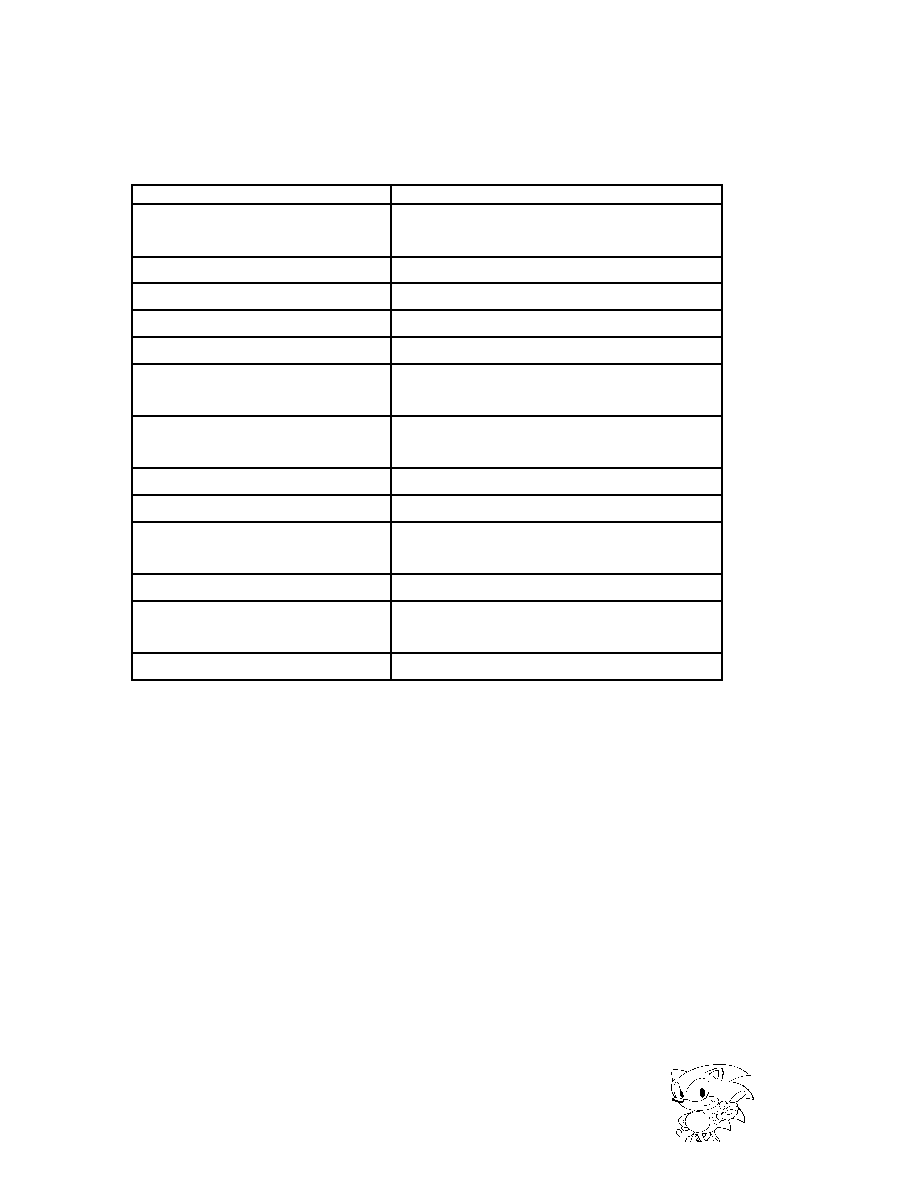

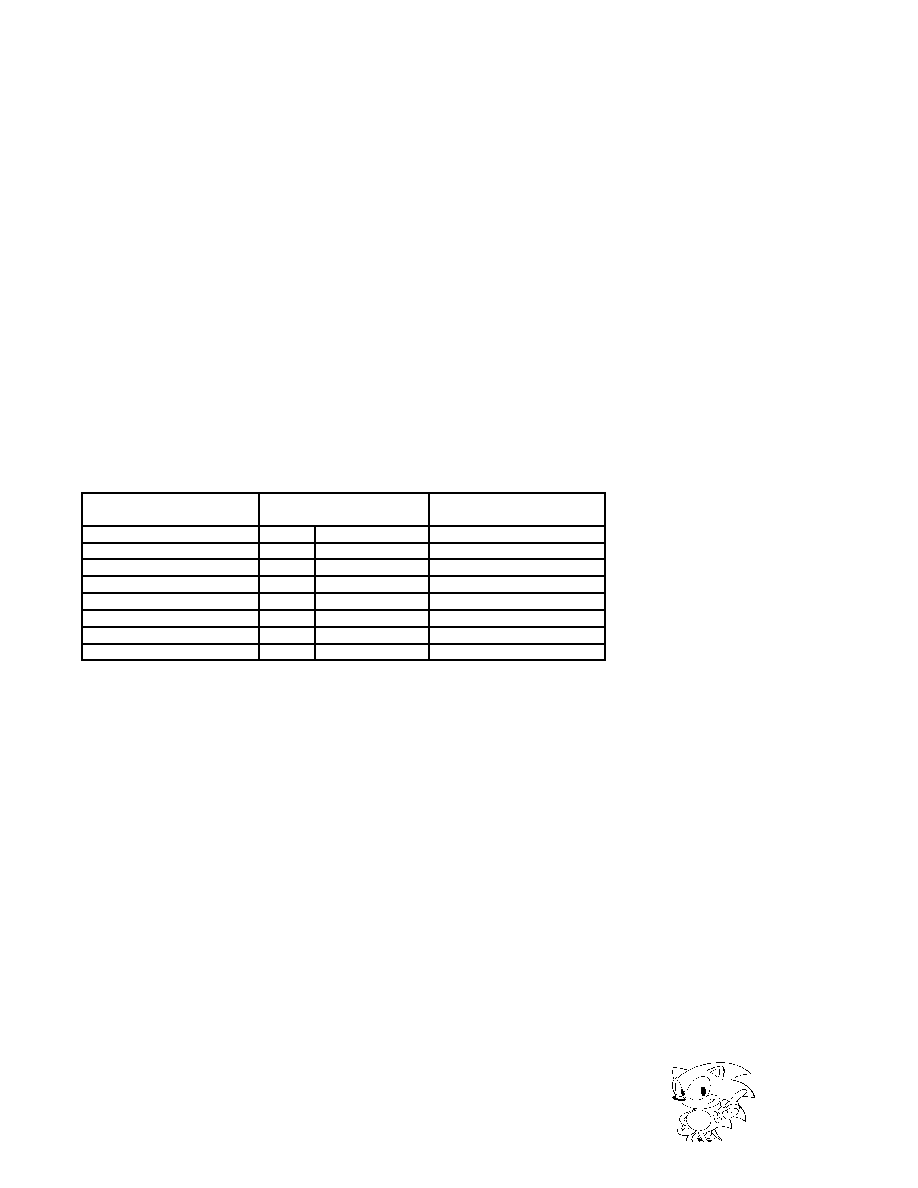

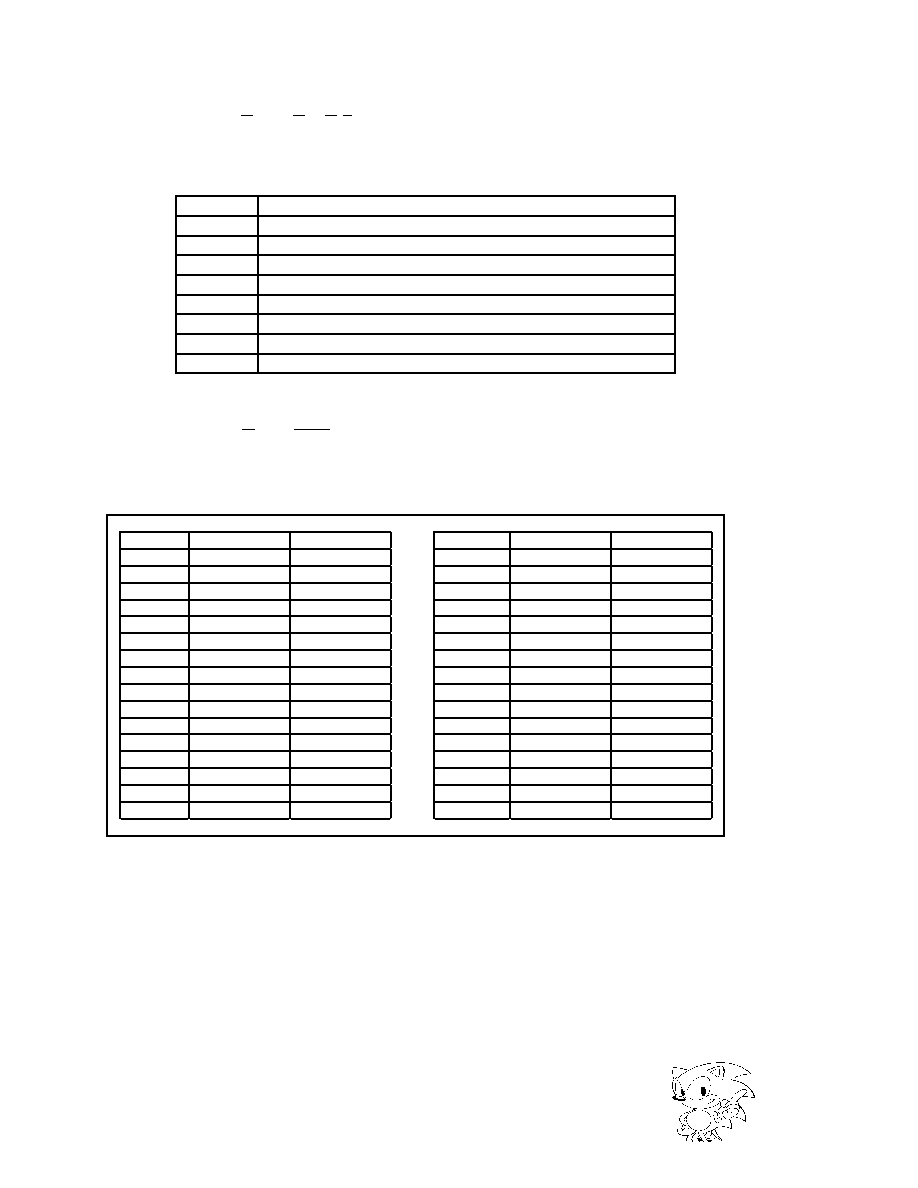

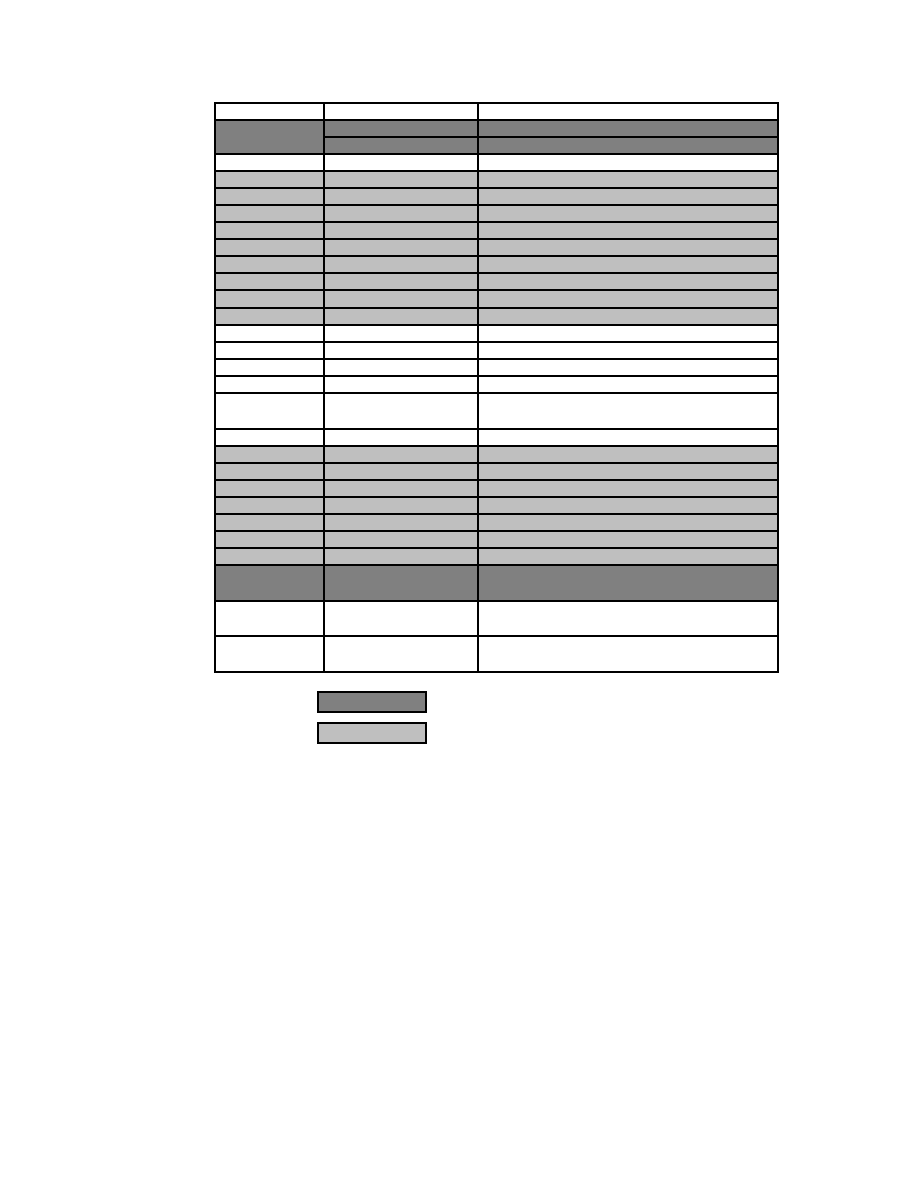

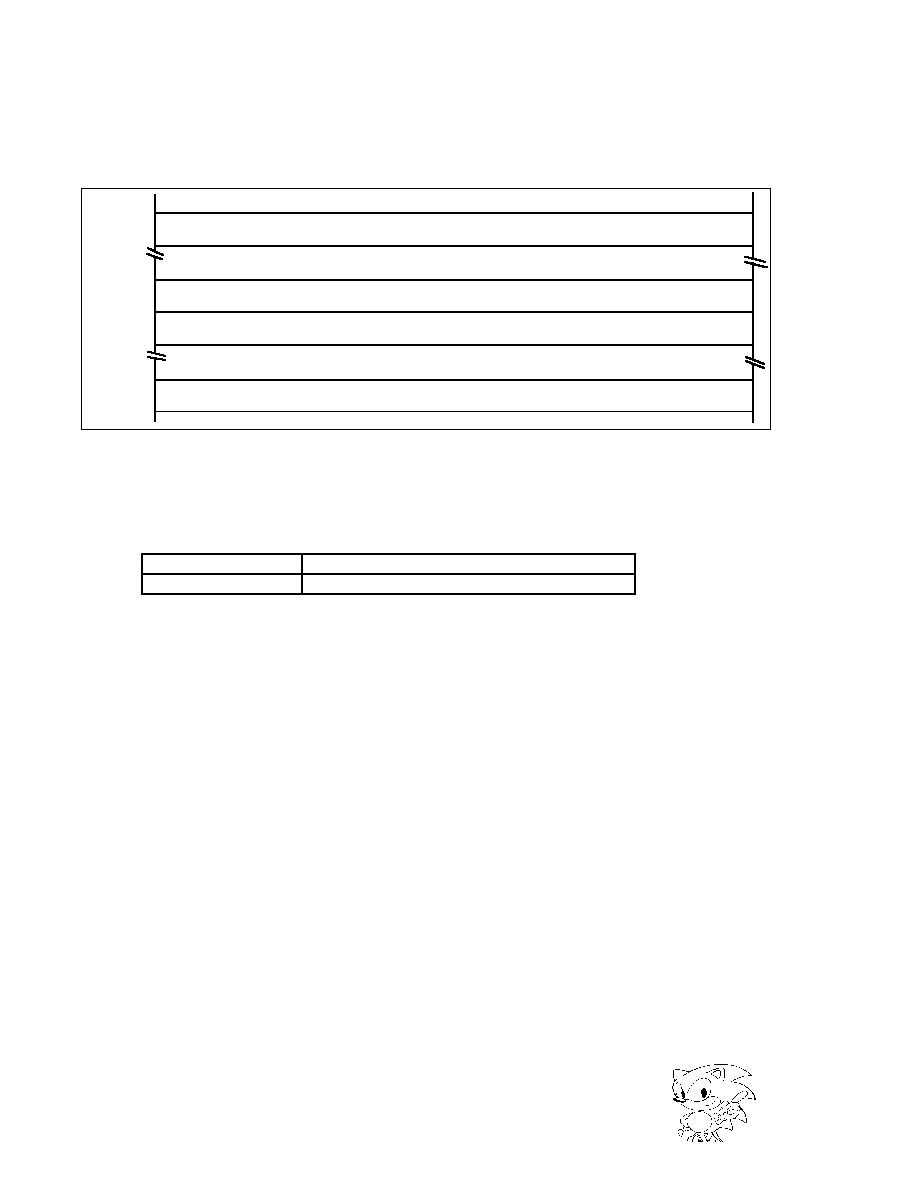

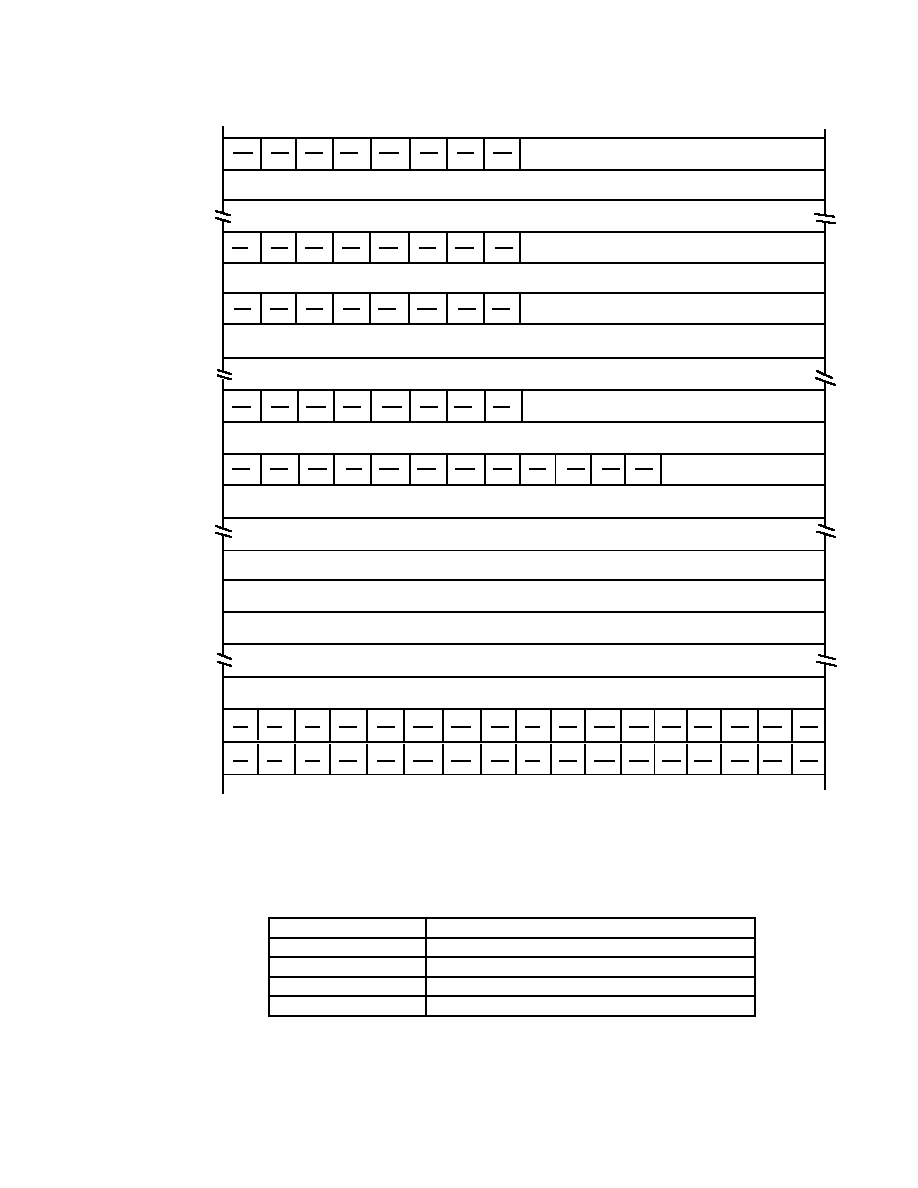

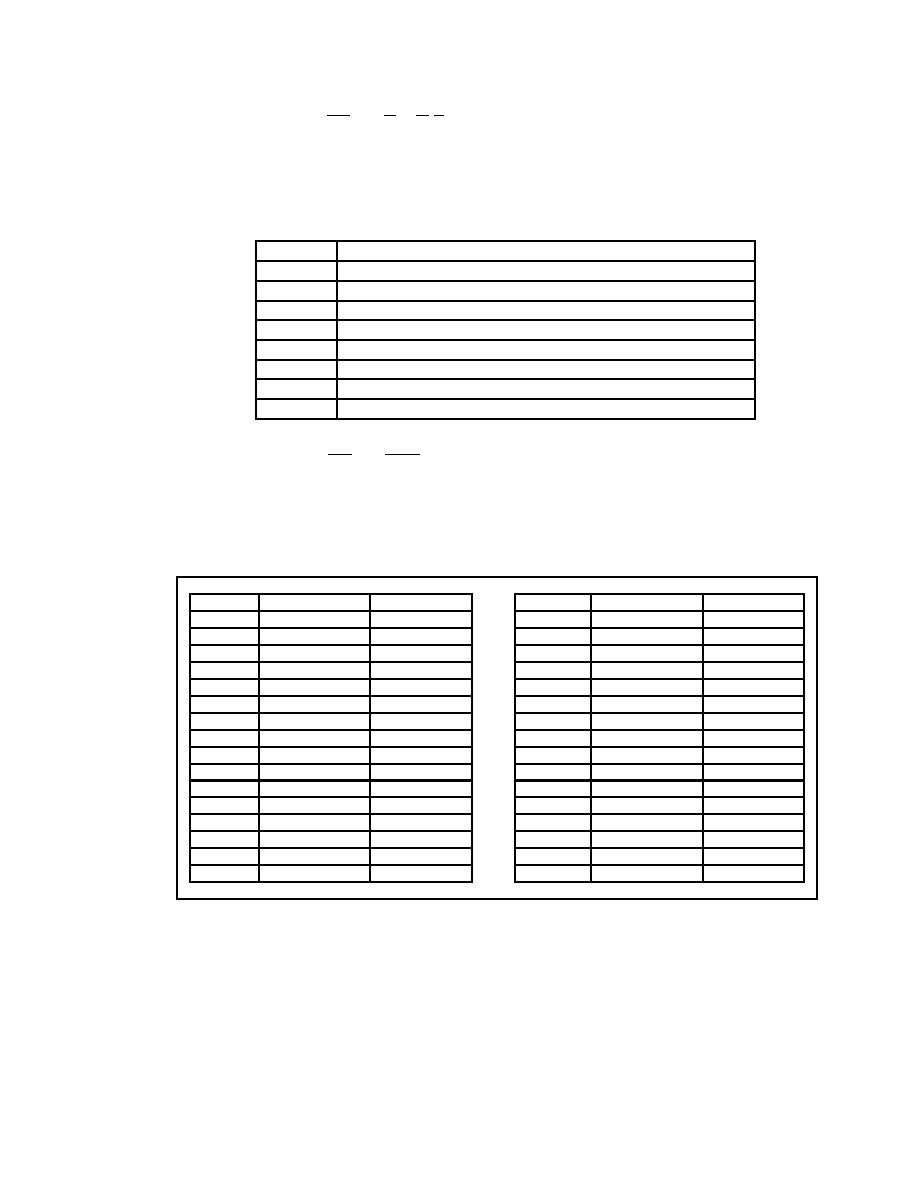

Table 1.2 Sound CPU Interrupt Vector Table

Note:

The sound development tools supplied by this company use the auto vector level 7 interrupt,

so users will not be able to use that level.

Interrupt Signals to the Main and the SCU DMA

The interrupt signal to the main CPU can also be used as triggers for the DMA

transfer start that have a SCU. (Refer to the SCU manual for details.)

Vector No.

MC68EC000 Address

Interrupt Vector Contents

0

000000

H

Reset vector initial SSP value

000004

H

Reset vector initial PC value

2

000008

H

Bus error

3

00000C

H

Address error

7

000010

H

Invalid command

5

000014

H

Calculation by 0 (Zero)

6

000018

H

CHK command

7

00001C

H

TRAPV command

8

000020

H

Privilege violation

9

000024

H

Trace

10

000028

H

Line 1010 emulator

11

00002C

H

Line 1111 emulator

12

000030

H

Undefined (Reserved)

13

000034

H

Undefined (Reserved)

14

000038

H

Undefined (Reserved)

15

00003C

H

Uninitialized interrupt vector

16~23

000040

H

~00005F

H

Undefined (Reserved)

24

000060

H

Spurious interrupt

25

000064

H

Auto vector level 1 interrupt

26

000068

H

Auto vector level 2 interrupt

27

00006C

H

Auto vector level 3 interrupt

28

000070

H

Auto vector level 4 interrupt

29

000074

H

Auto vector level 5 interrupt

30

000078

H

Auto vector level 6 interrupt

31

00007C

H

Auto vector level 7 interrupt

32~47

000080

H

~0000BF

H

TRAP command vector

48~63

0000C0

H

~0000FF

H

Undefined (Reserved)

64~255

000100

H

~0003FF

H

User interrupt vector

Normal use vectors.

Vectors open to users.

|

SEGA Confidential

8

|

SEGA Confidential

Saturn SCSP User's Manual

9

Chapter 2

SCSP Overview

Chapter 2 Contents

2.1 LSI Overview ..................................................... 10

2.2 LSI Specifications .............................................. 11

2.3 SCSP Chip Block Diagram ................................ 13

|

SEGA Confidential

10

2.1 LSI Overview

Since SCSP was developed with multi-media in mind, the audio features have better

functions and higher quality than before. The calculation block is equipped with

synthesizers that have performance comparable to those currently on the market

enabling a wide variety of sounds to be produced. Also, with future expansion in

mind, various interfaces are equipped. The DSP block can also produce composite

sound stages, and perform special effects such as play back of various sound stages

and special 3D sound positioning.

The characteristics of LSI are described below.

· Sampling Frequency

Sound generator block re-sampling frequency (set playback rate)

44.1KHz

Wave form data sampling frequency

0 (DC) ~ 44.1KHz

· Characteristics

-

32 slots for FM or PCM use built-in.

-

One per slot (completely independen

t) incorporates the total of 32 LFOs.

-

Incorporation of 32 EGs of 4 segment .

-

Interface for a built-in CPUs: The main CPU and the sound CPU

-

Built-in MIDI interface.

-

Built-in 128 step DSP

-

Built-in input mixer that selects DSP input

-

Built-in output mixer to mix sound generating output and DSP outputs.

-

Incorporation of a new FM calculation method.

|

SEGA Confidential

Saturn SCSP User's Manual

11

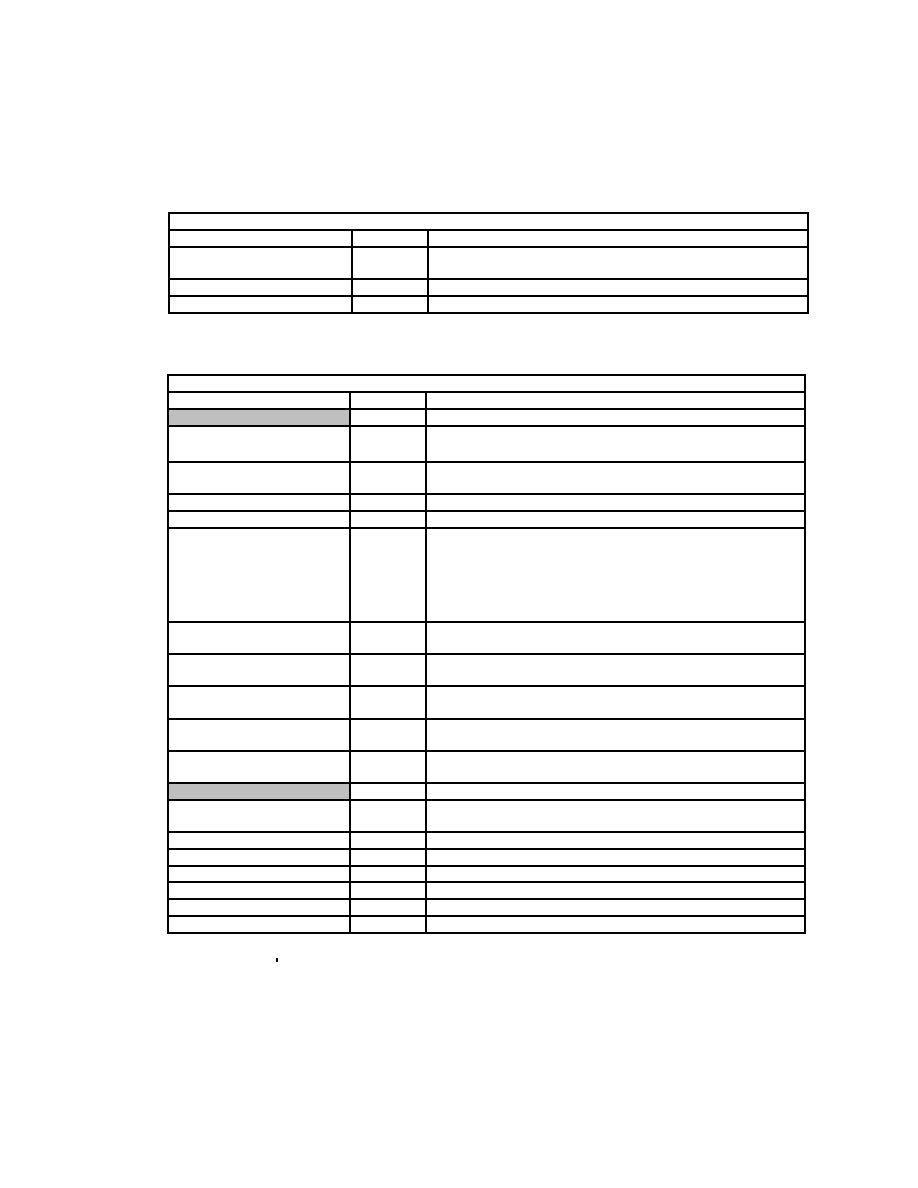

2.2 LSI Specifications

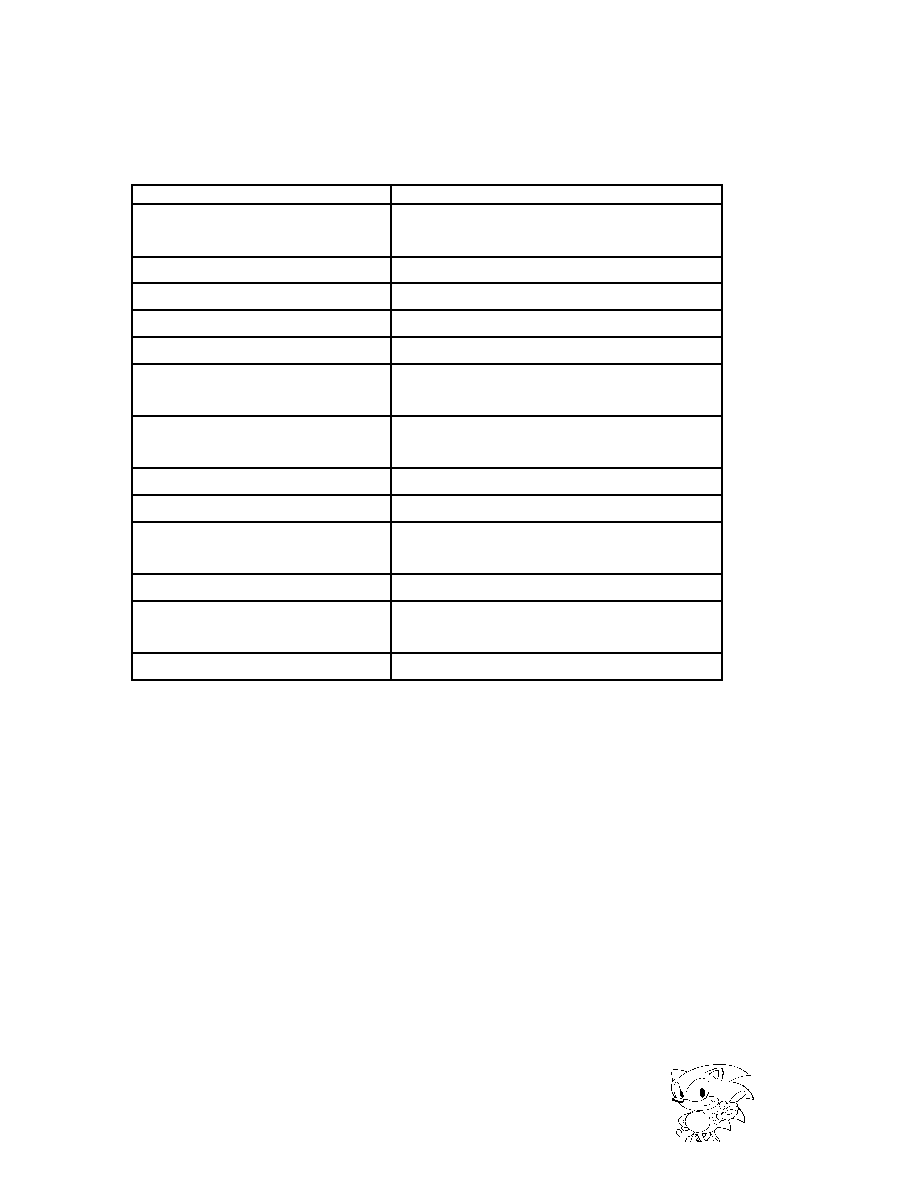

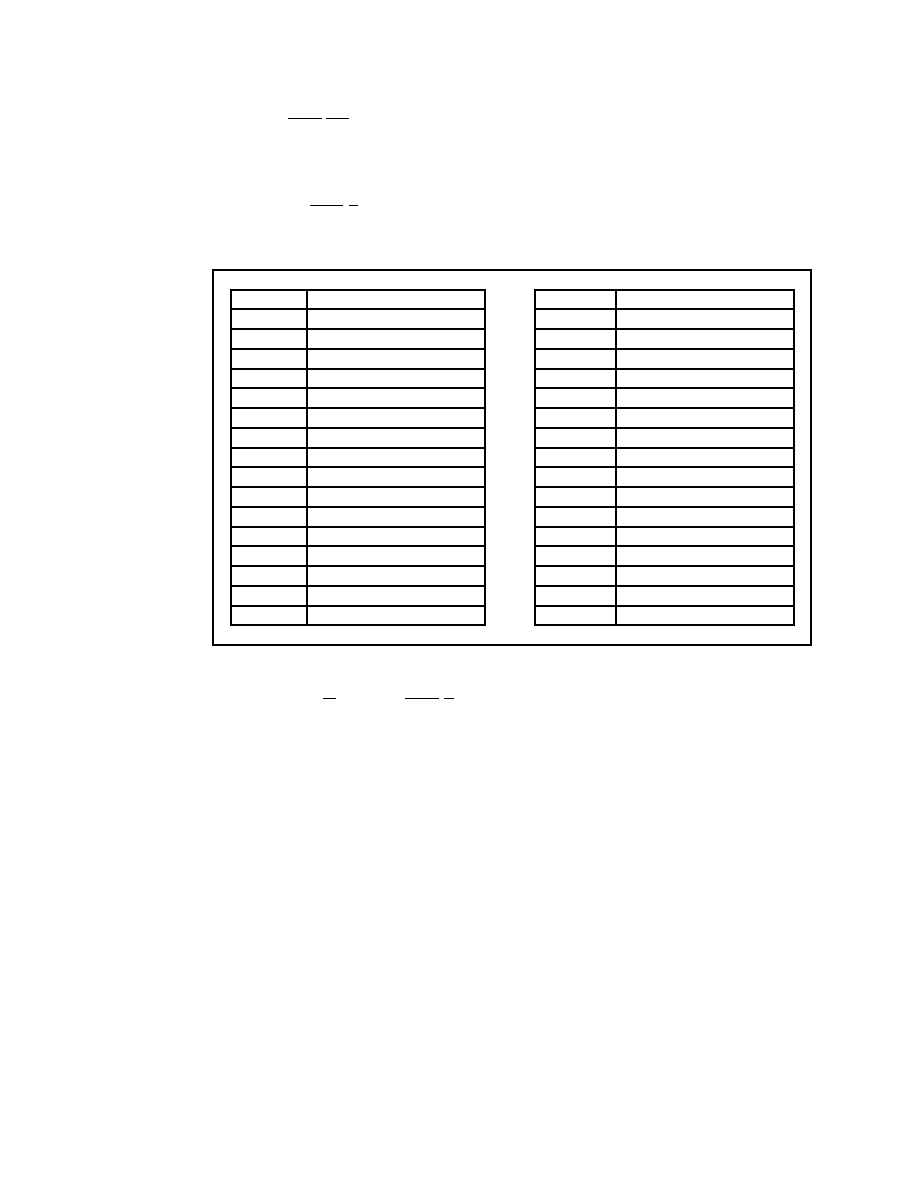

Table 2.1 shows the sound CPU (MC68EC000); tables 2.2 and 2.3 show SCSP LSI

detailed specifications.

Table 2.1 Sound CPU Specifications

Table 2.2 SCSP LSI Specifications (1)

1 FM sound mixing is not limited to the 4 operator (slot) types

used in the past, but 2~32 operators can be freely used for FM

connections. You may also freely set the feedback.

SOUND CPU MC68EC000-12 12.5MHz version

(Operating frequency 11.2896MHz)

Function

No. Included

Special Comments

CPU commands

Command system that is completely compatible with the

MC68000 CPU.

Interrupt signal

level 1~7 interrupt by auto vector .

Hardware configuration

MC68000 CPU with the MC6800 (8 bit) interface removed

SOUND LSI SCSP (SATURN CUSTOM SOUND PROCESSOR) (Operating frequency 22.5792MHz)

Function

No. Included

Special Comments

Sound mixing method

PCM sound mixing and FM sound mixing methods (

1)

noise source (can be used for mixing)

Sound source block

re-sampling frequency

44.1KHz fixed, primary interpolation

Wave form data format

16 and 8 bit linear 2'S complement method

Sound processor slots

32

Equal to 1 operator (1slot) in PCM and FM sound sources.

Maximum number of

simultaneous sounds

1~32

When all are 4 operator (slot) type FM sounds: 8 sounds

when all are PCM sounds, a total of 32 sounds.

(The number of slots per FM sound can be freely set. It is

also possible to mix FM and PCM sounds.

As long as the total number of slots does not exceed 32,

then any combination is possible.

Wave form loop function

Select from normal, reverse and alternative loops for each

slot.

EG

32

4 segment AMPLITUDE-EG (Each slot has 1 base

included)

LFO

32

Each slot has one installed ( for amplitude/frequency

modulation)

Types of LFO output wave

form

4

Four types: sawtooth, rectangular, triangular, and white

noise.

Sound source

oscillation frequency

-8~+7 octaves with 1024 steps between octaves

(nonlinear) can be set

Effect DSP block

DSP processor speed

128 steps/Fs (multiple parallel processing type DSP

Fs=44.1KHz)

Program RAM

128W

1 2 8 w o r d s x 6 0 b i t s

Coefficient data RAM

64W

6 4 w o r d s x 1 3 b i t s

Temporary (universal) RAM

128W

1 2 8 w o r d s x 2 4 b i t s

Multiplier accuracy

2 4 w o r d s x 1 3 b i t s = 2 6 b i t o u t p u t

Adder accuracy

2 6 w o r d s + 2 6 b i t s = 2 6 b i t o u t p u t

DSP internal bus width

2 4 b i t d a t a b u s

Sound Source

|

SEGA Confidential

12

Table 2.3 SCSP LSI Specifications (2)

Function

No. Included

Special Comments

Digital mixer block

Output level adjustment

steps

8 steps (for each slot sound, DSP output sound)

Panpot level adjustment

steps

31 steps (center 1 step, left and right, 15 steps each)

DSP effect send channel

count

16

Able to mix and store multiple slot output in each channel

DSP effect return channel

count

16

Able to set level and panpot for each channel.

Master volume set function

Stereo capable

CPU interface

Main CPU interface

1

SCU B-BUS interface

Sound CPU interface

1

MC68EC000 interface

Other functions, interfaces

Timer

3

8 bit timers with prescaler

DMAC

1

DMA controller for transfer between SCSP~DRAM

Interrupt controller

1

Interrupt controller for the main and sound CPUs

MIDI interface

IN: 1 OUT: 1

Digital audio interface

1

Input stereo interface: 1

Sound memory interface

1

DRAM interface

DAC output interface

1

16 bit/ 18 bit stereo DAC interface

External interrupt signal

interface

3

Not connected/used in the Saturn

DSP program library

Various types of effect

programs

REVERB (HALL, ROOM, VOCAL, PLATE, ETC.)

EARLY REFLECTION

ECHO / DELAY (STEREO, MONORAL)

PITCH SHIFTER (SINGLE, DOUBLE, TRIPLE)

CHORUS, FLANGER

SYMPHONIC, SURROUND

VOICE CANCEL, AUTOPAN

PHASER, DISTORTION

FILTER

PARAMETRIC EQUALIZER

|

SEGA Confidential

Saturn SCSP User's Manual

13

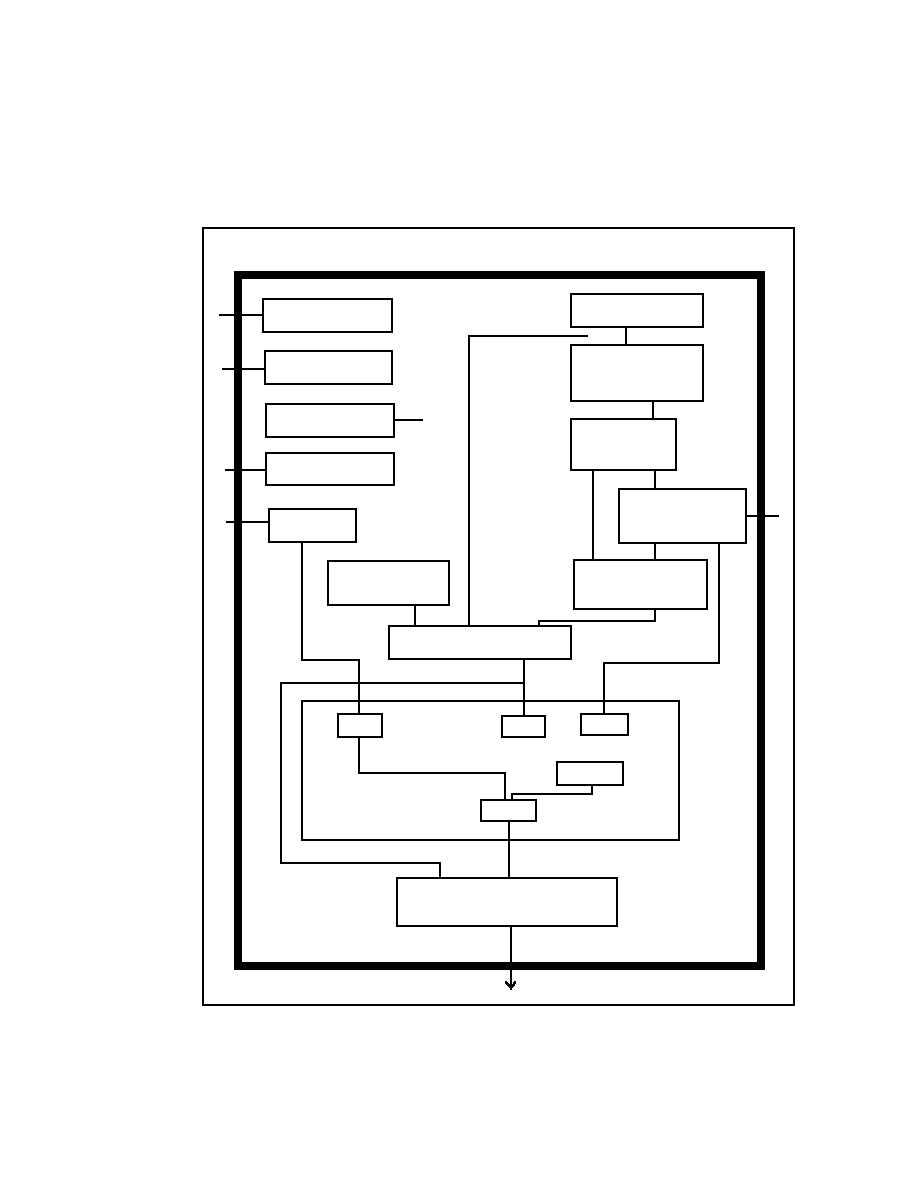

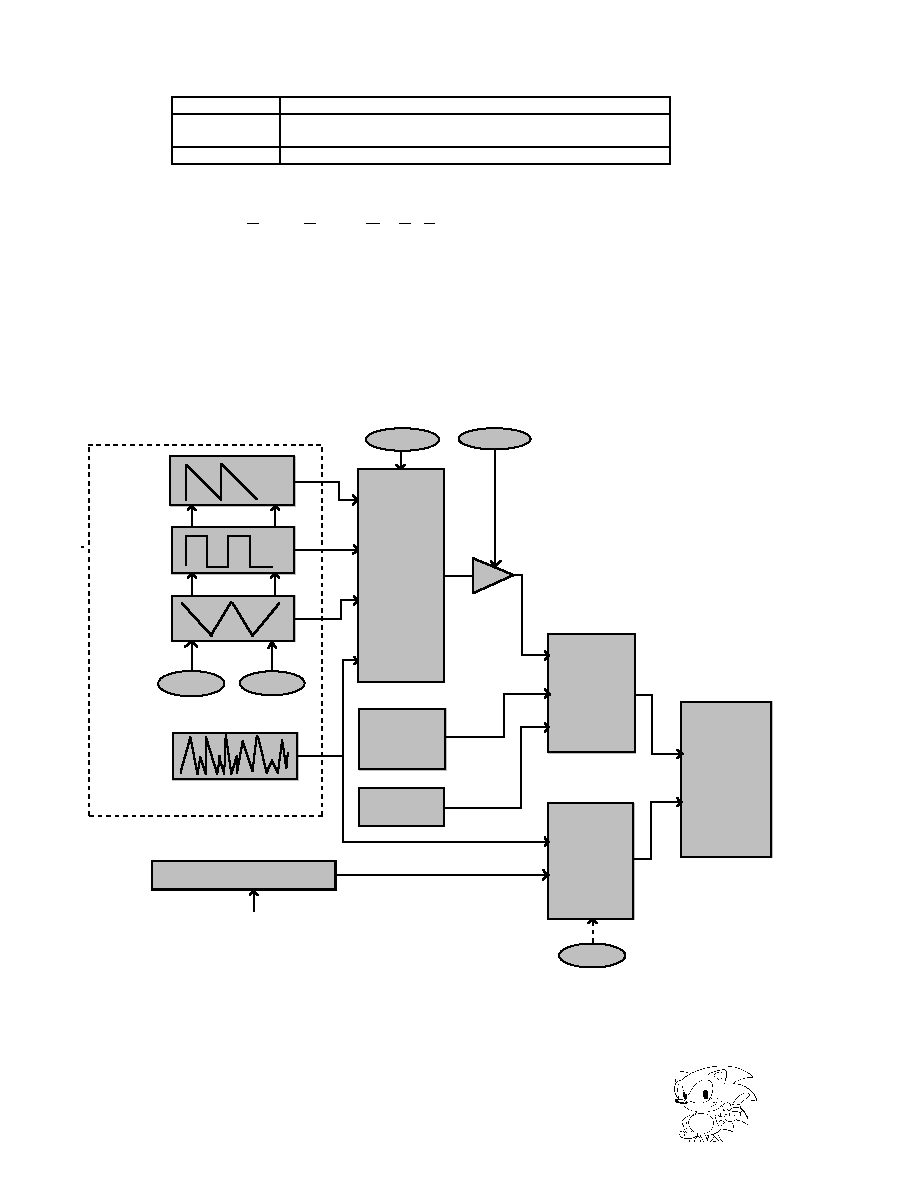

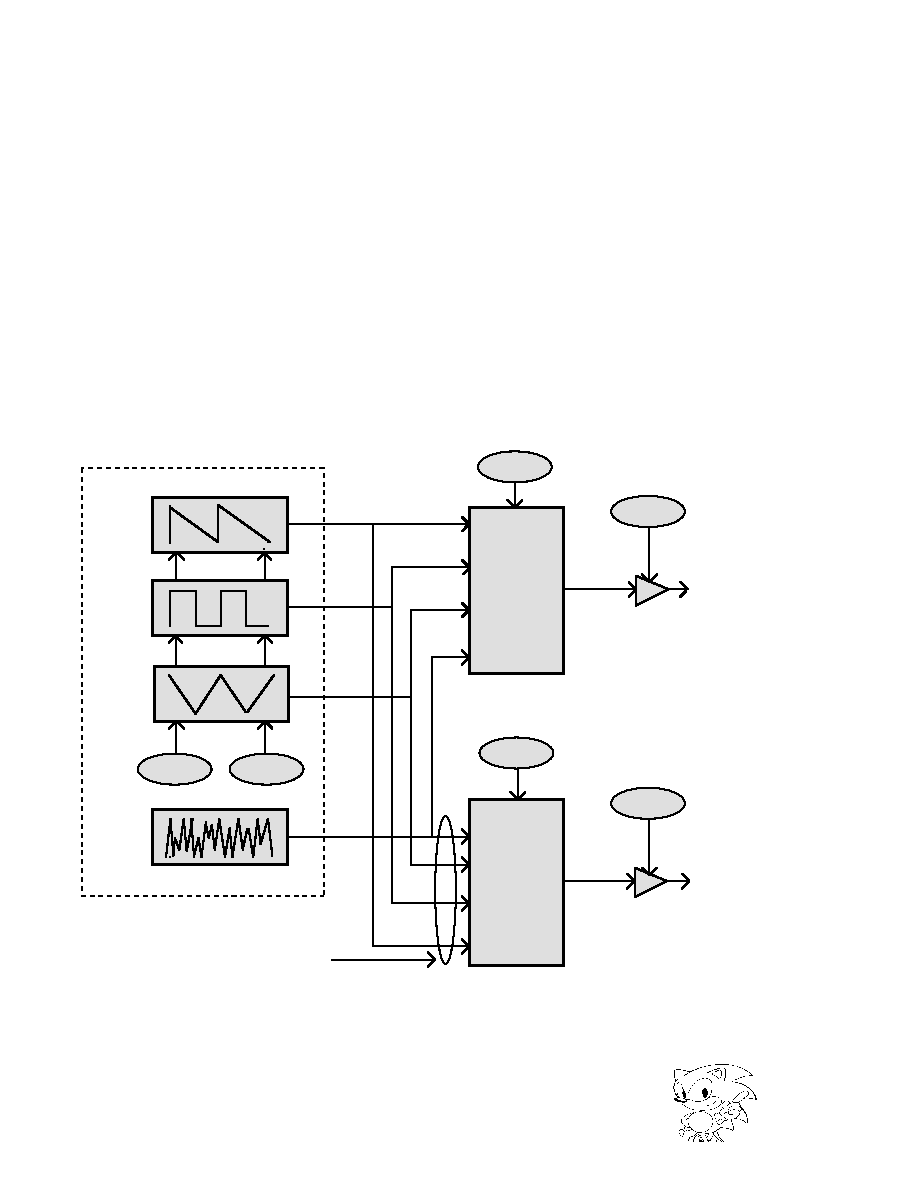

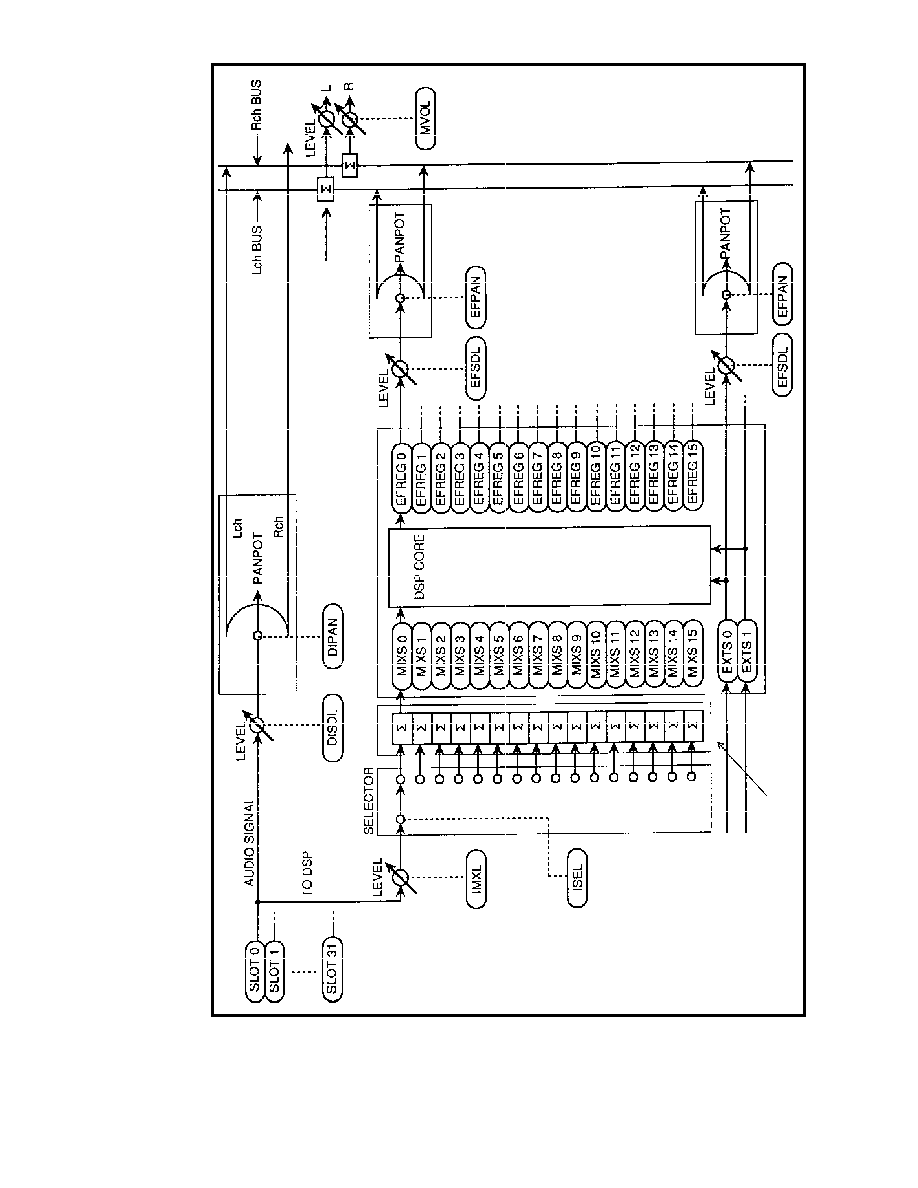

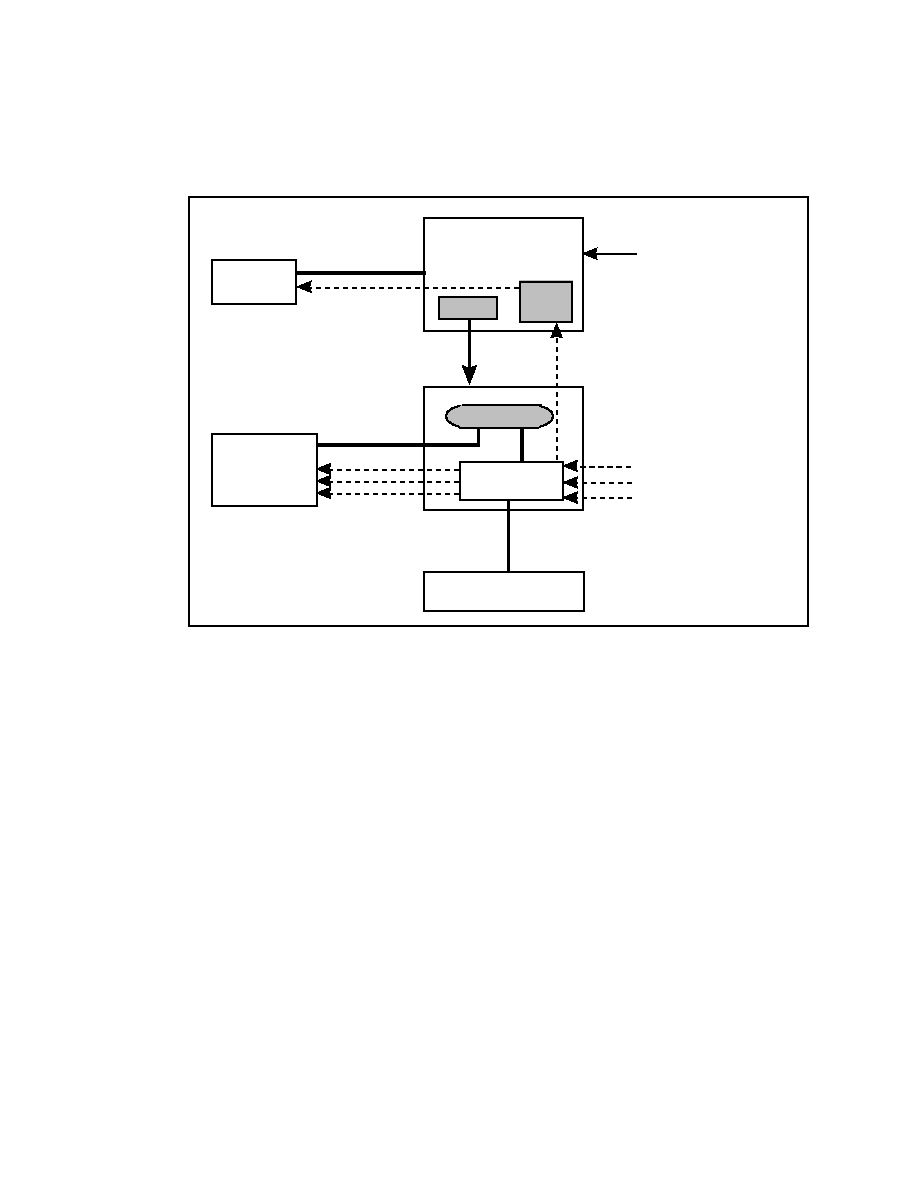

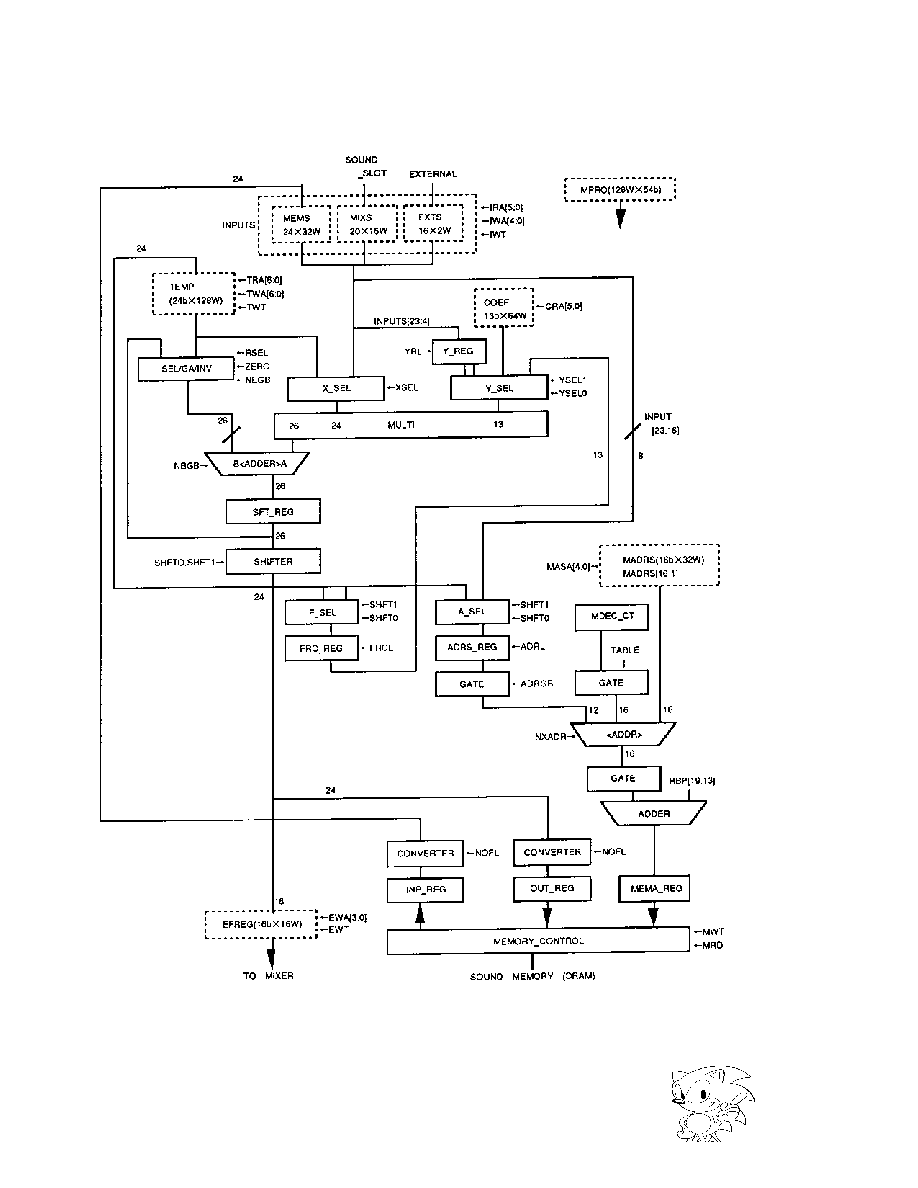

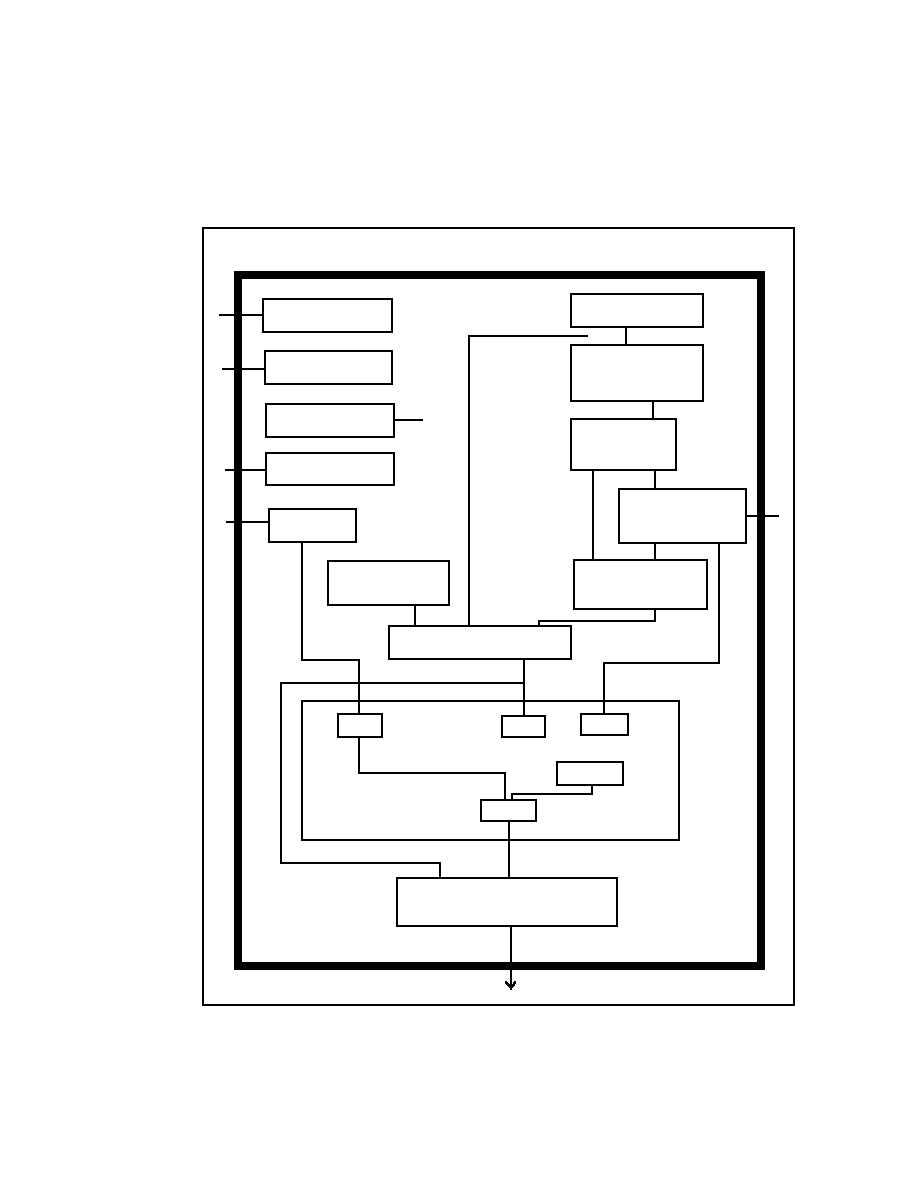

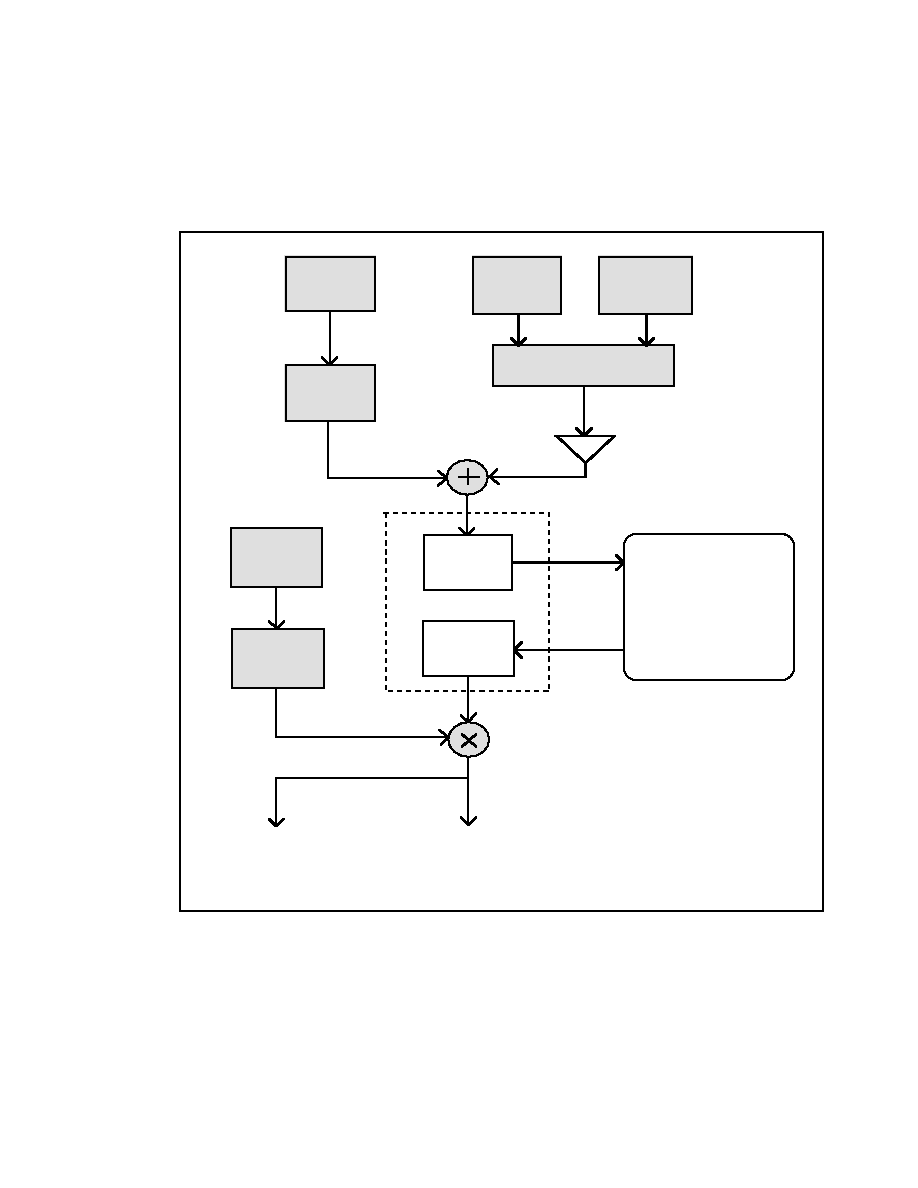

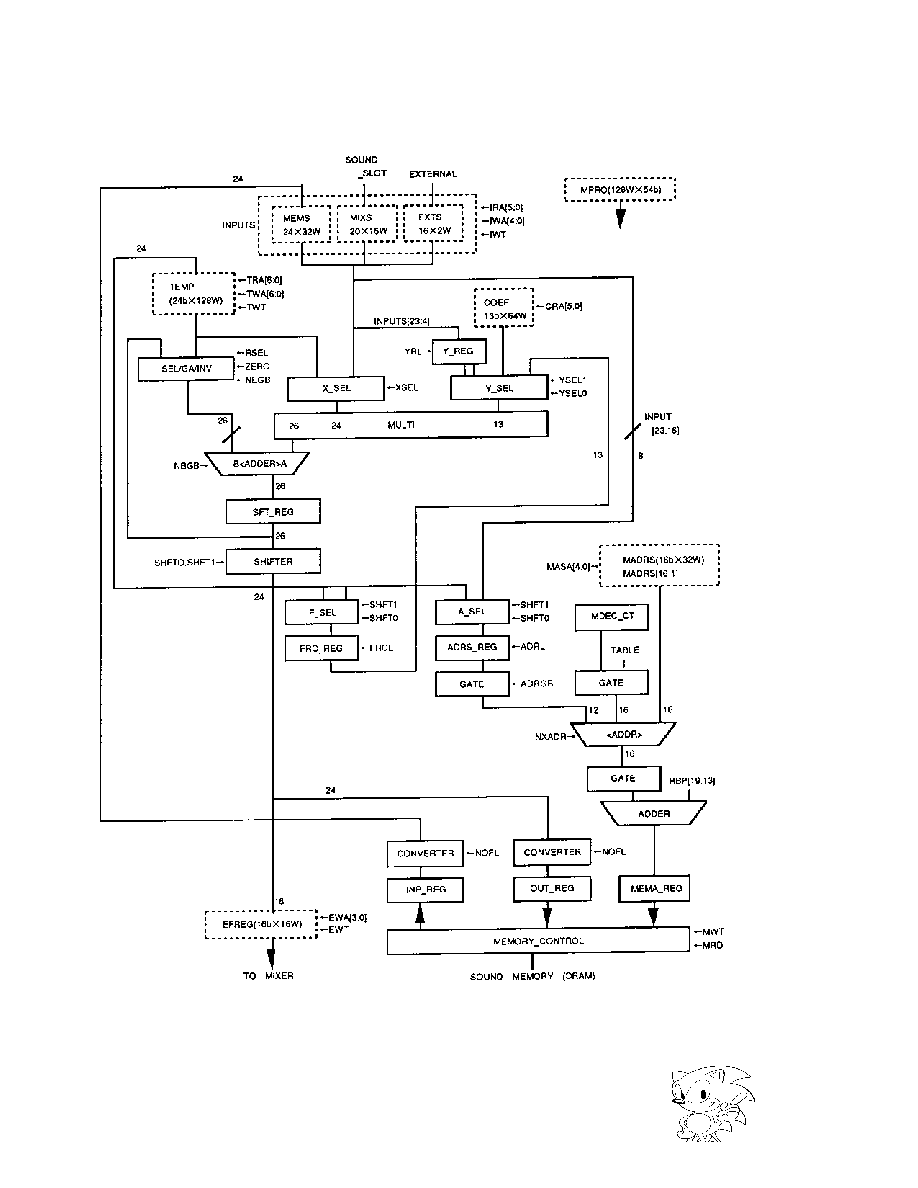

2.3 SCSP Chip Block Diagram

Figure 2.1 shows the SCSP chip block diagram.

SCSP

Sound CPU

Interface

Main CPU

Interface

DMA Transfer

Interface

MIDI

Interface

External

Input

Envolope

Generator

Level Calculator

LFO

Phase

Generator

Address

Pointer

Memory

Controller

Interpolator

AFLO PLFO

PHASE

PHASE

PLFO

ADSR-L ADSR-R

DATA DATA

ADSR-R

ADSR-L DATA

PCM-DATA

PCM_DATA

EG

ALFO

Output

Mixer

EXTS

MIXS

MEMS

EFREG

SEL

DSP

DIR

EFREG

EG

Figure 2.1 SCSP Chip Block Diagram

|

SEGA Confidential

14

Items shown in SCSP Chip Block Diagram Figure 2.1 are explained below.

Sound CPU Interface

Interface that connects to the MC68EC000.

Main CPU Interface

Interface that connects the system controller (SCU).

DMA Transfer Interface

This is the SCSP built-in DMA controller. It enables data

transfer between the SCSP and the sound memory.

MIDI Interface

This serial interface complies with MIDI specifications;

however, some external circuits will be needed to make it

compatible with a MIDI connector.

External Input (External Digital Audio Input Interface)

Interface that inputs a digital audio signal from an exter-

nal instrument (external device).

L F O (Low Frequency Oscillator)

Indicates a function generator that generates wave forms

of a frequency that is below the range that the human ear

can hear, and is used as a wave form for various modula-

tion.

Phase Generator

Block that calculates and outputs frequency data based

on

the sound generation frequency setting of the PCM

data.

Address Pointer

Creates the wave form address value based on the phase

information, etc., from the phase generator.

|

SEGA Confidential

Saturn SCSP User's Manual

15

Memory Controller

Block that outputs the address created by the address

pointer to the memory and reads data, etc.; it controls the

sound memory.

Interpolator

Block that interpolates the wave form data.

Envelope Generator (EG)

Functional calculation block that controls the sound

output level with time.

Level Calculator Block

Block that calculates the wave form output level based on

the level coefficient created by EG, TL (Total Level), and

ALFO.

DSP

Audio DSP that receives and holds the SCSP special

sound effects.

Output Mixer

Final block that contains functions that calculate various

positions and level adjustments needed to compile each

sound output in stereo.

|

SEGA Confidential

16

|

SEGA Confidential

Saturn SCSP User's Manual

17

Chapter 3

SCSP Functions

Chapter 3 Contents

3.1 Interface

18

Sound CPU Interface

18

Main CPU Interface

18

3.2 Memory Access Control

20

Chapter 3 Contents

3.1 Interface .......................................................

18

Sound CPU Interface .................................... 18

Main CPU Interface ...................................... 18

3.2 Memory Access Control ............................... 20

|

SEGA Confidential

18

3.1 Interface

The SCSP has two internal CPU (main CPU and sound CPU) interfaces. The main

CPU has higher priority than the sound CPU, so the processing speed of the sound

CPU depends on the operation of the main CPU.

Sound CPU Interface

The sound CPU interface is a block with specialized functions to enable it to connect

to the sound CPU. By adding this interface, the sound CPU can be directly con-

nected to the SCSP without external circuits.

Programs for the sound CPU reside in the sound memory. For this reason, all CPU

programs are placed in the sound CPU address space available.

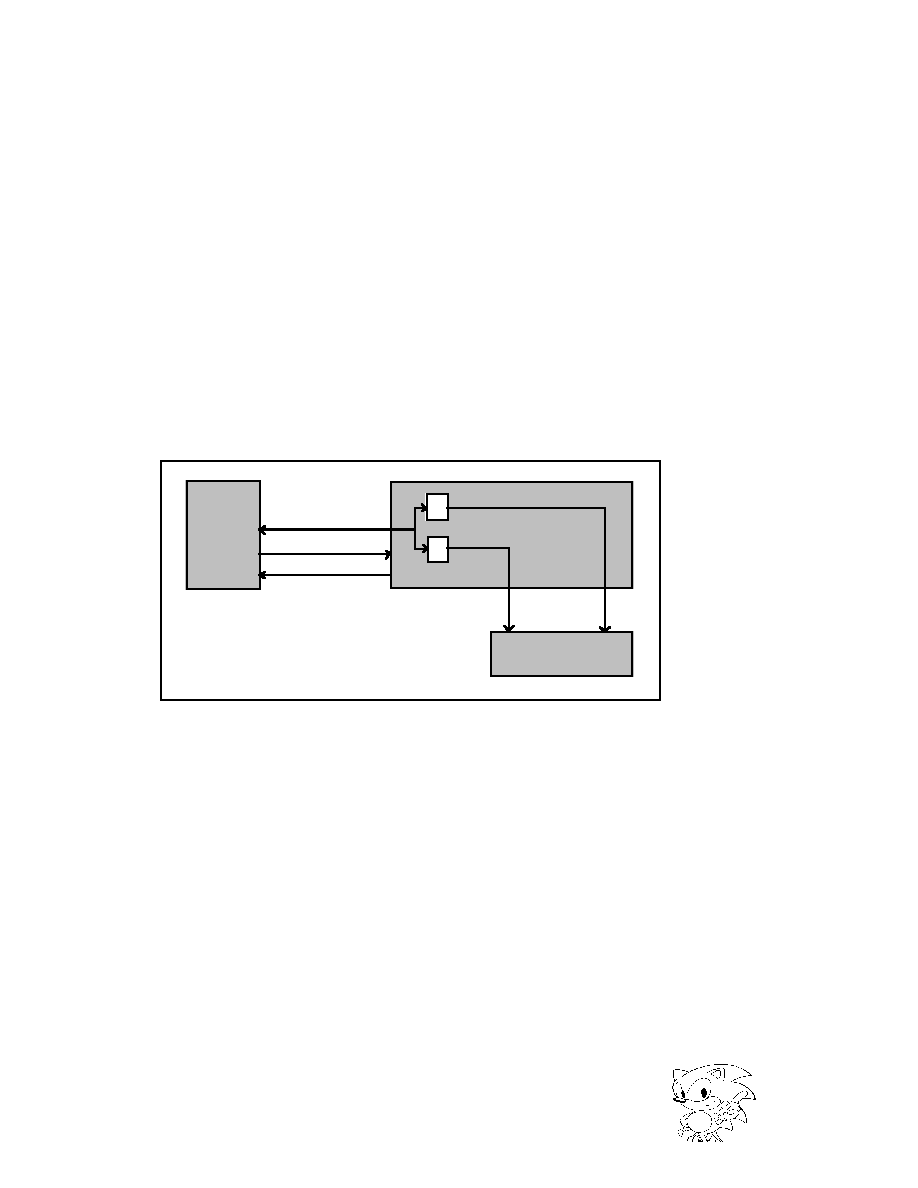

Main CPU Interface

Access between the main CPU and the interface is shown in Figure 3.1.

SCU

D

A

DRAM

SCSP

MCD

MCCSN

MCRDYN

Address

Data

Figure 3.1 Access Overview

At the trailing edge of the select signal (MCCSN) from the main CPU, the interface is

started; at the leading edge of the select signal, the interface is ended. Also, when "1"

is output with respect to the ready signal (MCRDYN) to the main CPU, the select

signal (MCCSN) from the main CPU and the main CPU data bus (MCD[7:0]) do not

change.

|

SEGA Confidential

Saturn SCSP User's Manual

19

The following cautions should be observed with interfacing with the main CPU.

(1)

Because the main CPU cannot access in units of 8 bits, so read and write in 16

bit units.

(2)

When there is a request to read or write, the SCSP buffer gets the address and

data. Because of this, a "1" is output to the ready signal (MCRDYN) going to

the main CPU causing a wait. This wait continues until the internal processing

of the LSI is finished. For this reason, continuous read and writes that cause

many waits to occur should be avoided except when turning on the power.

(3)

When the power is turned on, the time necessary for initialization of sound

memory by continuous writing is approximately 100 msec for 4Mbit DRAM.

|

SEGA Confidential

20

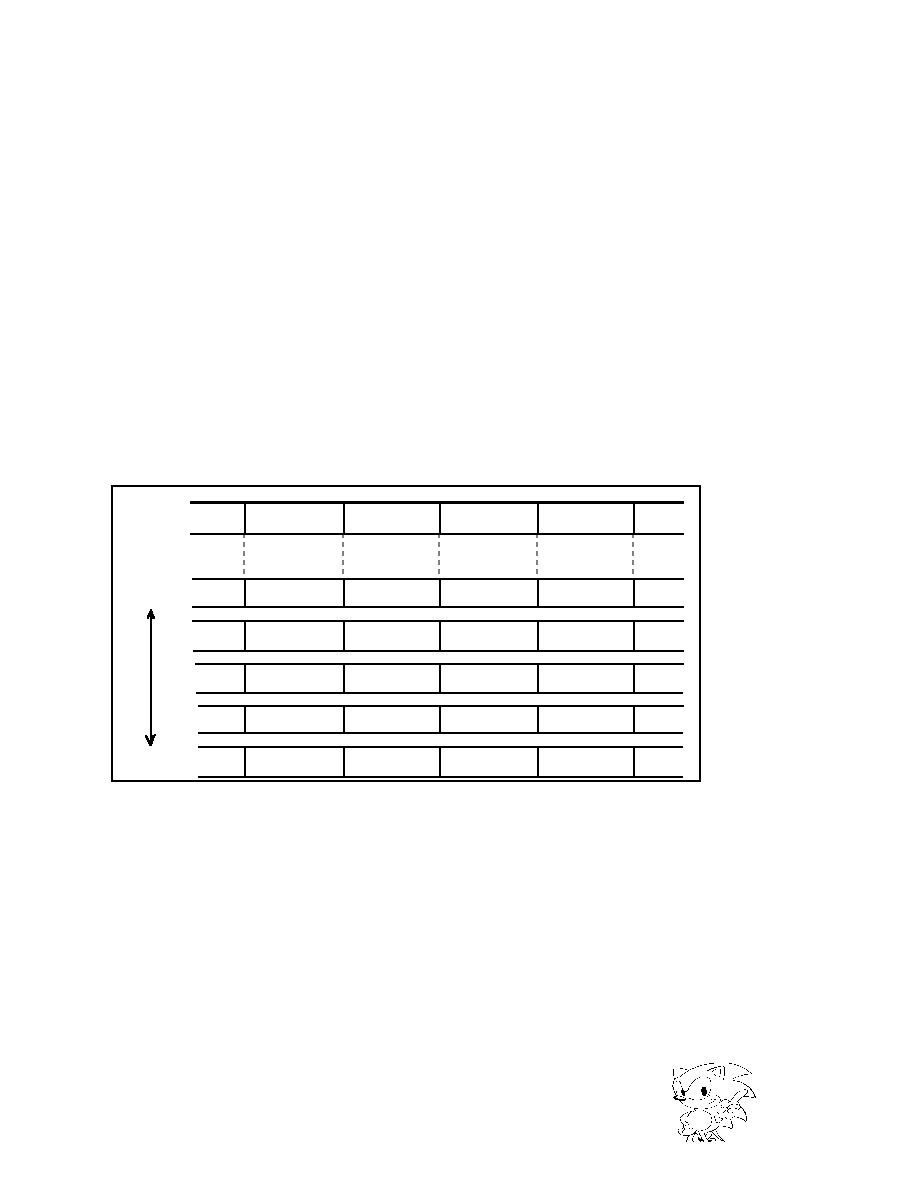

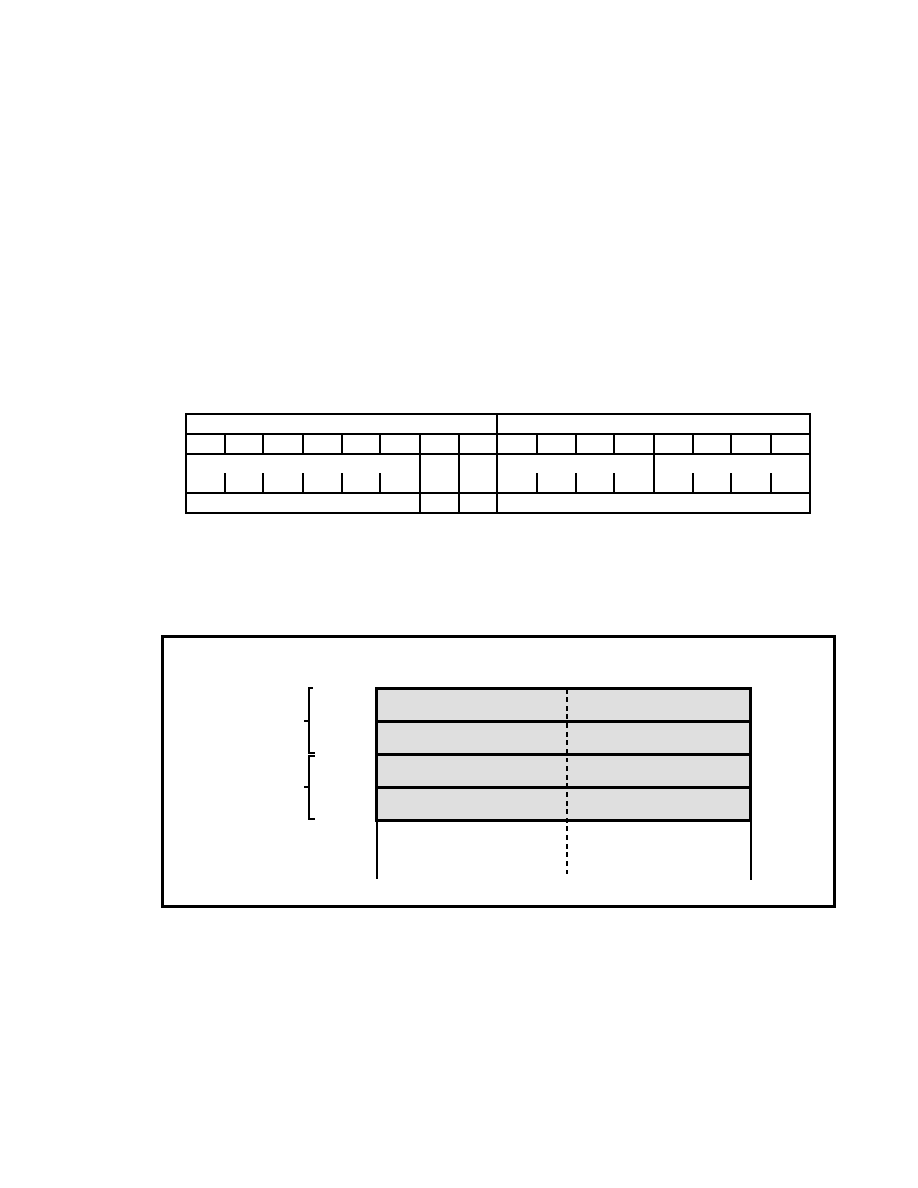

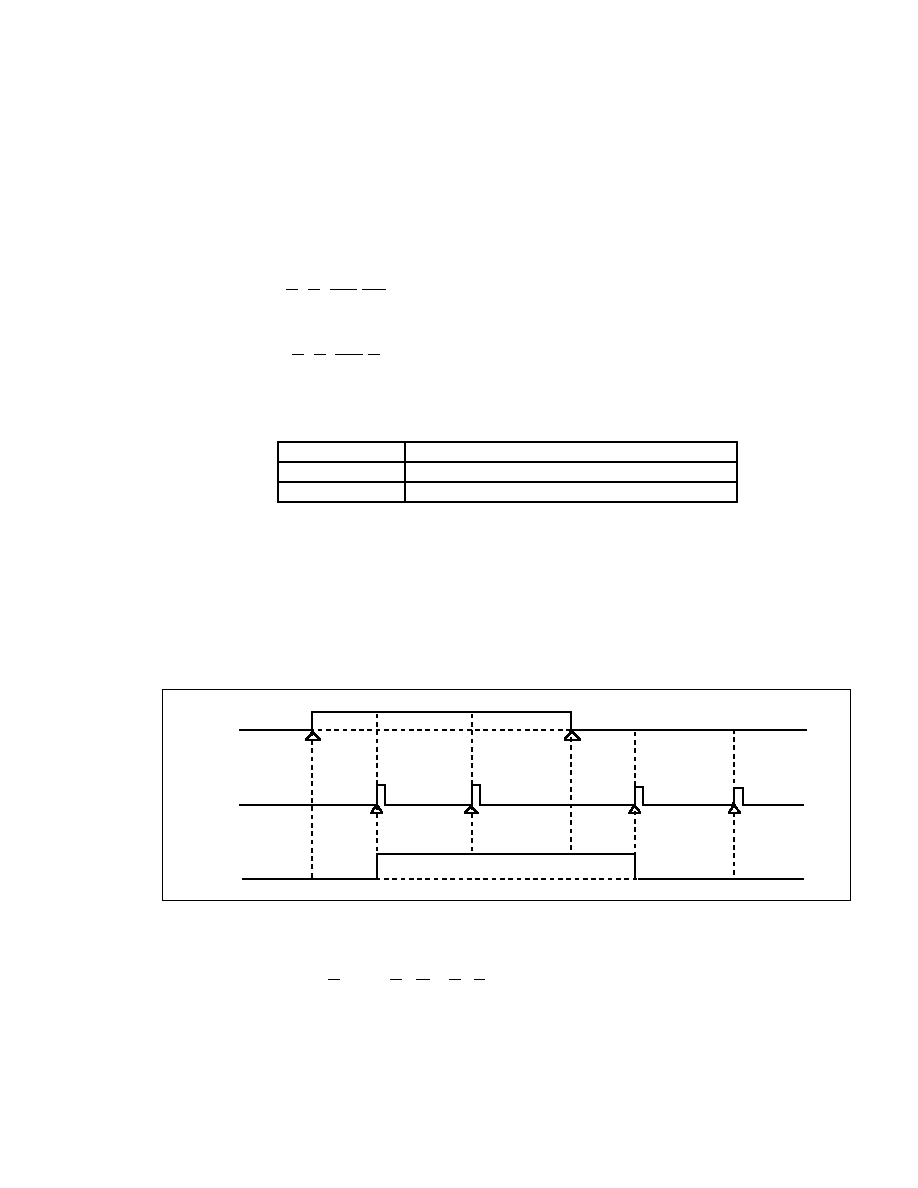

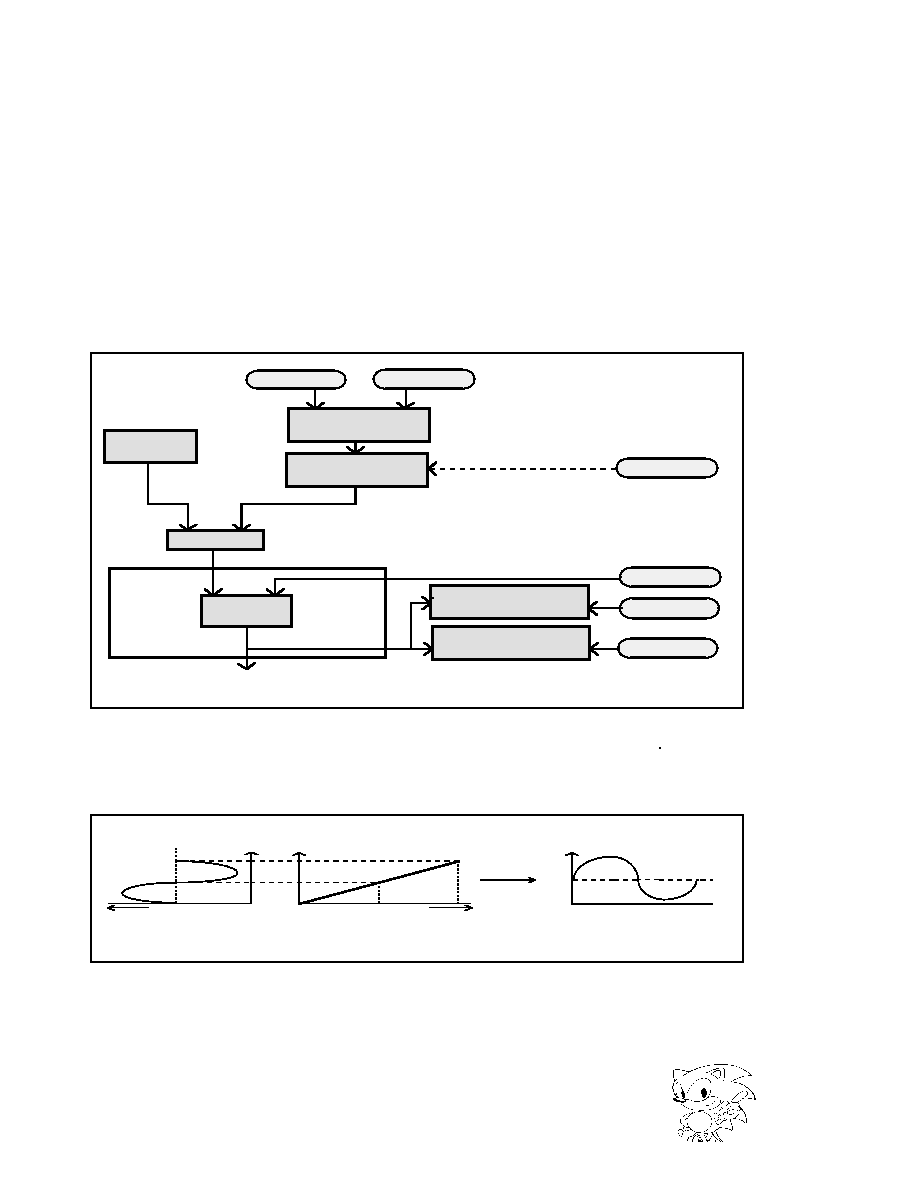

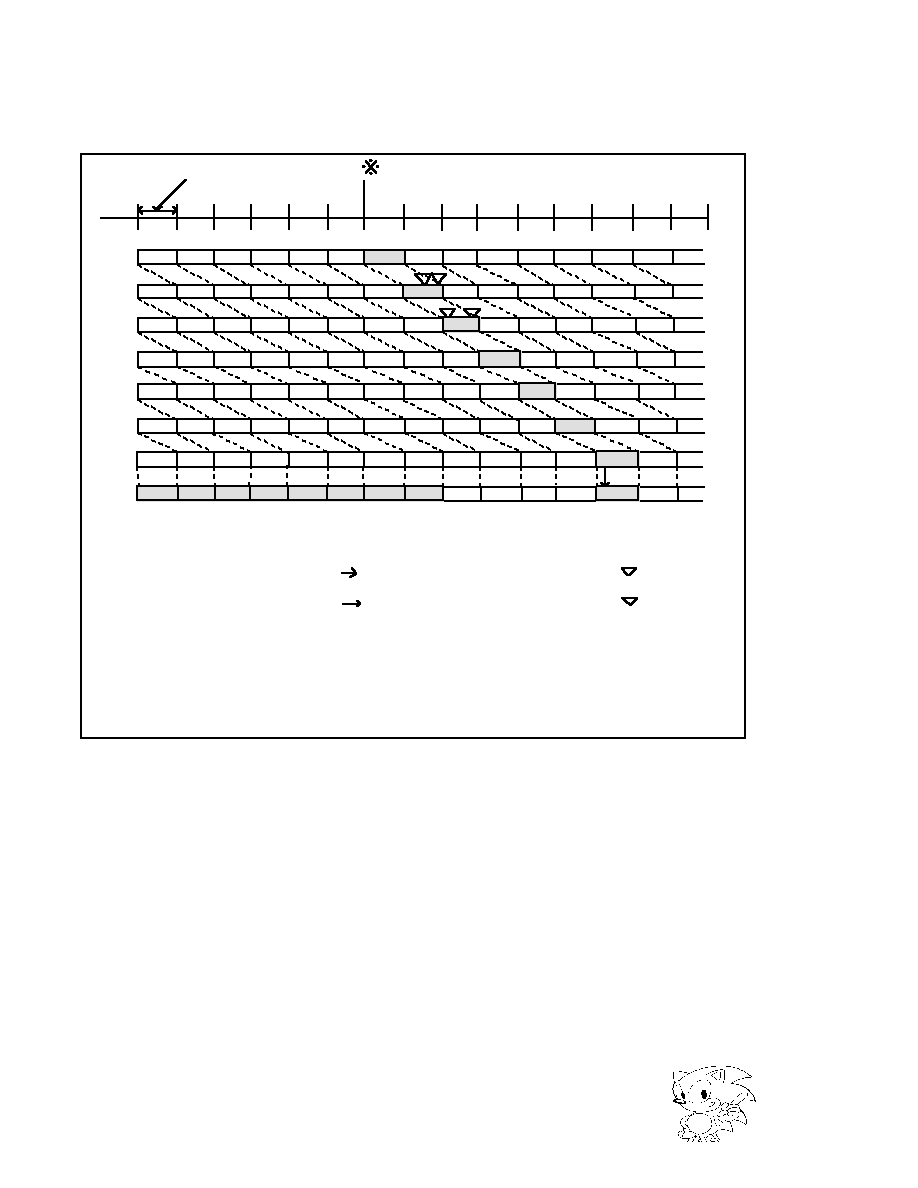

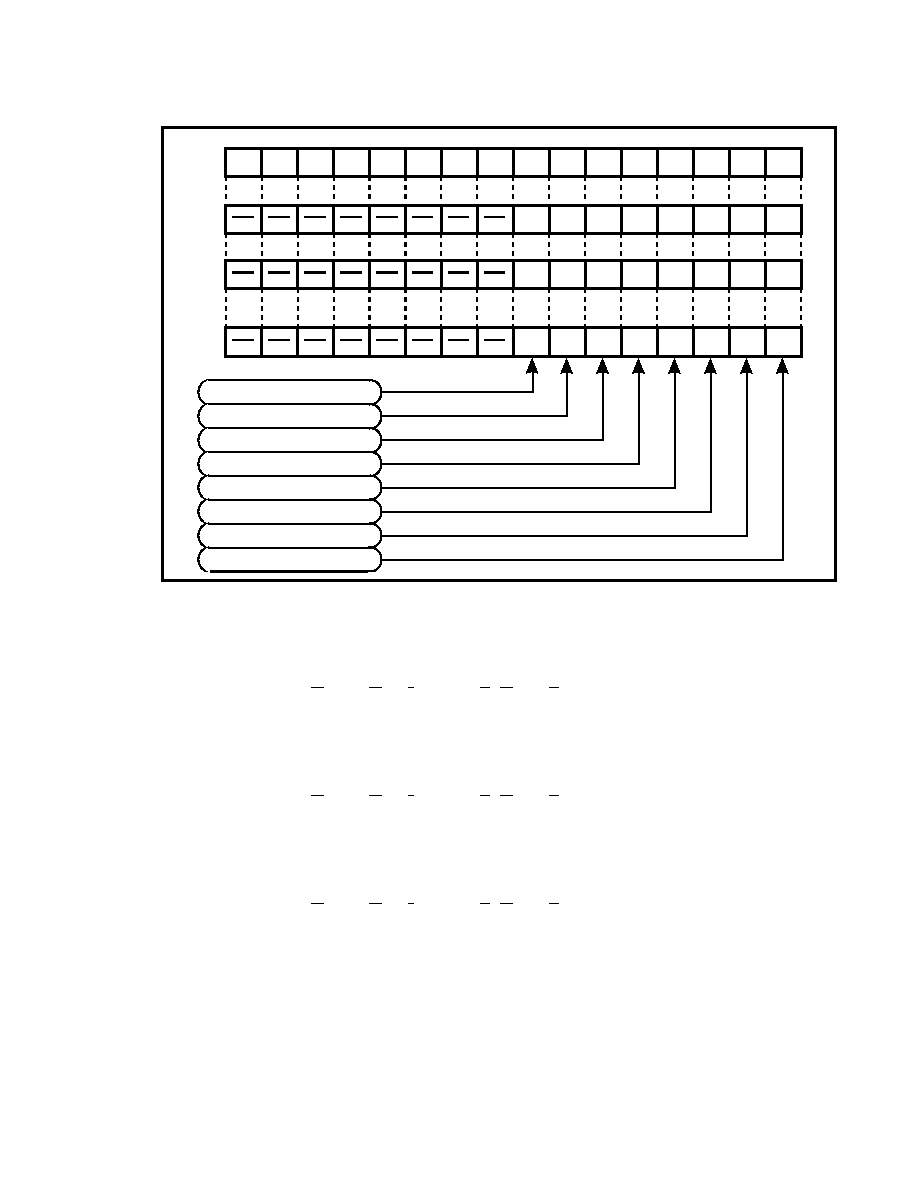

3.2 Memory Access Control

When accessing sound memory from the SCSP, the following priorities are main-

tained.

1. PCM Data Read by PCM sound generator, accessed by DSP.

2. DRAM refresh cycle.

3. DMA transfer.

4. Access by the main CPU.

5. Access by the sound CPU.

When there is an access request with a high priority, there will be a wait state against

an access request with a low priority. Also, a high priority access request will not

occur while a low priority access is requested because the decision on which device

to be permitted to access memory (PCM sound generator block, DSP block, main

CPU, sound CPU, DMA, etc.) is made before any actual memory access is per-

formed.

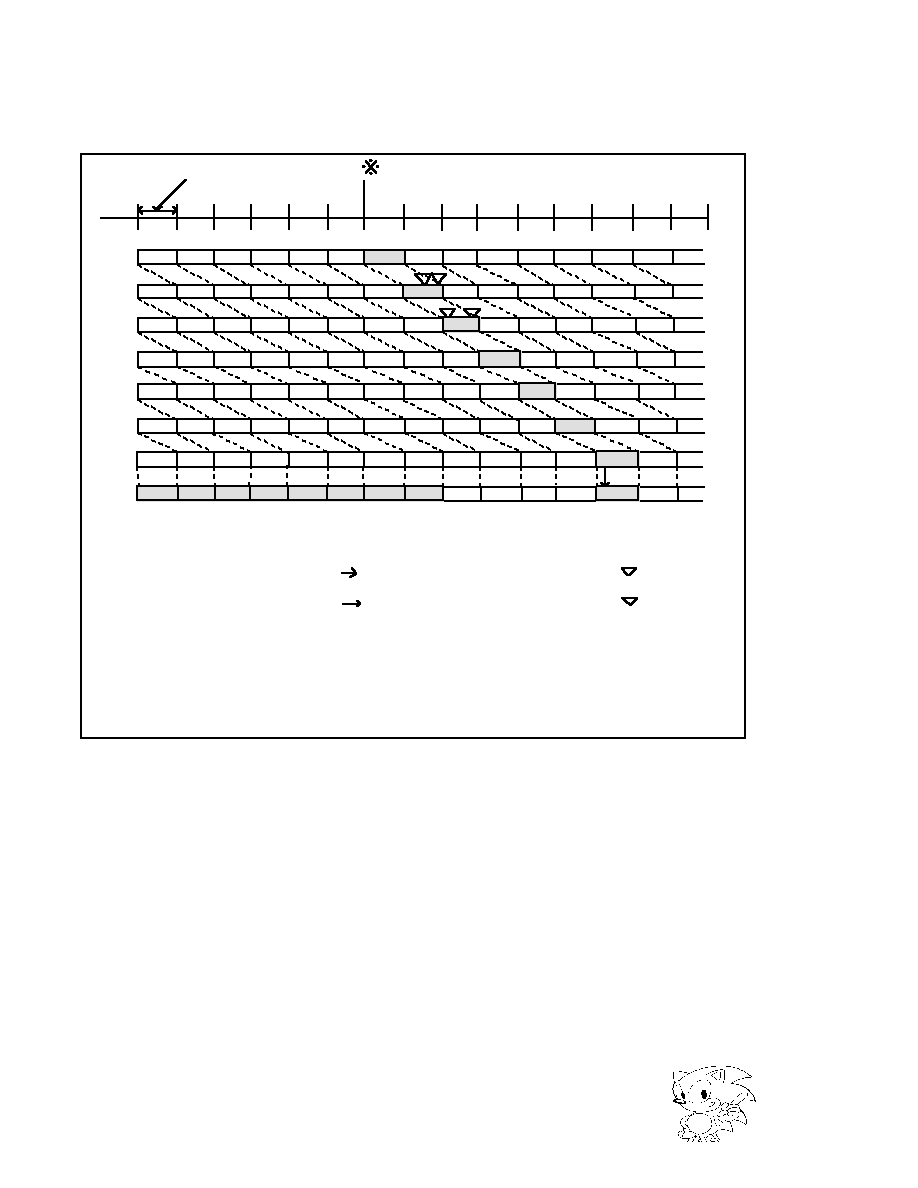

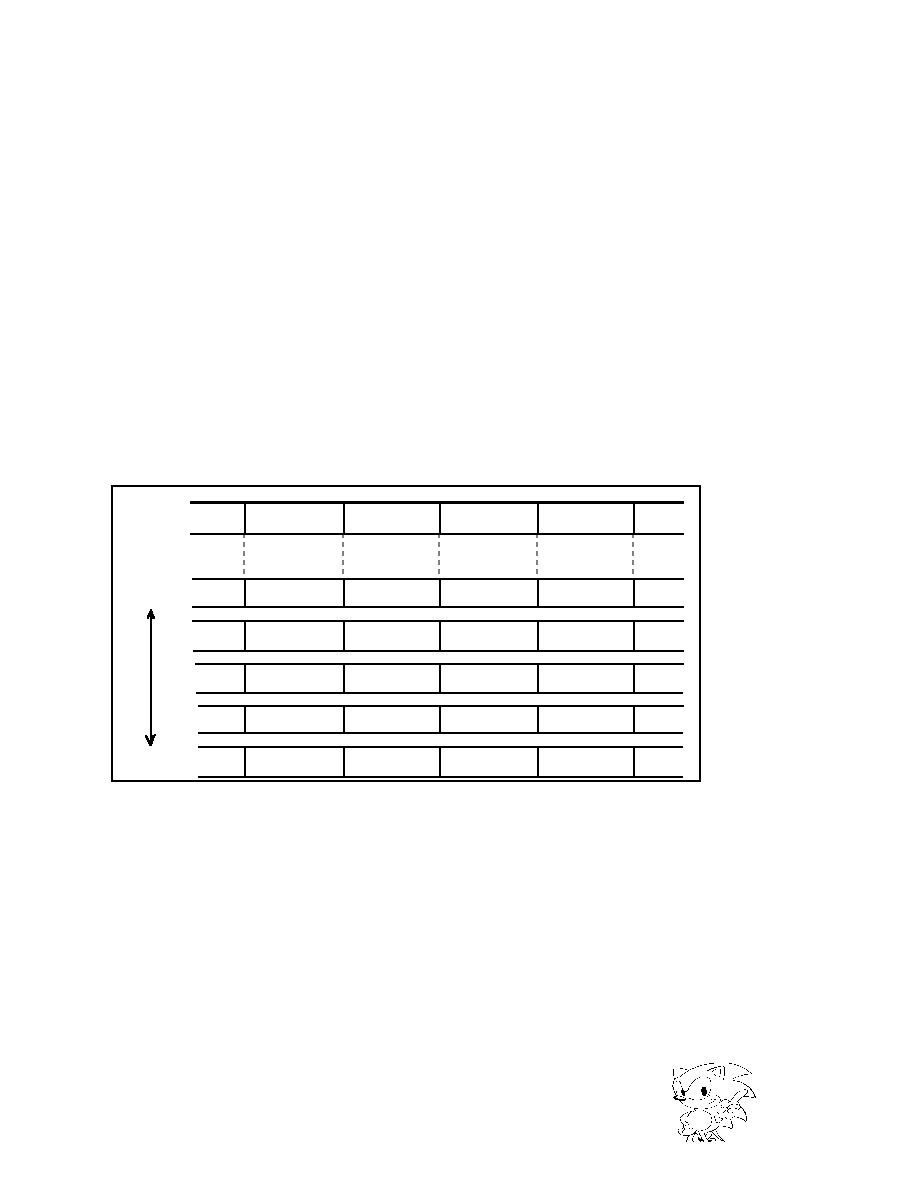

CYCLE 0

CYCLE 1

CYCLE 2

CYCLE 3

High

Low

DSP

PCM

DSP

PCM

Access

Access

Access

Access

Refresh

cycle

Refresh

cycle

Refresh

cycle

Refresh

cycle

DMA

Access

DMA

Access

DMA

Access

DMA

Access

MCPU(SCU)

Access

MCPU(SCU)

Access

MCPU(SCU)

Access

MCPU(SCU)

Access

SCPU

Access

SCPU

Access

SCPU

Access

SCPU

Access

Memory Access

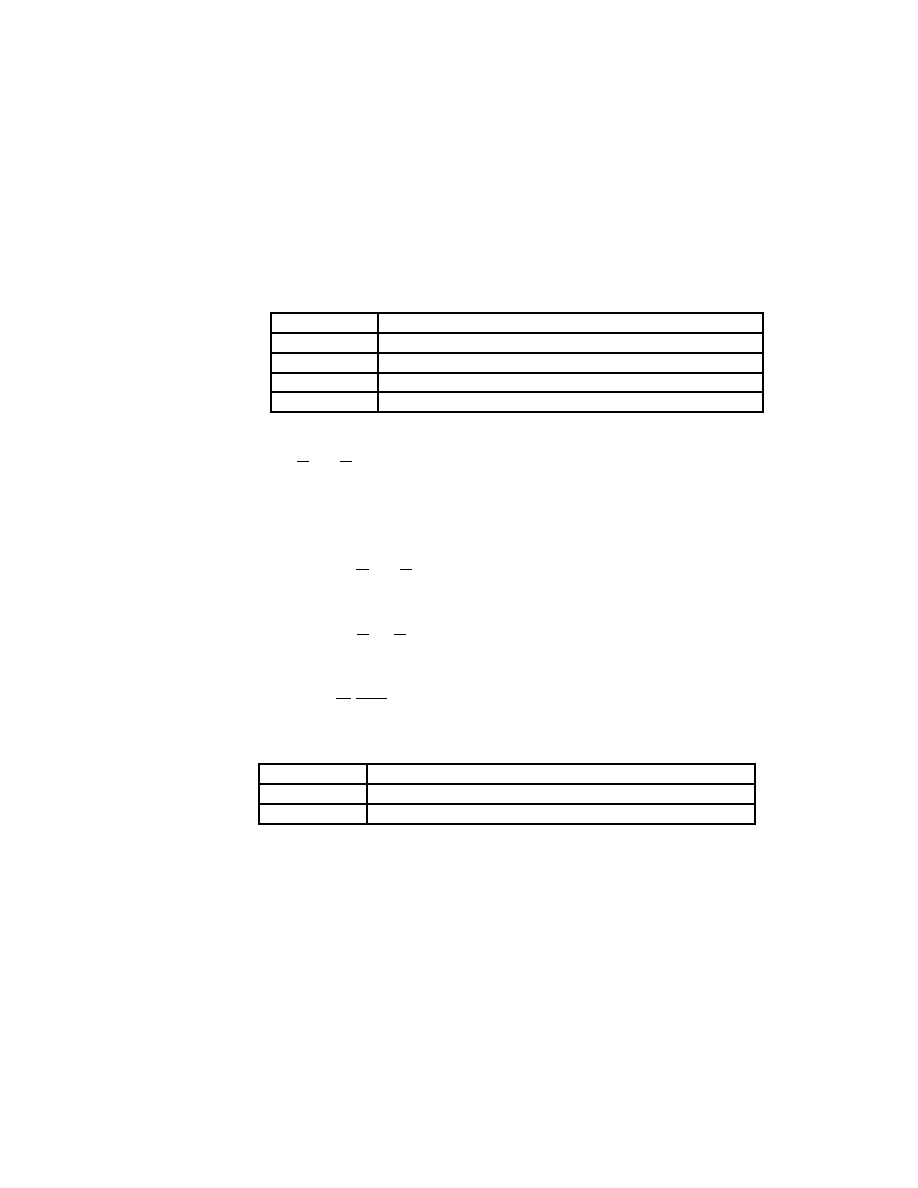

Priority

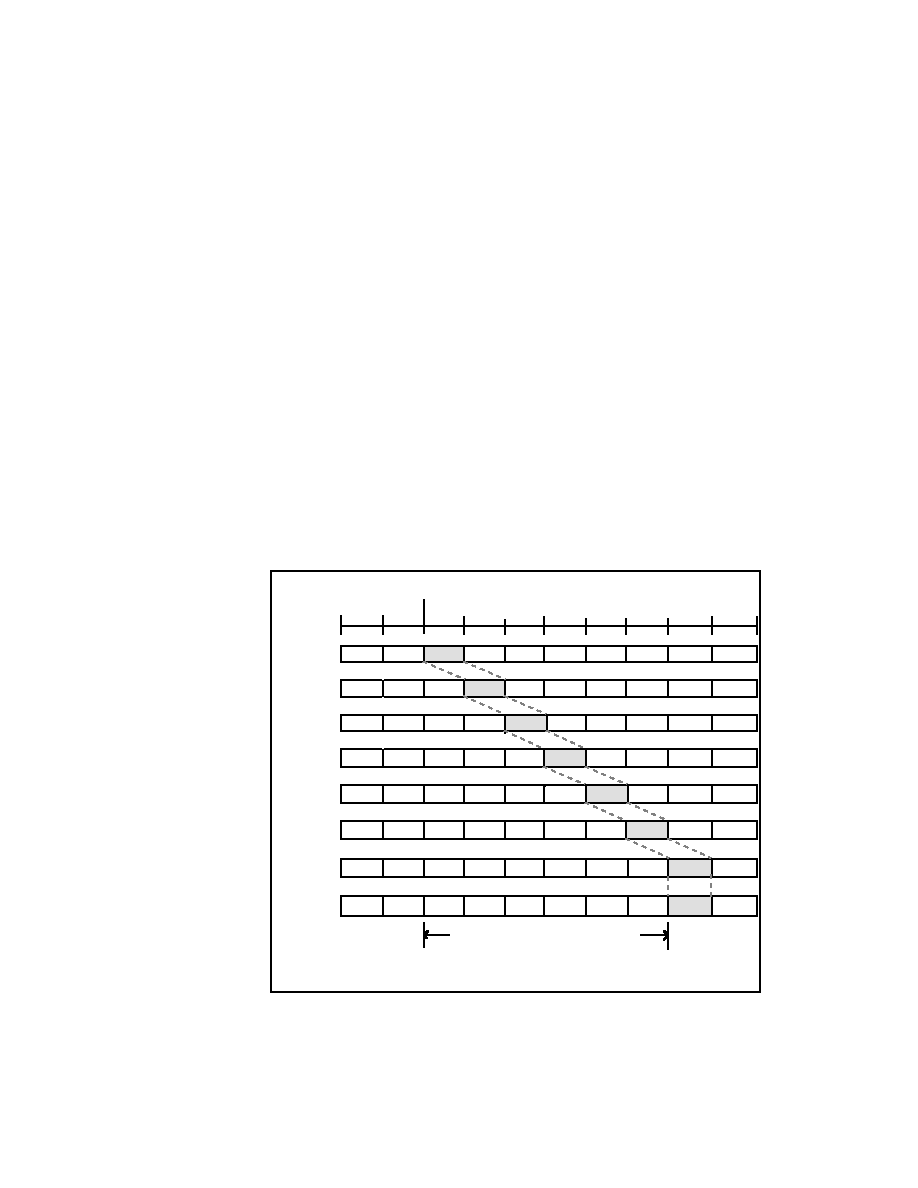

Figure 3.2 Memory Access Priorities

The performance of the SCSP / sound CPU is determined by the distribution of the

memory cycles.

There are 128 memory cycles within one sample (1/44.1K

=

22.68

µ

sec). These 128

cycles are distributed among the various devices. The number of times the CPU

accesses changes with the application, so there is no best way to access memory, but

be aware of the items on the following page.

|

SEGA Confidential

Saturn SCSP User's Manual

21

· Sound memory uses DRAM, so refresh cycles are required. In the Saturn sound

system, two empty cycles are required between each sample, so the number of

memory cycles that can be used by other devices is 126.

· The sound generator and DSP memory cycles have the highest priority memory

cycles.

· The sound generator uses two memory cycles to produce sound from one slot.

With a maximum of 32 slots, a total of 64 times of memory cycle may be used.

When the EG is at the maximum attenuation state ("3FF

H

"), the sound generator

does not access memory. Do KEY_OFF for those slots that are not producing

sound.

· The DSP accesses memory a maximum of 64 times. This changes with the DSP

application. Try to use the internal DSP registers as much as possible when

storing data temporarily.

· The sound CPU operating speed will decrease when using the SCSP built-in

DMA due to the extent of the wait state imposed on the sound CPU.

|

SEGA Confidential

22

|

SEGA Confidential

Saturn SCSP User's Manual

23

Chapter 4

SCSP Register

Chapter 4 Contents

4.1

Register Map

24

4.2

Sound Source Register

34

Loop Control Register

35

EG Register

40

FM Modulation Control Register

46

Using the FM Sound Generator Method

47

Sound Volume Register

72

PITCH Register

73

LFO Register

76

MIXER Register

80

Slot Status Register

89

Sound Memory Structure Register

89

MIDI Register

89

Timer Register

92

Interrupt Control Register

95

DMA Transfer Register

101

4.3

DSP Memory Control Register

103

Chapter 4 Contents

4.1

Register Map ..........................................................

24

4.2

Sound Source Register .......................................... 34

Loop Control Register ............................................ 35

EG Register ............................................................

40

FM Modulation Control Register ............................. 46

Using the FM Sound Generator Method ................ 47

Sound Volume Register ......................................... 72

PITCH Register ......................................................

73

LFO Register ..........................................................

76

MIXER Register .....................................................

80

Slot Status Register ...............................................

89

Sound Memory Structure Register ......................... 89

MIDI Register .........................................................

89

Timer Register ........................................................

92

Interrupt Control Register ....................................... 95

DMA Transfer Register ........................................... 101

4.3

DSP Memory Control Register ............................... 103

|

SEGA Confidential

24

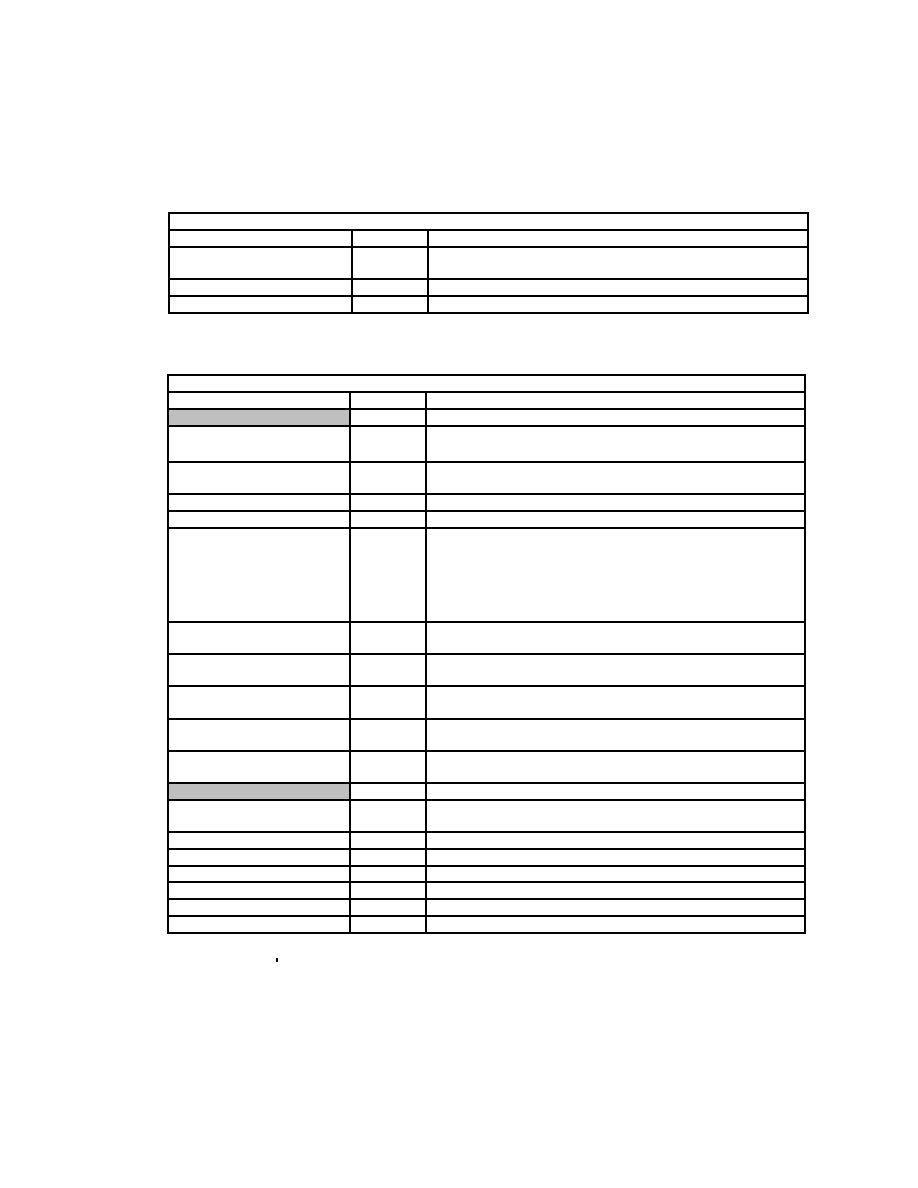

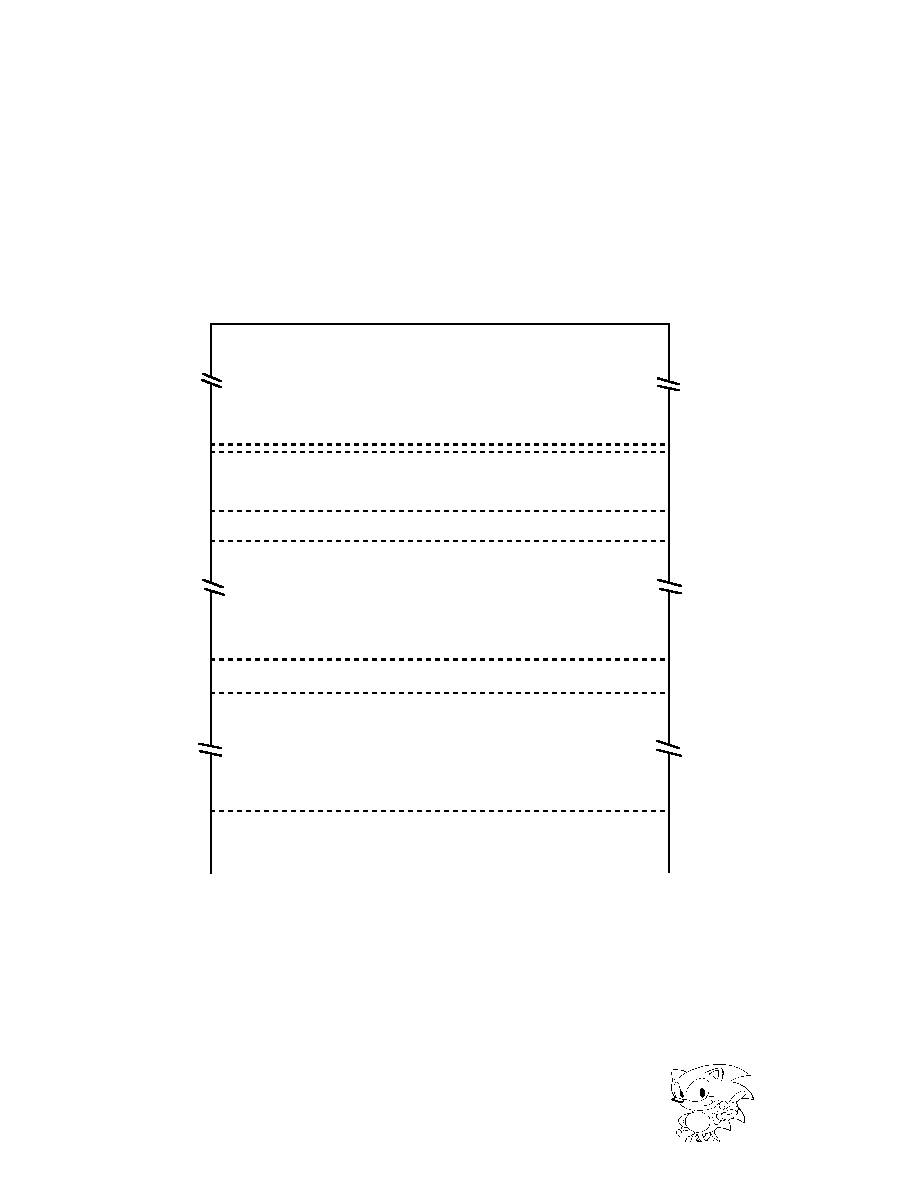

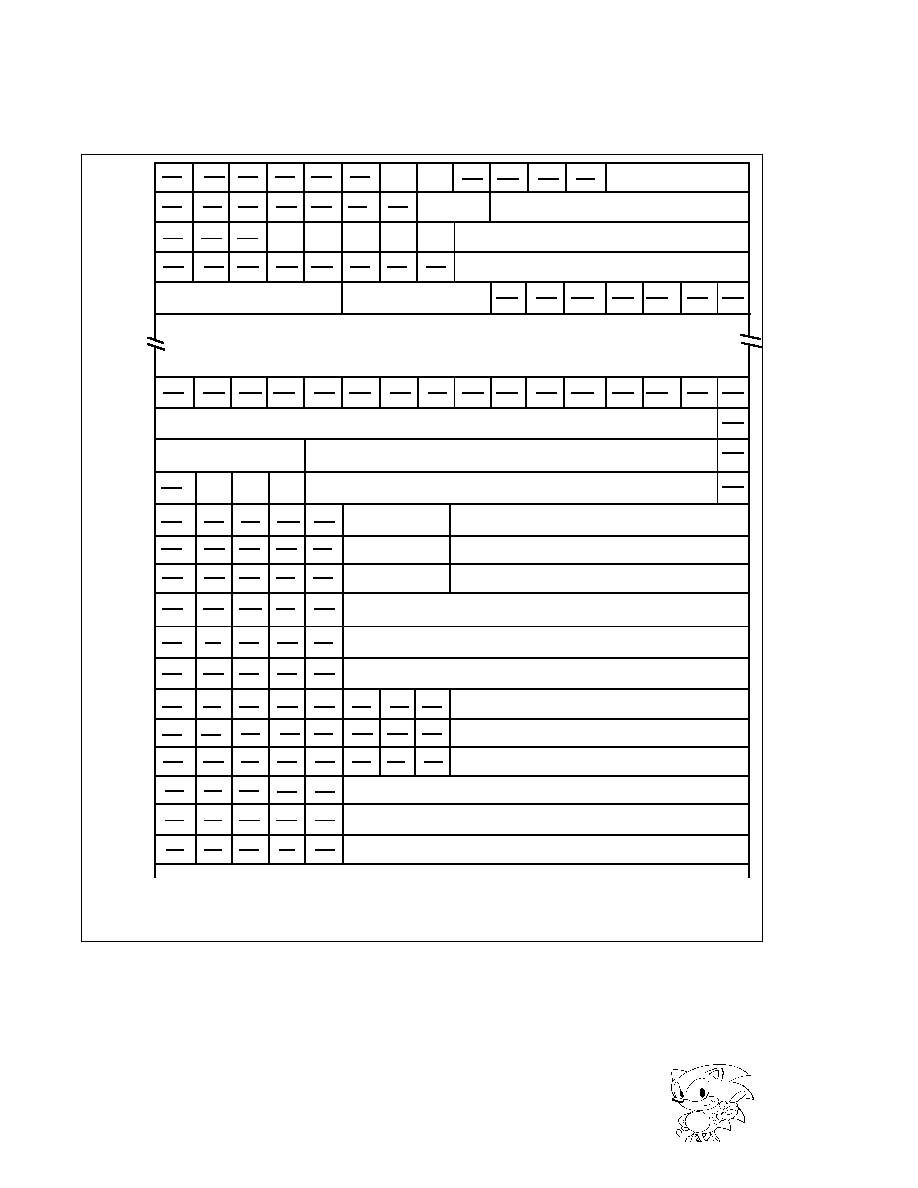

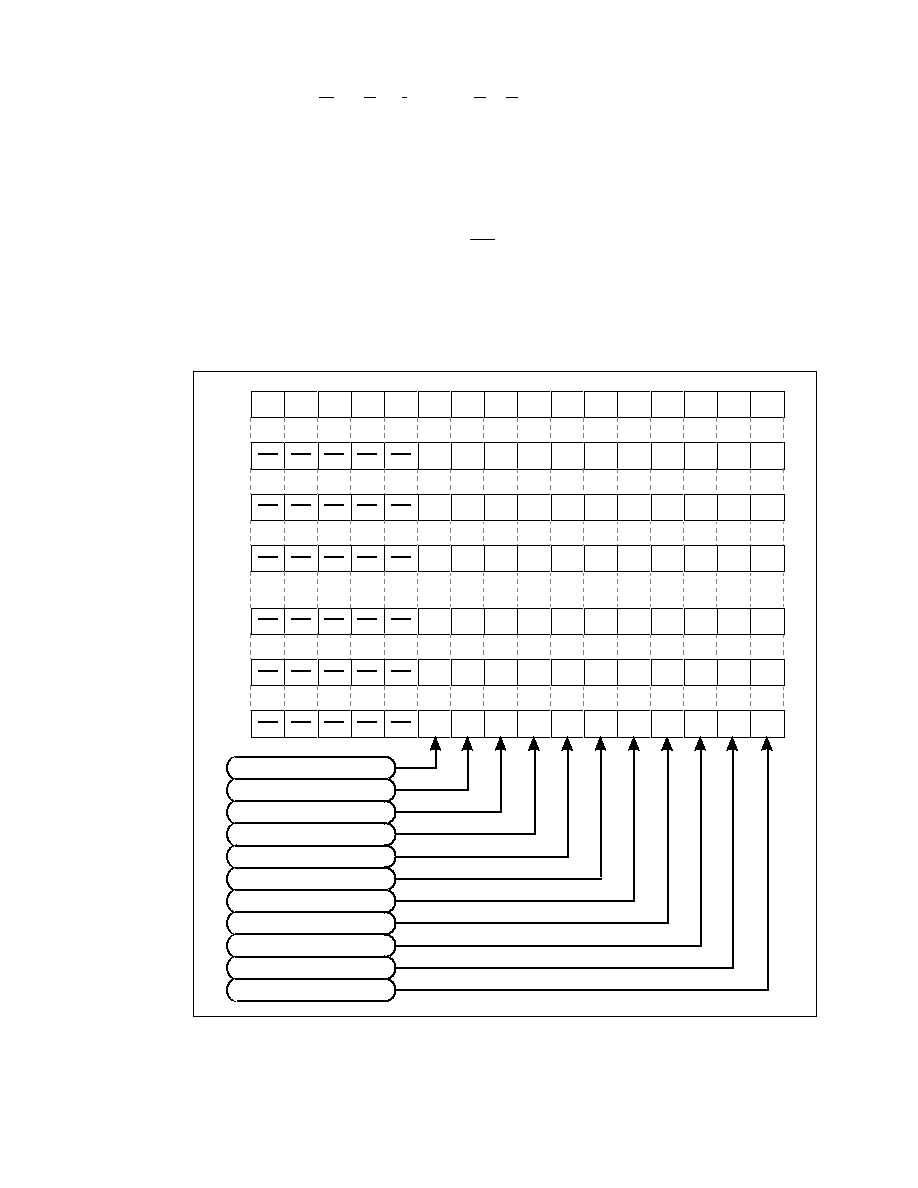

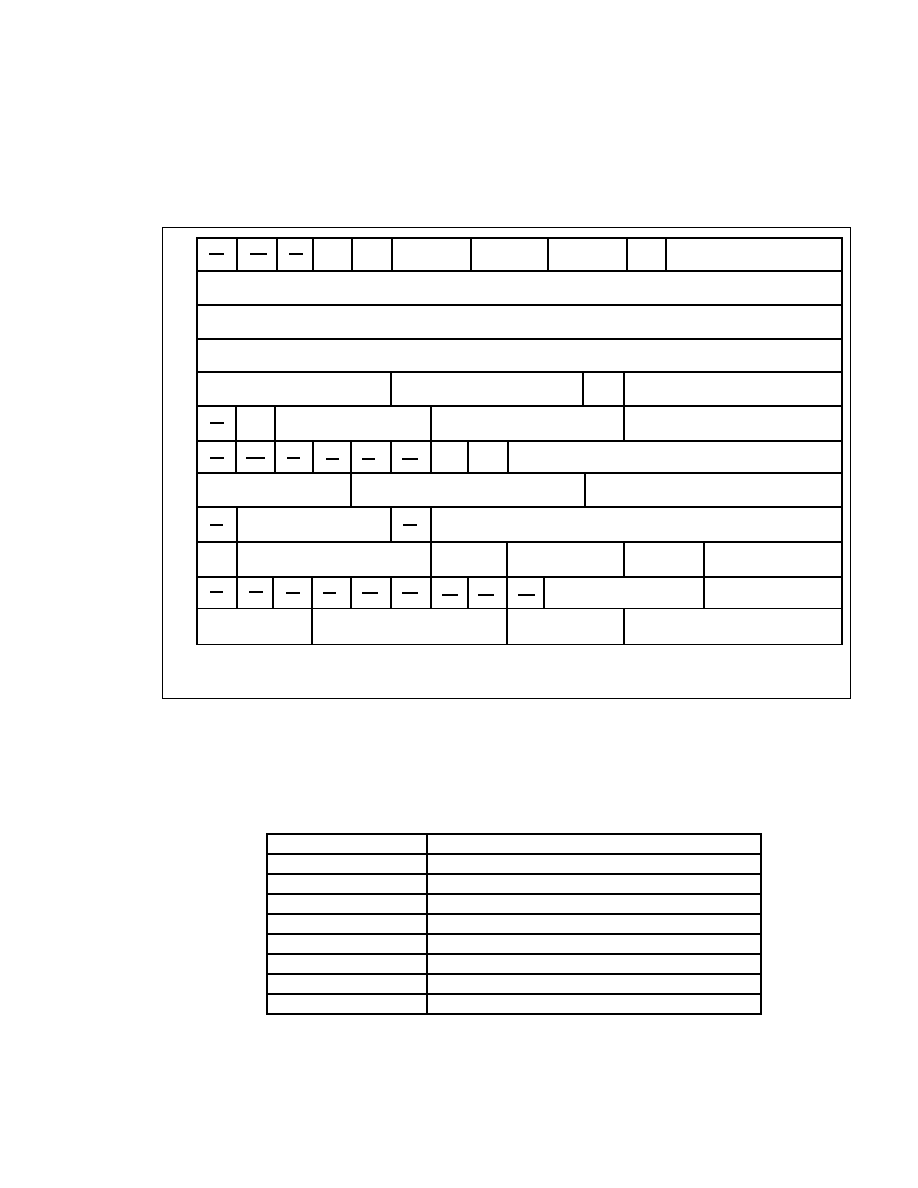

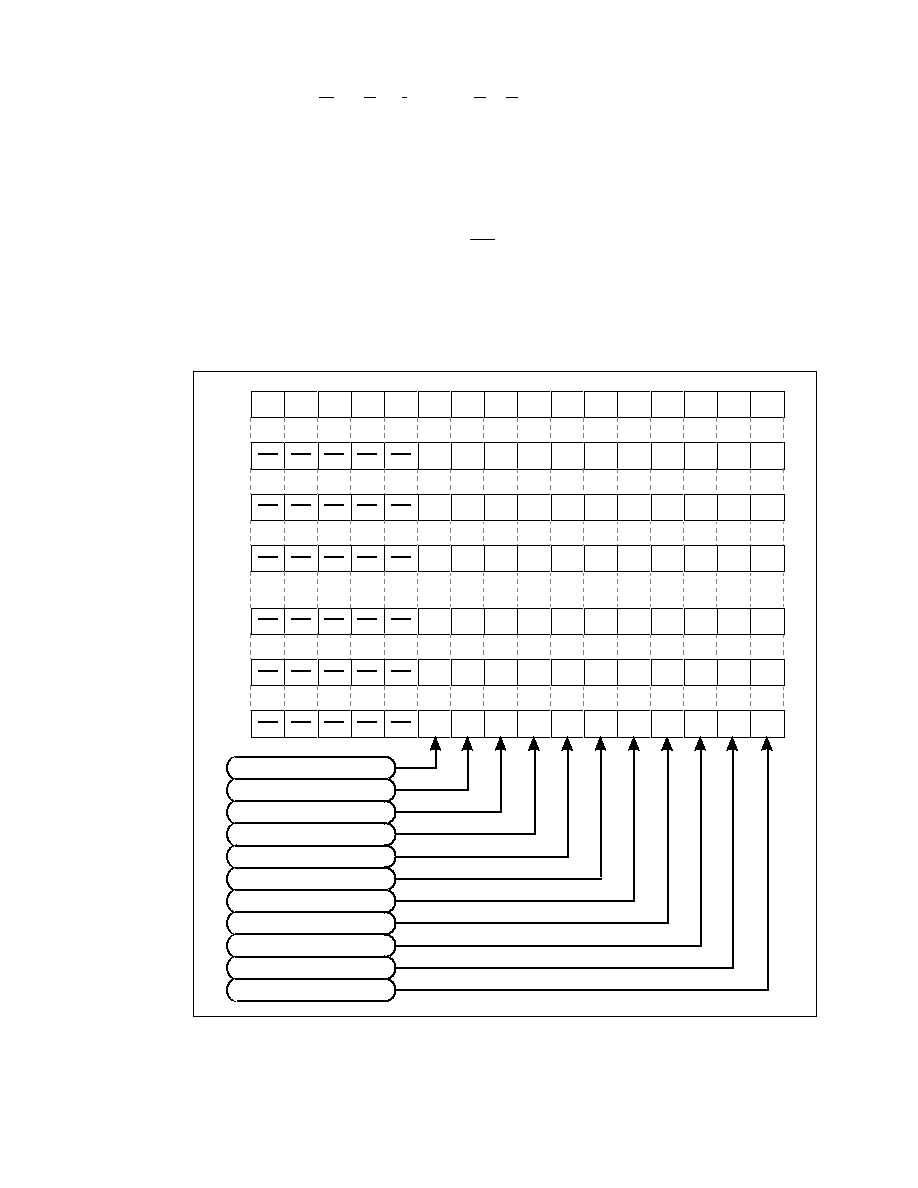

4.1 Register Map

The SCSP carries a wave form calculator unit called SLOT to realize FM sound

mixing.

Figure 4.1 describes the SCSP memory map and the allocation of the individual

registers that make up the memory map.

Individual Slot Control Register

( 5 0 8 W )

SCSP Common Control Register

( 2 4 W )

Sound Data Stack

( 6 4 W )

DSP Control Register

(1 0 1 0 W )

Note) W: Word = 16bit

100EE3

100700

10067F

100600

10042F

100400

1003F8

100000

H

H

H

H

H

H

H

H

Figure 4.1 SCSP Memory Map (1906W)

|

SEGA Confidential

Saturn SCSP User's Manual

25

The individual slot control register represents the allocation of the registers config-

ured in each of the 32 slots (SLOT0~SLOT31).

The location of bit allocation for each register is described as [3 : 0]. For example, SA

[19 : 16] represents the allocation from the 16th bit through the 19th bit of SA.

KX:KYONEX KB:KYONB 8B:PCM8B

HO:EGHOLD LS:LPSLNK SI:STWINH

SD:SDIR RE:LFORE

DISDL[2:0]

DIPAN[4:0]

EFSDL[2:0]

EFPAN[4:0]

ISEL[3:0]

IMXL[2:0]

ALFOS[2:0]

ALFOWS

PLFOS[2:0]

PLFOWS

LFOF[4:0]

RE

OCT[3:0]

FNS[9:0]

MDYSL[5:0]

MDXSL[5:0]

MDL[3:0]

SI

SD

TL[7:0]

RR[4:0]

DL[4:0]

KRS[3:0]

LS

D2R[4:0]

D1R[4:0]

HO

AR[4:0]

LEA[15:0]

LSA[15:0]

SA[15:0]

KX

KB

SBCTL

SSCTL

LPCTL

8B

SA[19:16]

00

18

H

H

Figure 4.2 Individual Slot Control Register

Table 4.1 Individual Slot Control Register (1)

Designation

Contents

KYONEX (KX)

Execute KEY_ON

KYONB (KB)

Record KEY_ON, KEY_OFF

SBCTL

Source bit control

SSCTL

Sound source control

LPCTL

Loop control

PCM8B (8B)

Select wave form data format

SA

Start address

LSA

Loop start address

|

SEGA Confidential

26

Table 4.2 Individual Slot Control Register (2)

LEA

Loop end address

D2R

Decay 2 rate

D1R

Decay 1 rate

EGHOLD (HO)

EG hold mode

AR

Attack rate

LPSLNK (LS)

Loop start link

KRS

Key rate scaling

DL

Decay level

RR

Release rate

STWINH (SI)

Stack write inhibit

SDIR (SD)

Sound direct

TL

Total level

MDL

Modulation level

MDXSL

Select modulation input X

MDYSL

Select modulation input Y

OCT

Octave

FNS

Frequency number switch

LFORE (RE)

LFO reset

LFOF

LFO frequency

PLFOWS

Select LFO frequency modulation wave form

PLFOS

LFO frequency modulation level

ALFOWS

Select LFO amplitude modulation wave form

ALFOS

LFO amplitude modulation level

ISEL

Input select

IMXL

Input mix level

DISDL

Direct data send level

DIPAN

Direct data, fixed position

EFSDL

Effect data send level

EFPAN

Effect data, fixed position

|

SEGA Confidential

Saturn SCSP User's Manual

27

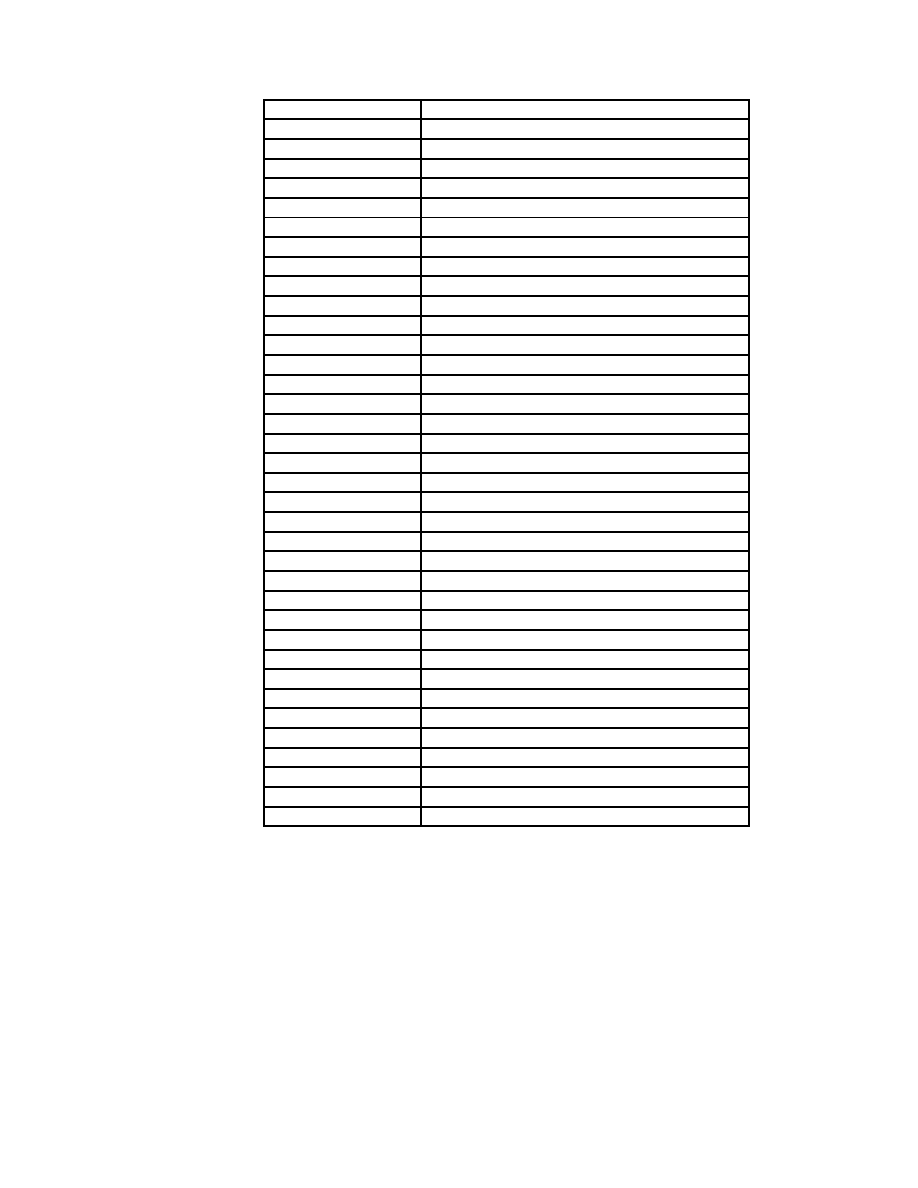

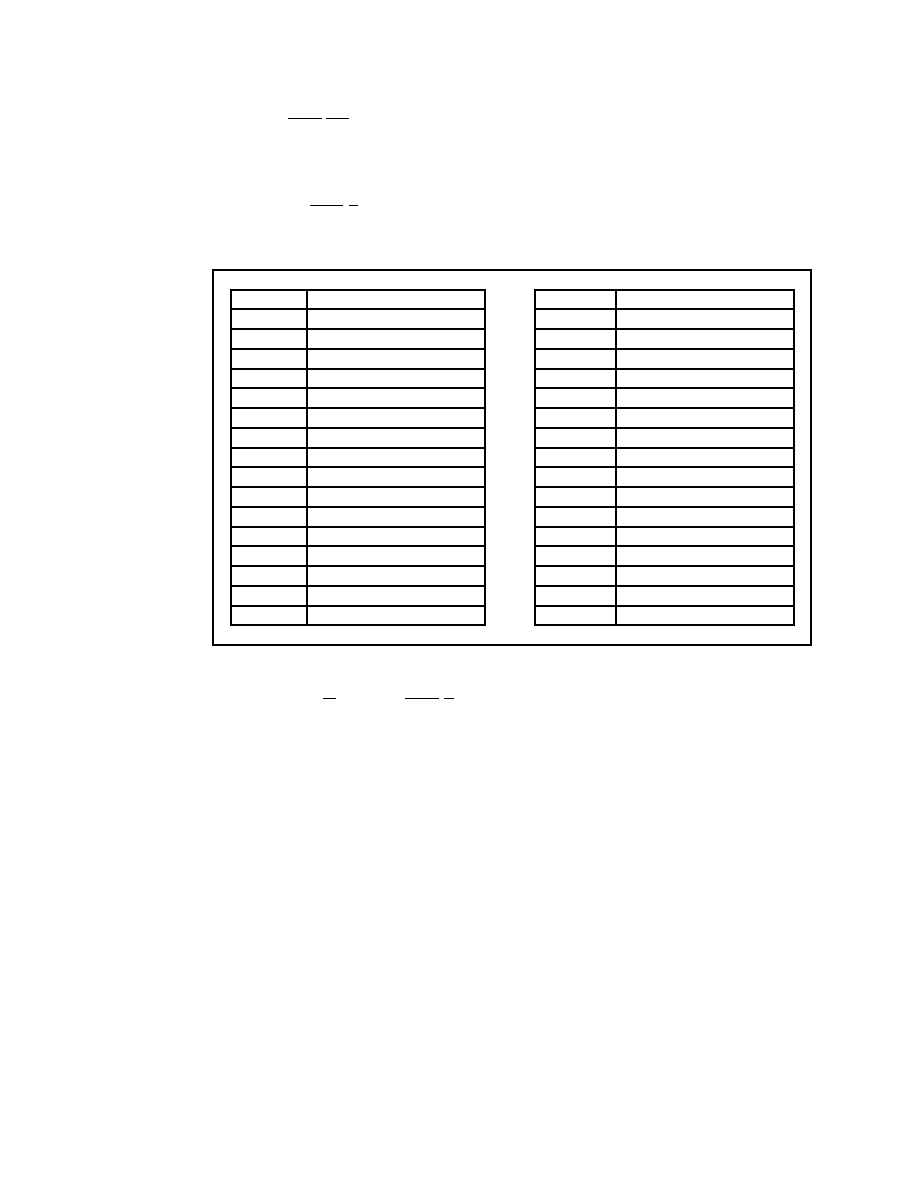

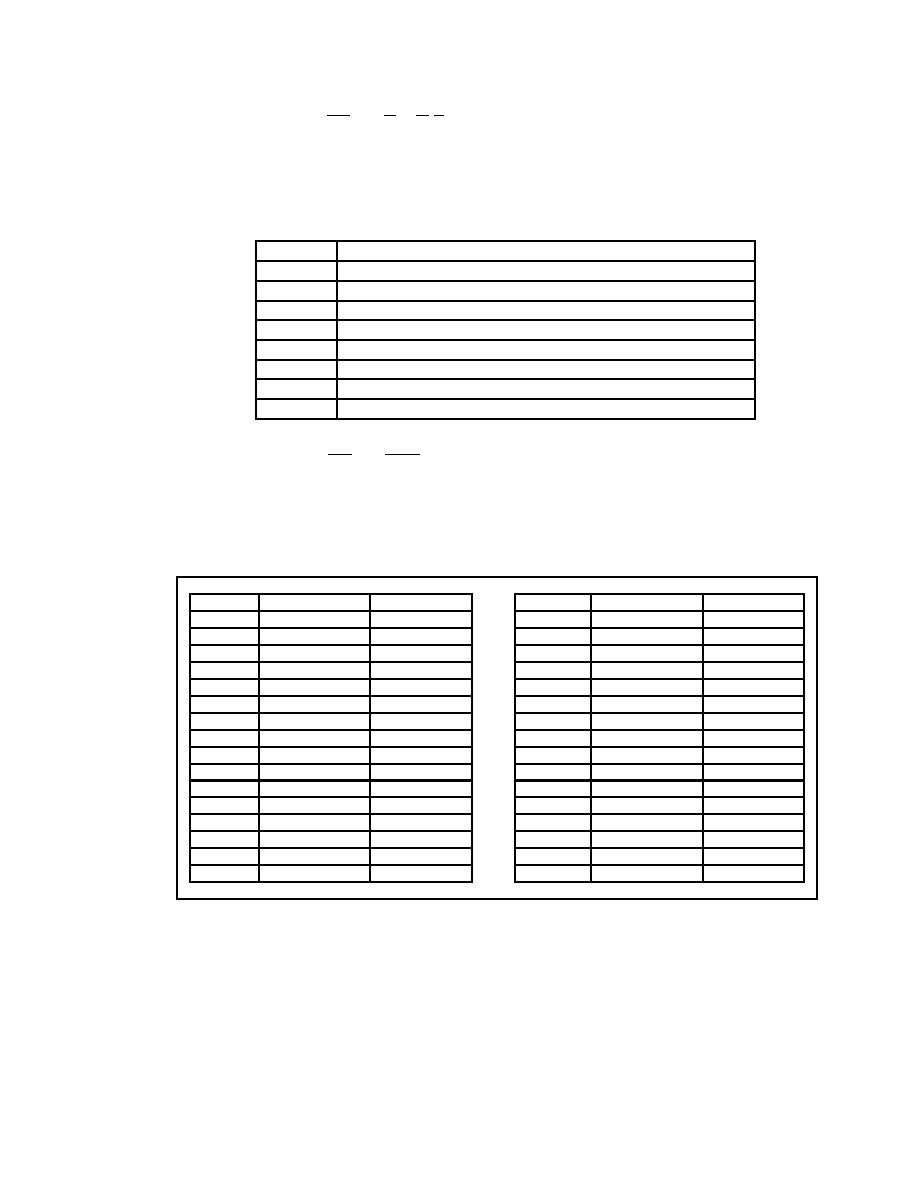

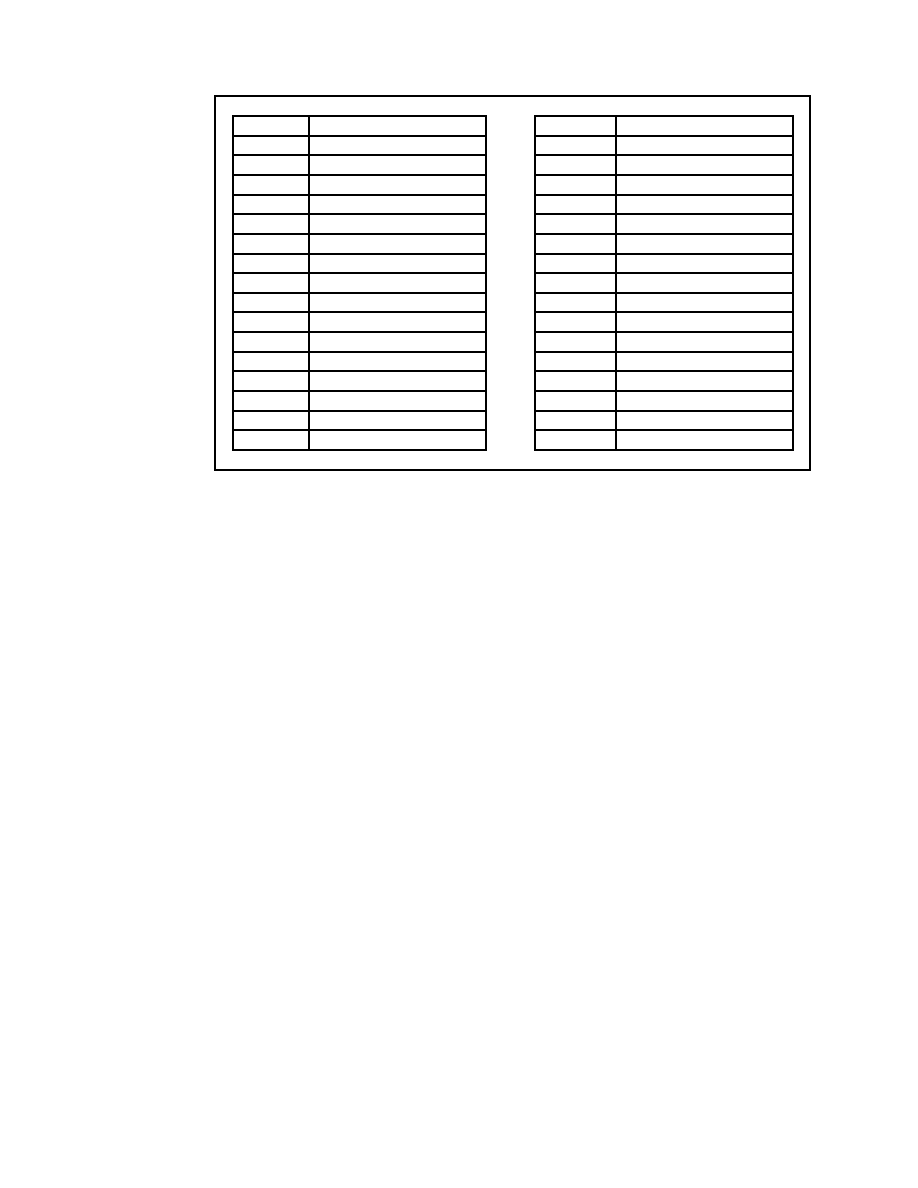

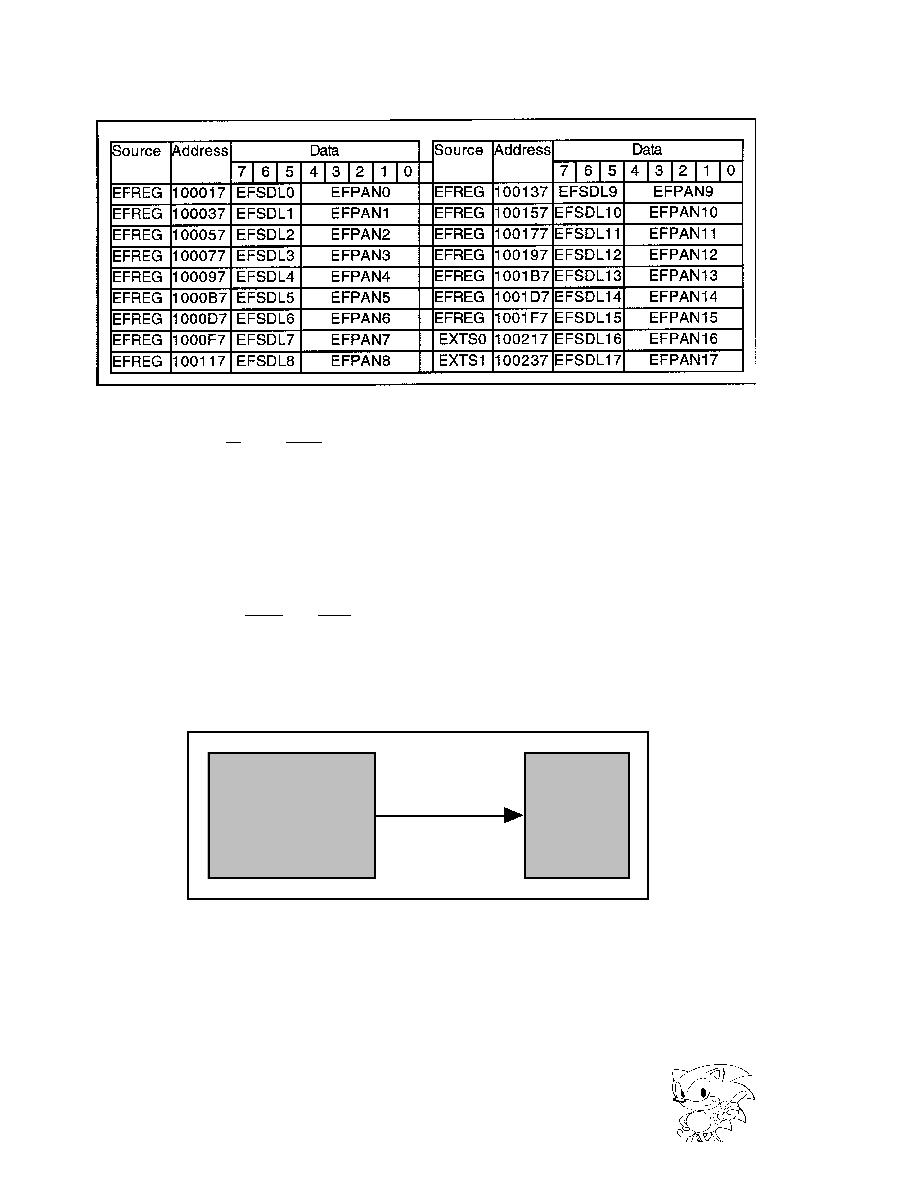

Table 4.3 Individual Slot Control Register Address Map

Slot

Address

Slot

Address

0

100000

H

~ 100017

H

16

100200

H

~ 100217

H

1

100020

H

~ 100037

H

17

100220

H

~ 100237

H

2

100040

H

~ 100057

H

18

100240

H

~ 100257

H

3

100060

H

~ 100077

H

19

100260

H

~ 100277

H

4

100080

H

~ 100097

H

20

100280

H

~ 100297

H

5

1000A0

H

~ 1000B7

H

21

1002A0

H

~ 1002B7

H

6

1000C0

H

~ 1000D7

H

22

1002C0

H

~ 1002D7

H

7

1000E0

H

~ 1000F7

H

23

1002E0

H

~ 1002F7

H

8

100100

H

~ 100117

H

24

100300

H

~ 100317

H

9

100120

H

~ 100137

H

25

100320

H

~ 100337

H

10

100140

H

~ 100157

H

26

100340

H

~ 100357

H

11

100160

H

~ 100177

H

27

100360

H

~ 100377

H

12

100180

H

~ 100197

H

27

100380

H

~ 100397

H

13

1001A0

H

~ 1001B7

H

29

1003A0

H

~ 1003B7

H

14

1001C0

H

~ 1001D7

H

30

1003C0

H

~ 1003D7

H

15

1001E0

H

~ 1001F7

H

31

1003E0

H

~ 1003F7

H

|

SEGA Confidential

28

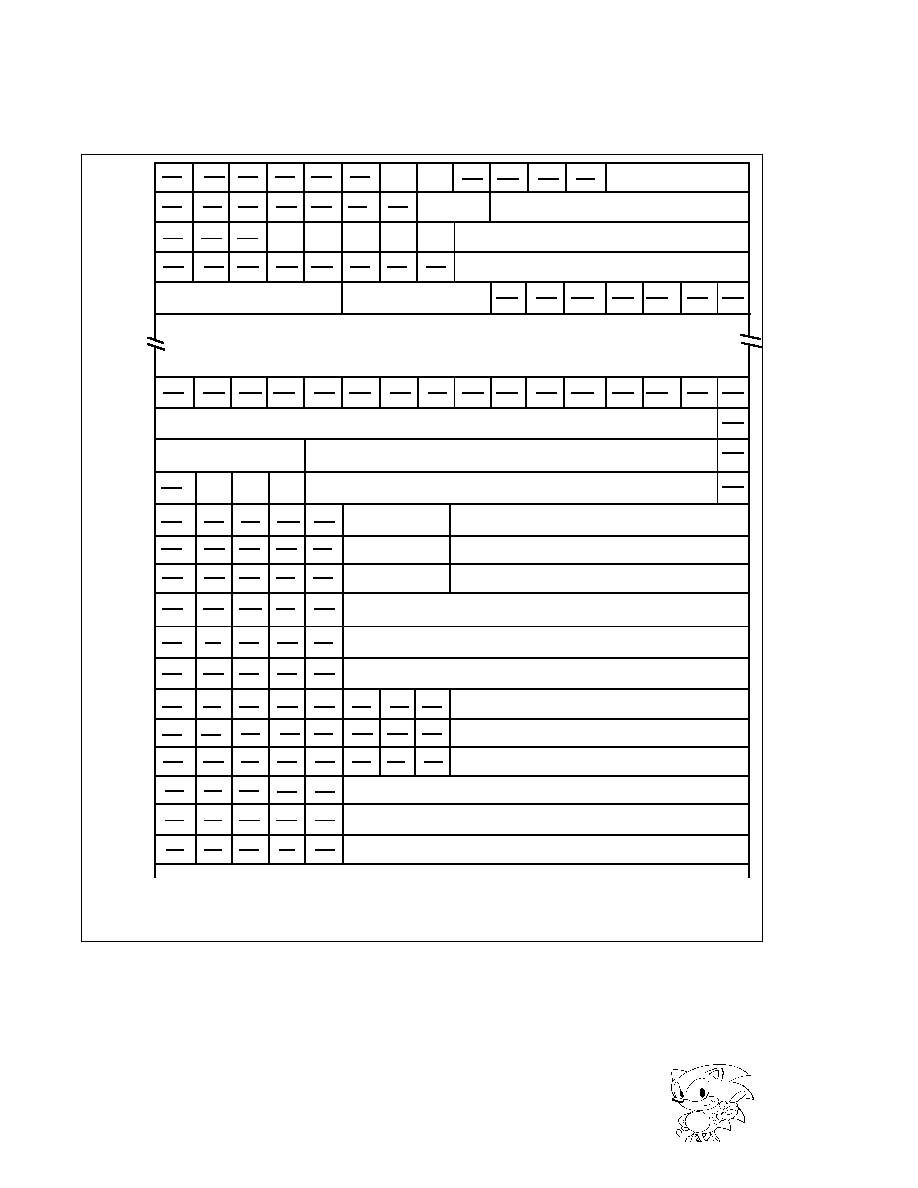

The SCSP control register allocates the interrupt register and timer register, etc., that

are commonly used.

Figure 4.3 SCSP Common Control Register

M4 DB MVOL[3:0]

RBL RBP[19:13]

OF OE IO IF IE MIBUF[7:0]

MOBUF[7:0]

DMEA[15:1]

DMEA[19:16] DRGA[11:1]

GA DI EX DTLG[11:1]

TACTL[2:0] TIMA[7:0]

TBCTL[2:0] TIMB[7:0]

TCCTL[2:0] TIMC[7:0]

SCIEB[10:0]

SCIPD[10:0]

SCIRE[10:0]

SCILV0[7:0]

SCILV1[7:0]

SCILV2[7:0]

MCIEB[10:0]

MCIPD[10:0]

MCIRE[10:0]

M4:MEM4MB DB:DAC18B OF:MOFULL

OE:MOEMP IO:MIOVF IF:MIFULL

IE:MIEMP GA:DGATE DI:DDIR

EX:DEXE

10042F

100430

H

H

10040F

100410

100409

10040A

100400

H

H

H

H

H

MSLC[4:0]

CA[3.0]

|

SEGA Confidential

Saturn SCSP User's Manual

29

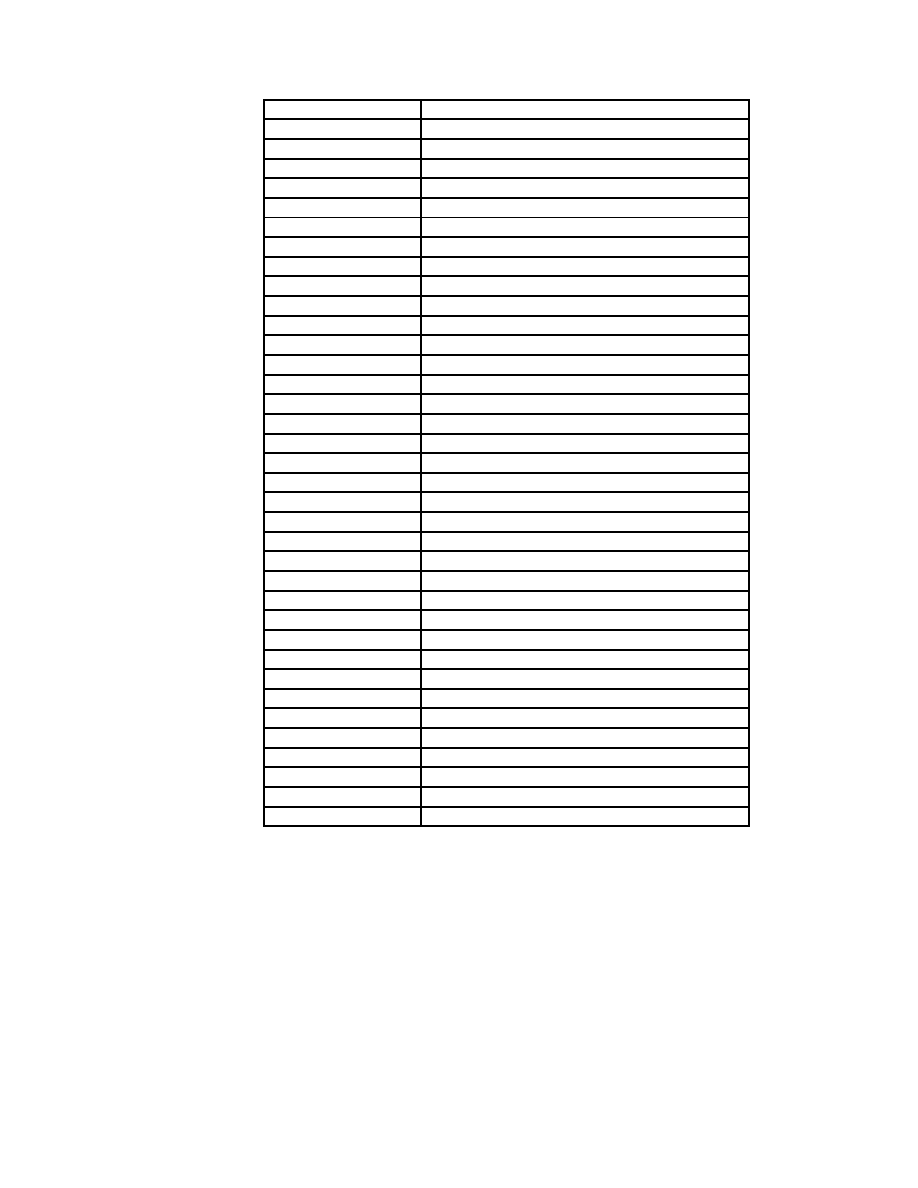

Table 4.4 SCSP Common Control Register

Designation

Contents

MEM4MB (M4)

Memory size designation

DAC18B (DB)

Use the 18 bit D/A converter on the digital output

VER

Version number

MVOL

Master volume

RBL

Ring buffer length

RBP

Ring buffer lead address

MOFULL (OF)

Output FIFO is full

MOEMP (OE)

Output FIFO is empty

MIOVF (IO)

Input FIFO overflow

MIFULL (IF)

Input FIFO full

MIEMP (IE)

Input FIFO empty

MIBUF

MIDI input data buffer

MOBUF

MIDI output data buffer

MSLC

Monitor Slot

CA

Call Address

DMEA

DMA transfer start memory address

DRGA

DMA transfer start register address

DGATE (GA)

DMA transfer gate 0 clear

DDIR (DI)

DMA transfer direction

DEXE (EX)

DMA transfer start

DTLG

DMA transfer data count

TACTL

Timer A pre-scaler control

TIMA

Timer A count data

TBCTL

Timer B pre-scaler control

TIMB

Timer B count data

TCCTL

Timer C pre-scaler control

TIMC

Timer C count data

SCIEB

Allow sound CPU interrupt

SCIPD

Request sound CPU interrupt

SCIRE

Reset sound CPU interrupt

SCILV0

Sound CPU interrupt level bit0

SCILV1

Sound CPU interrupt level bit1

SCILV2

Sound CPU interrupt level bit2

MCIEB

Allow main CPU interrupt

MCIPD

Request main CPU interrupt

MCIRE

Reset main CPU interrupt

|

SEGA Confidential

30

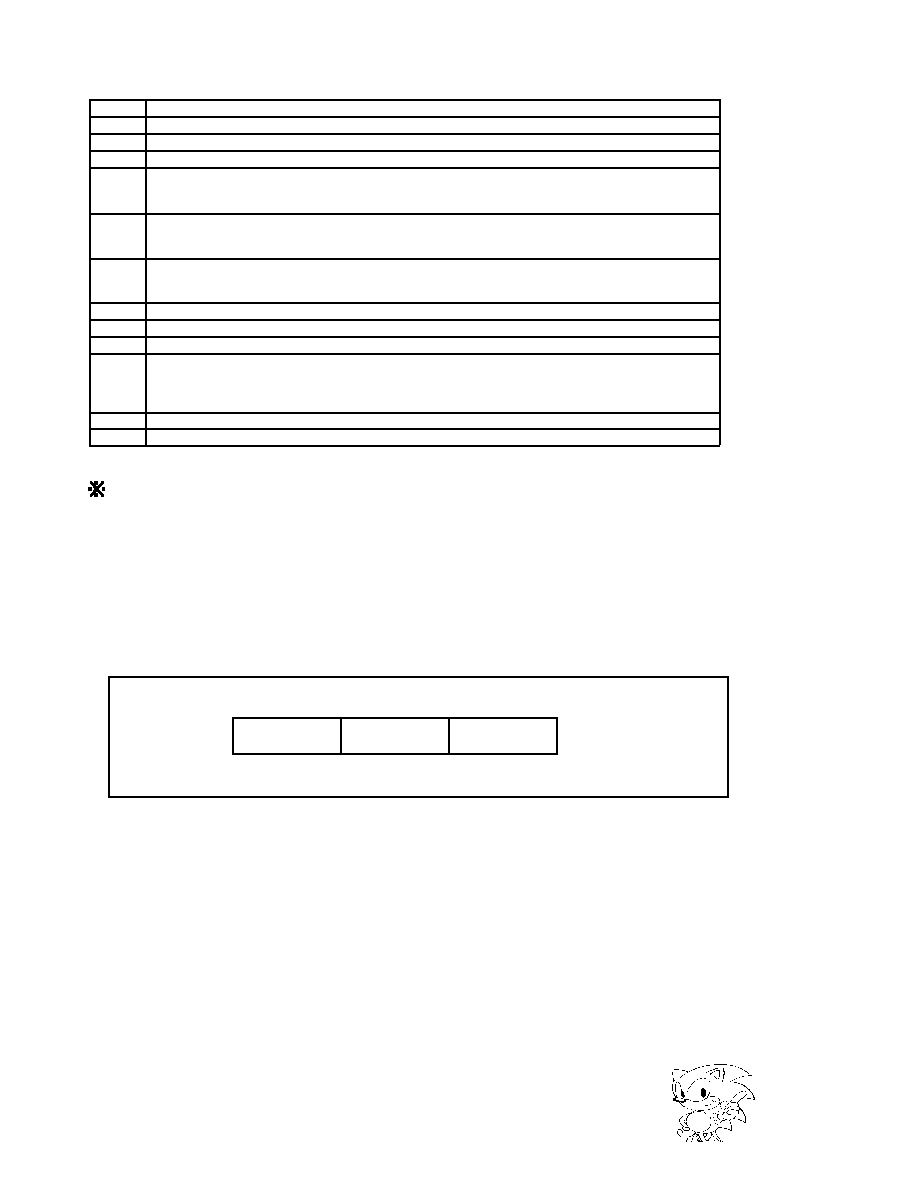

The sound data stack is where sound data is stored. Sound data is in two generation

configuration (GENERATION A and B). Each generation can control up to 32 sound

data.

DIRECT SOUND SLOT DATA STACK (GENERATION A) "SOUS[15:0]"

DIRECT SOUND SLOT DATA STACK (GENERATION A) "SOUS[15:0]"

DIRECT SOUND SLOT DATA STACK (GENERATION B) "SOUS[15:0]"

DIRECT SOUND SLOT DATA STACK (GENERATION B) "SOUS[15:0]"

100600

10063F

100640

10067F

(32W)

(32W)

H

H

H

H

Figure 4.4 Sound Data Stack

Table 4.5 Sound Data Stack

Designation

Contents

SOUS

Sound stack

|

SEGA Confidential

Saturn SCSP User's Manual

31

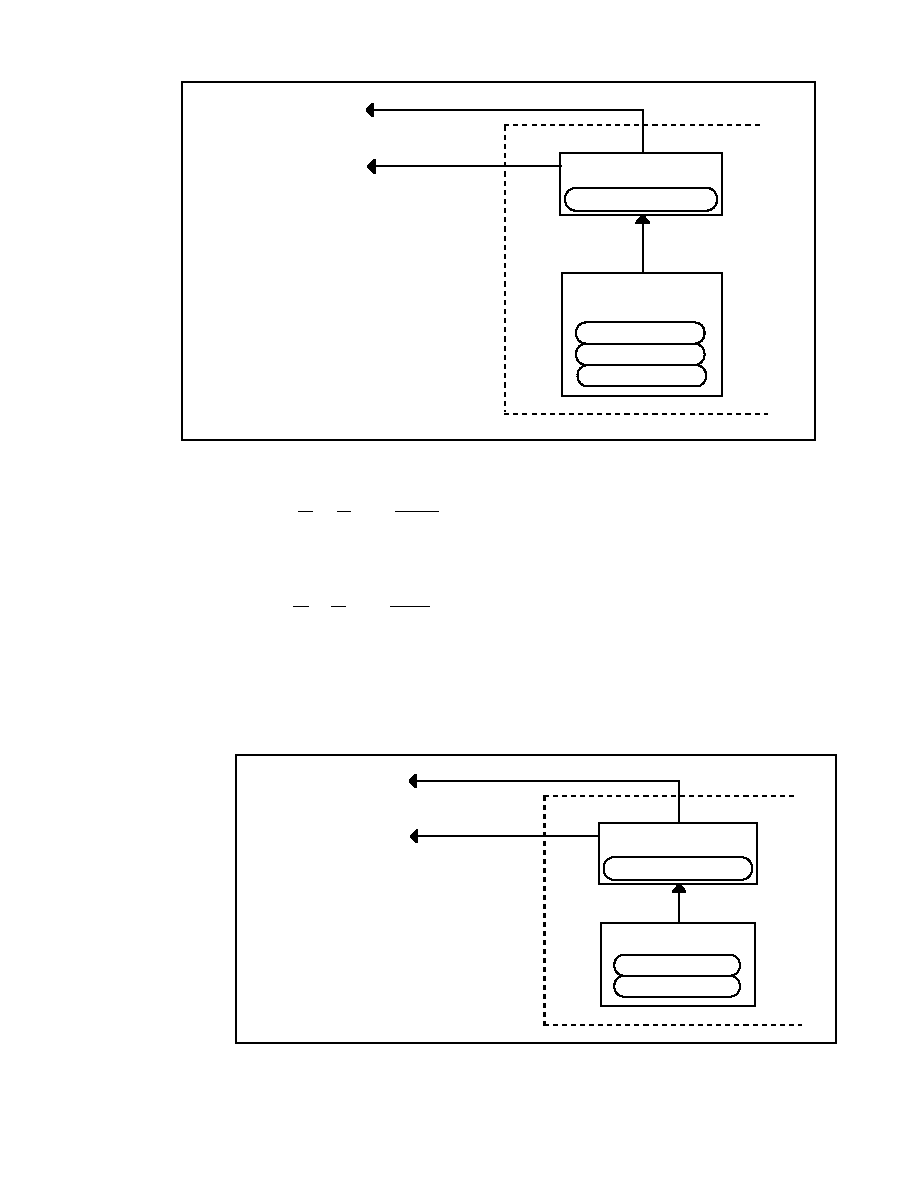

On the DSP control register, the interface block area of DSP is defined which is built

within SCSP.

COEF REG "COEF[12:0]"

O

O

O

O O 0

COEF REG "COEF[12:0]"

MEMORY ADDRESS REG "MADRS[16:1]"

MEMORY ADDRESS REG "MADRS[16:1]"

DSP MICRO PROGRAM

DSP INTERNAL BUFFER

100700

(64W)

10077F

100780

(32W)

1007BF

100800

(512W)

100BFF

100C00

(370W)

100EE3

H

H

H

H

H

H

H

H

Figure 4.5 DSP Control Register

Table 4.6 DSP Control Register

Designation

Contents

COEF

DSP coefficient buffer

MADRS

Memory address register

|

SEGA Confidential

32

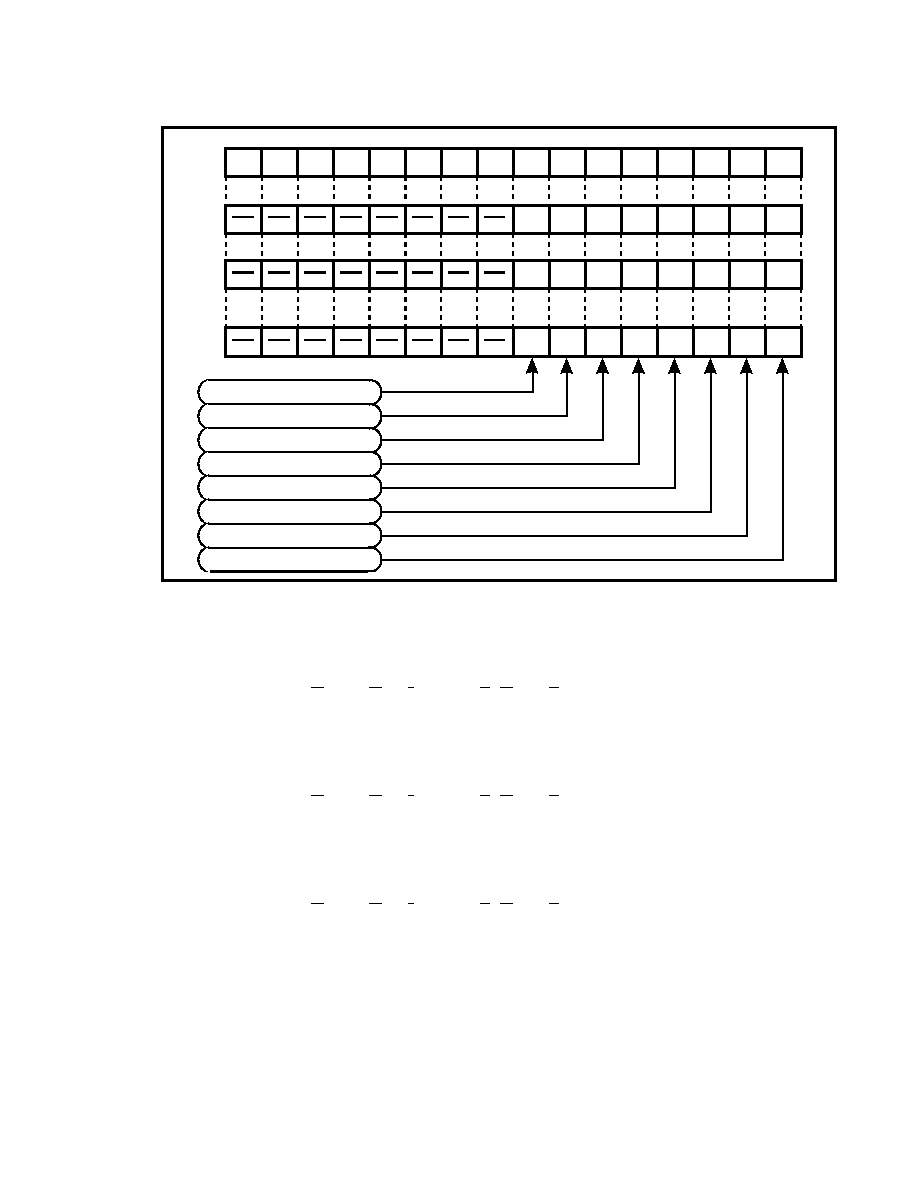

512W

DSP MICRO PROGRAM (STEP_127) "MPRO[15:0]"

DSP MICRO PROGRAM (STEP_127) "MPRO[31:16]"

DSP MICRO PROGRAM (STEP_127) "MPRO[47:32]"

DSP MICRO PROGRAM (STEP_127) "MPRO[63:48]"

DSP MICRO PROGRAM (STEP_126) "MPRO[15:0]"

DSP MICRO PROGRAM (STEP_1) "MPRO[63:48]"

DSP MICRO PROGRAM (STEP_0) "MPR0[15:0]"

DSP MICRO PROGRAM (STEP_0) "MPRO[31:16]"

DSP MICRO PROGRAM (STEP_0) "MPRO[47:32]"

DSP MICRO PROGRAM (STEP_0) "MPRO[63:48]"

100800

100807

100808

100BF8

100BFF

H

H

H

H

H

Figure 4.6 DSP Micro Program Map

Table 4.7 DSP Micro Program

Designation

Contents

MPRO

Micro program register

|

SEGA Confidential

Saturn SCSP User's Manual

33

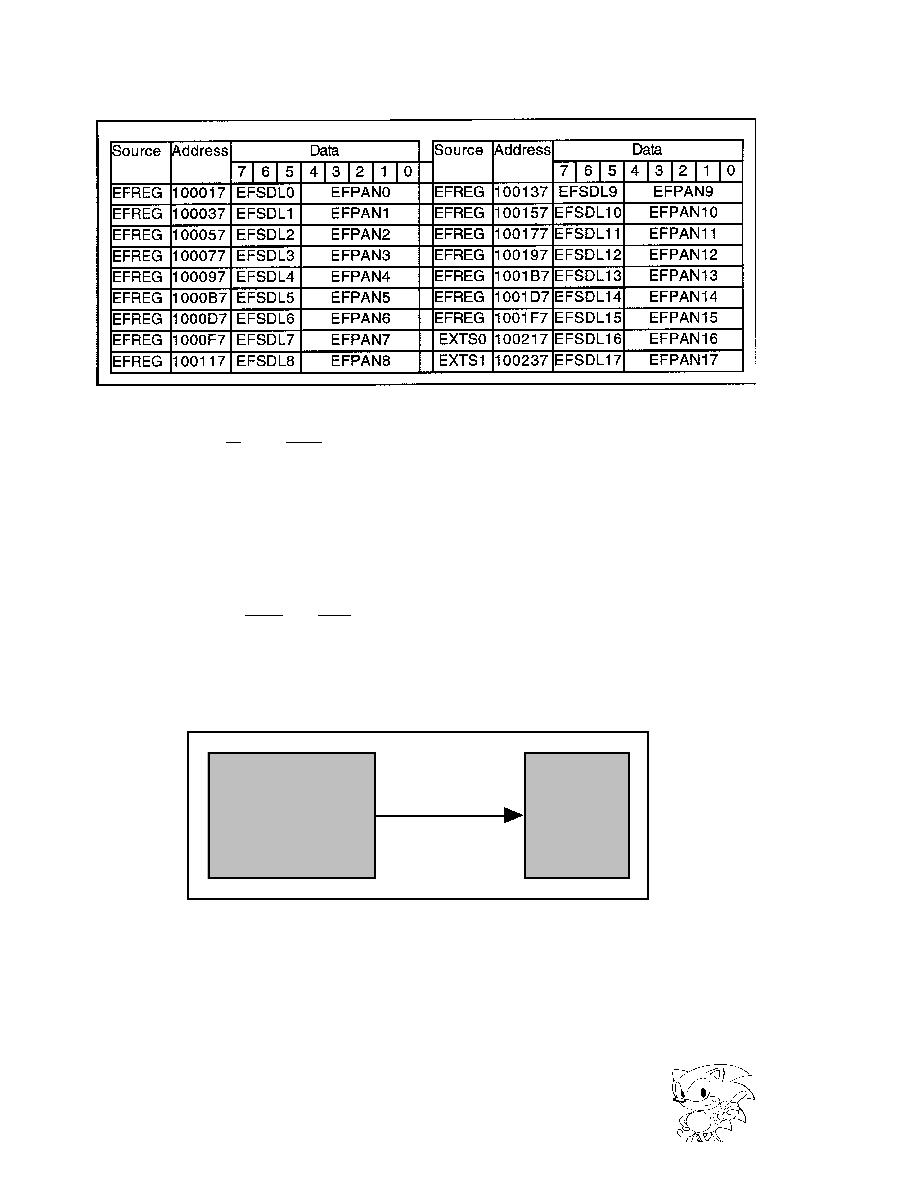

Figure 4.7 DSP Internal Buffer Map

"TEMP[7:0]"

WORK BUFFER 00 "TEMP[23:8]"

"TEMP[7:0]"

WORK BUFFER 127 "TEMP[23:8]"

MEMS[7:0]"

"

SOUND MEMORY 00 "MEMS[23:8]"

"MEMS[7:0]"

SOUND MEMORY 31 "MEMS[23:8]"

"MIXS[3:0]"

MIX SOUND SLOT DATA STACK 00 "MIXS[19:4]"

"MIXS[3:0]"

MIX SOUND SLOT DATA STACK 15 "MIXS[19:4]"

EFFECTED DATA OUTPUT 00 "EFREG[15:0]"

EFFECTED DATA OUTPUT 15 "EFREG[15:0]"

100EE3

100EDF

100EE0

(16W)

100EBF

100EC0

(32W)

100E7F

100E80

(64W)

100DFF

100E00

(256W)

100C00

H

H

H

H

H

H

H

H

H

H

Table 4.8 DSP Internal Buffer

Designation

Contents

TEMP

DSP temporary (universal) buffer

MEMS

Memory data stack

MIXS

Mix stack

EFREG

Effect register

|

SEGA Confidential

34

4.2

Sound Source Register

The sound source (block) register is made up of the allocations shown in Table 4.9.

Table 4.9 Sound Source (Block) Register Allocation

Register Name

Bit Name

Loop Control Register

KYONEX, KYONB, SBCTL, SSCTL, SA, LSA,

LEA, PCM8B, LPCTL

EG Register

EGHOLD, AR, D1R, D2R, RR, DL, KRS, LPSLNK

FM Modulation Control Register

SOUS, MDL, MDXSL, MDYSL, STWINH

Sound Volume Register

TL, SDIR

PITCH Register

OCT, FNS

LFO Register

LFORE, LFOF, ALFOWS, ALFOS,

PLFOWS,PLFOS

MIXER Register

IMXL, ISEL, DISDL, DIPAN, EFSDL, EFPAN,

MVOL, DAC18B

Slot Status Register

MSLC, CA

Sound Memory Config. Register

MEM4MB

MIDI Register

MIBUF, MIOVF, MIFULL, MIEMP, MOFULL,

MOEMP, MOBUF

Timer Register

TACTL, TIMA,TBCTL, TIMB, TCCTL, TIMC

Interrupt Control Register

SCIPD, SCIEB, SCIRE, SCILVO, SCILV1, SCILV2,

MCIPD, MCIEB, MCIRE

DMA Transfer Register

DGATE, DDIR, DEXE, DMEA, DRGA,DTLG

|

SEGA Confidential

Saturn SCSP User's Manual

35

Below is the definition of the bit in terms of the sound generator block register,

based on the classifications in Table 4.9. The symbols following the register names

have the following meanings: (R) read only, (W) write only, (R/W) both read and

write are possible.

When reading data from the write only register (bit), that value becomes "0

B

".

When writing data to the read only register (bit), always write "0

B

".

Loop Control Register

KYONEX (W) ;KeY_ON EXecution

A "1B" written here will execute KEY_ON, OFF for all of the slots.

KYONB (R/W) ;KeY_ON Bit

Registers KEY_ON,OFF. (If you wish to KEY_ON simultaneously, the "KYONB" of

the slot you want to turn ON must be set to "1B".)

Table 4.10 KYONB Function

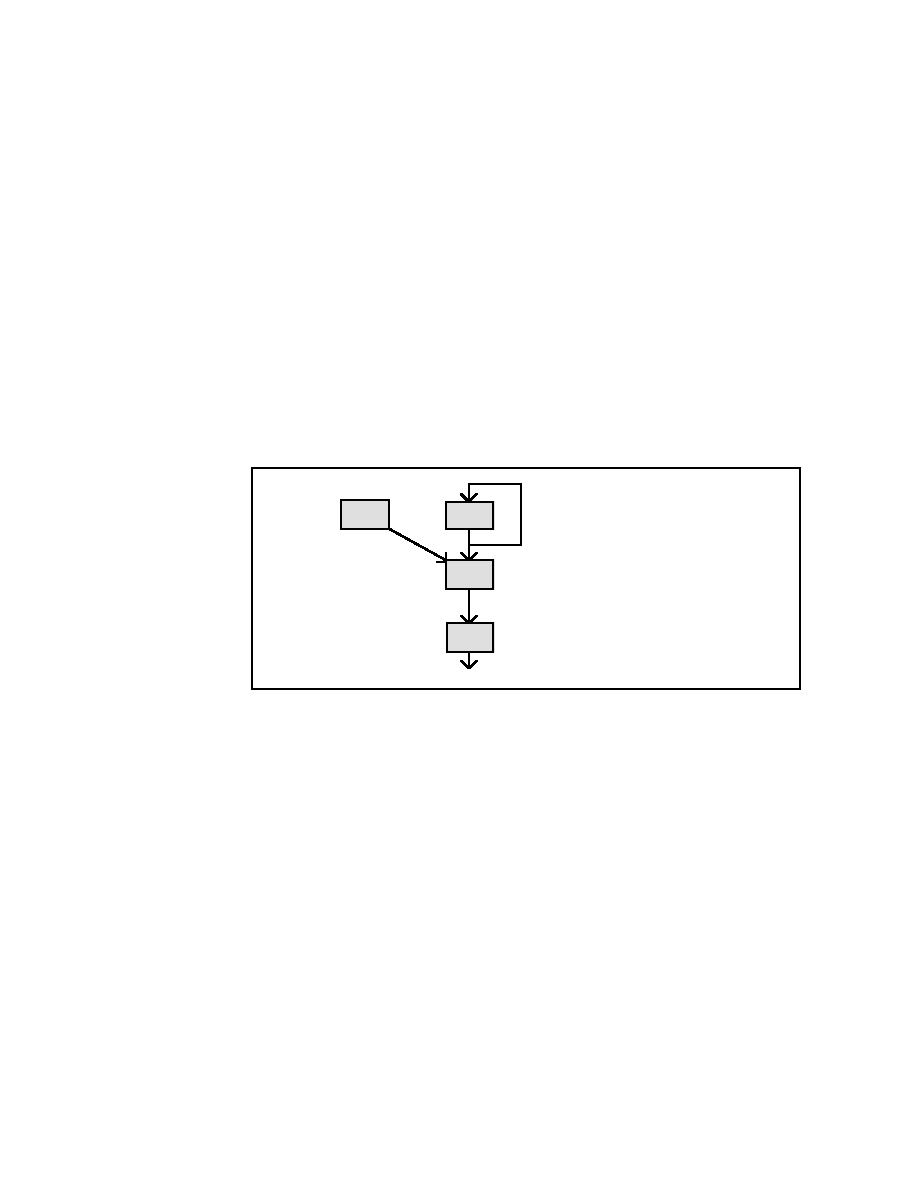

"KYONEX" and "KYONB" exist in each slot. The sequence of KEY_ON and

KEY_OFF is shown in Figure 4.8.

There is no need to write a "0B" in "KYONEX" after writing a "1B". Also a "1B" in

"KYONEX" is used for all slots, so you don't need to set to "1B" per a specific slot.

KYONB

REGISTER

KYONEX

REGISTER

KEYON

TRIGGER

"0"

"0"

"0"

"0"

"0"

"0"

"0"

"0"

"0"

"0"

"0"

"1"

"1"

"OFF"

"ON"

"ON"

"ON"

"OFF"

"1" WRITE

"1" WRITE

"1"WRITE

"1"WRITE

Time

Time

Time

Execute

Ignore

Execute

No Meaning

ON

OFF

"1"

"1"

"1"

"1"

"1" WRITE

"0" WRITE

"1"

Figure 4.8 KEY_ON and KEY_OFF Sequence

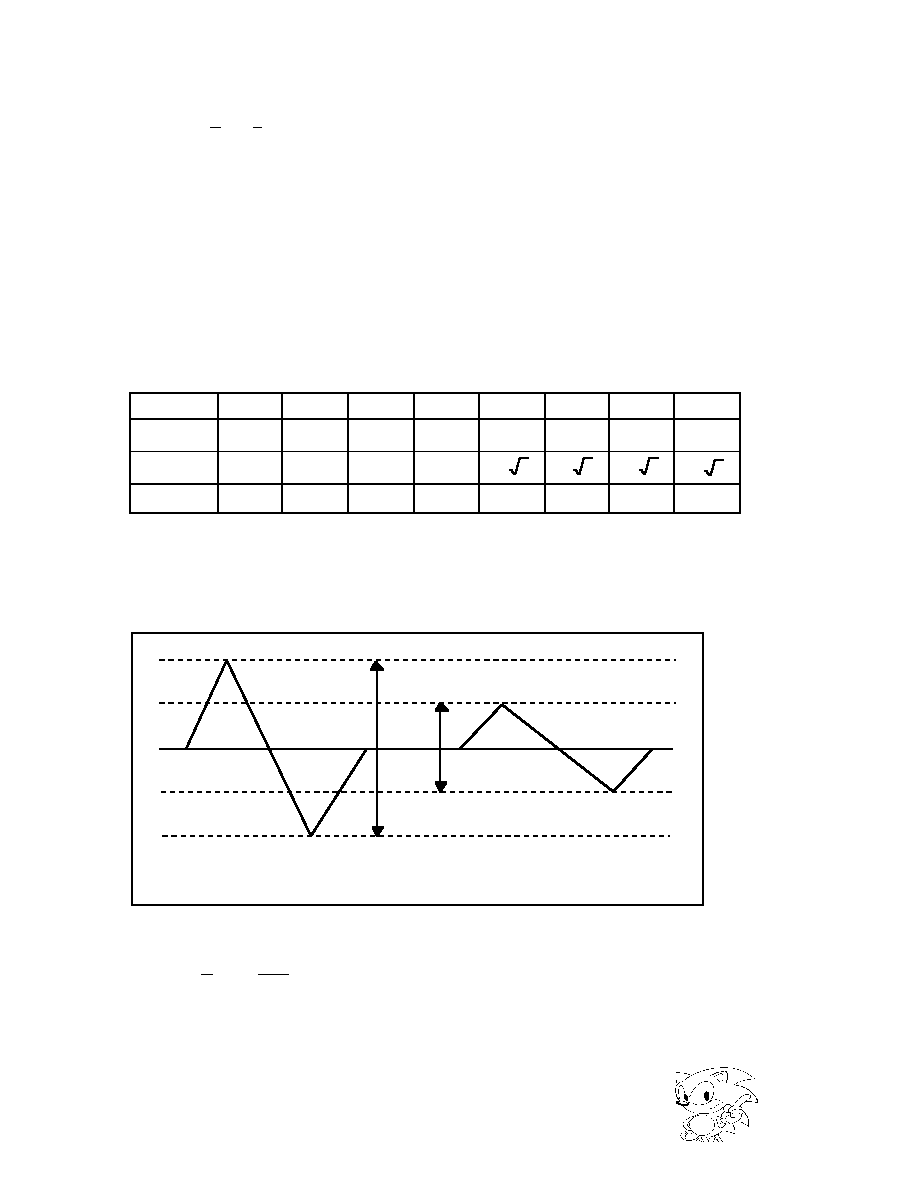

SBCTL[1:0] (R/W) ;Source Bit ConTroL

Specifies bit reversal operation of the sound input data. The reversal function be-

comes valid for bits with "1B" written to them.

bit

Function

0

Registers KEY_OFF

1

Registers KEY_ON

|

SEGA Confidential

36

Table 4.11 SBCTL Function

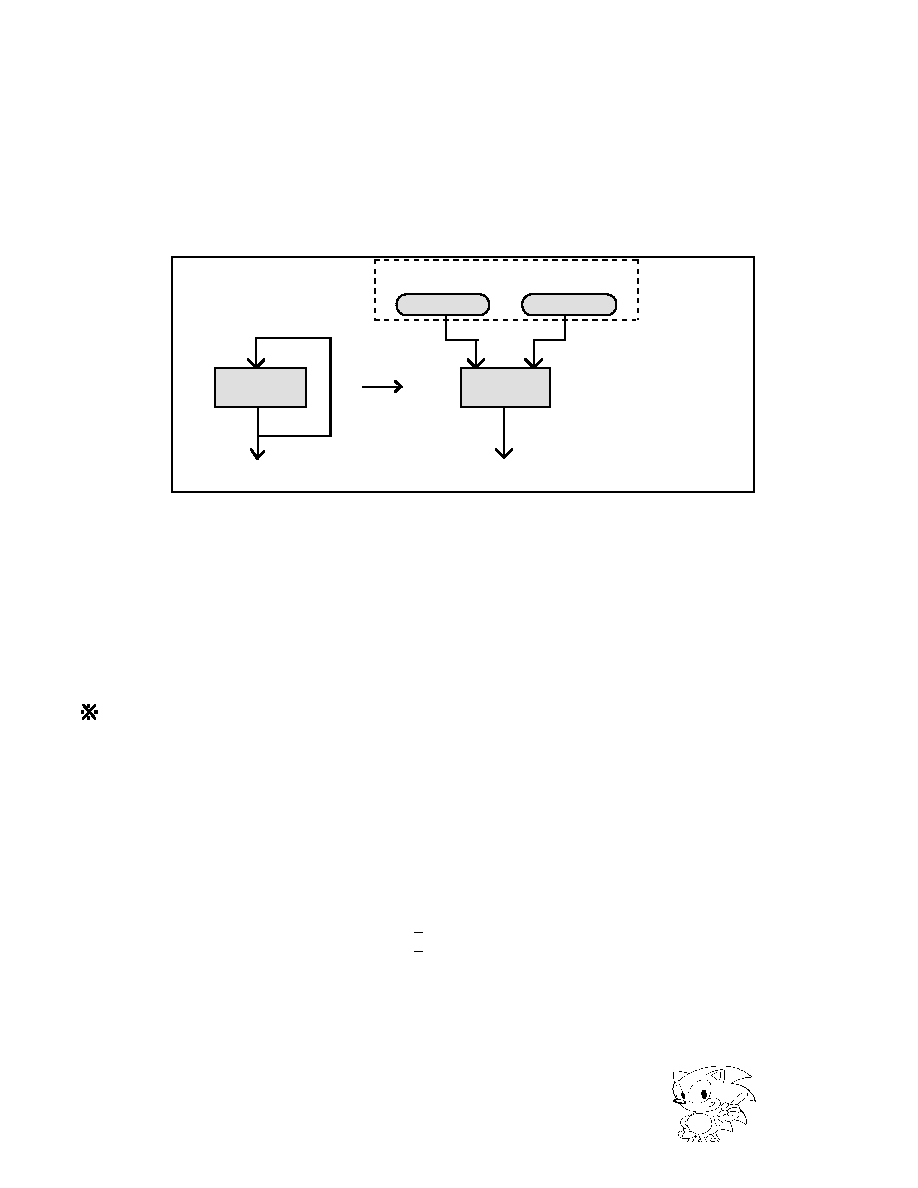

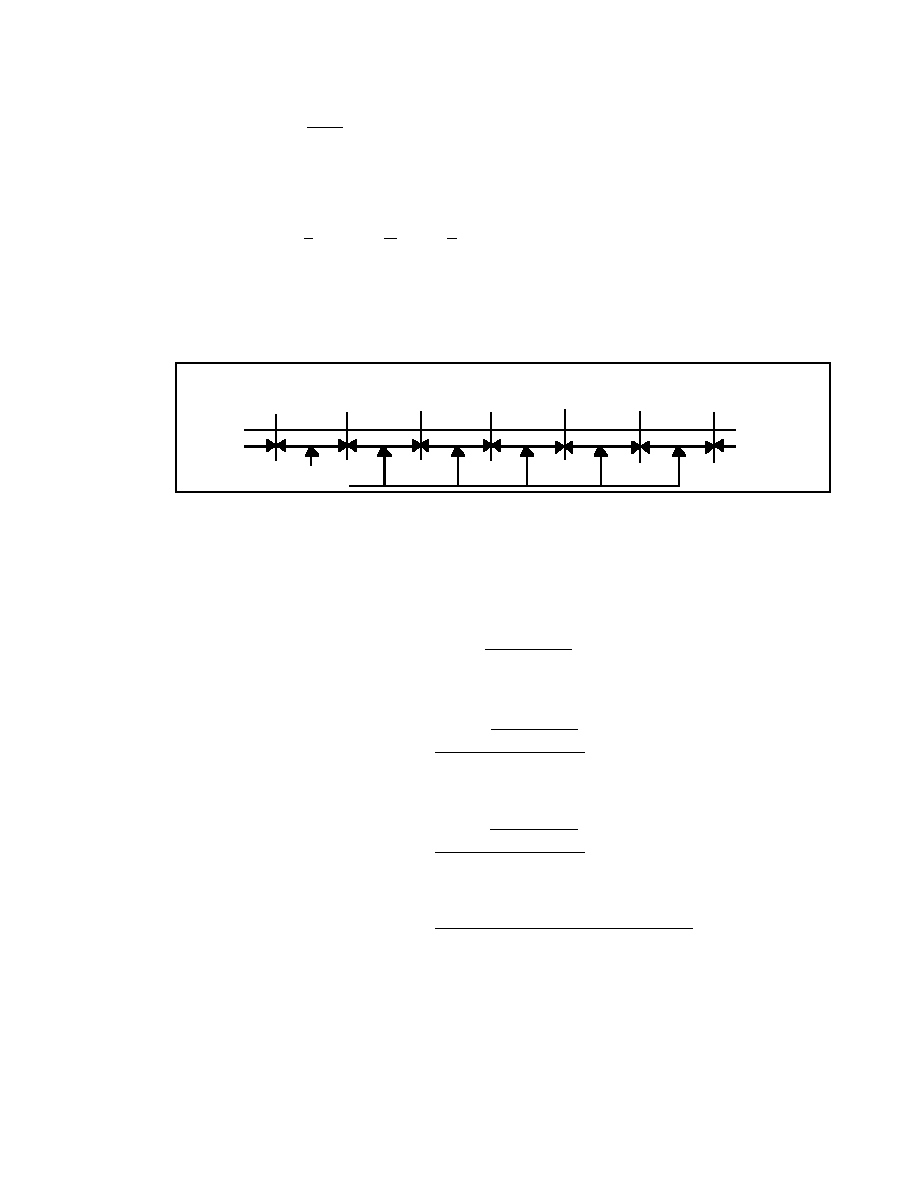

SSCTL[1:0] (R/W) ;Sound Source ConTroL

Designates the data to be used as sound input data. When using the wave form data

in sound memory to produce a sound, write "0B". When this register is "1

B

", the

slot with respect to which setting has been applied (the LFO accompanied with each

slot) will output noise.

The block diagram of noise generated when "SSCTL"="1

B

" and the relation to LFO

is shown with ALFO added in Figure 4.9

ALFOWS

SLOT

Wave Form Data

Buffer

TL

EG

SSCTL

SELECTOR

2

TO

1

Waveform Data From

Wave Form Memory (RAM)

Normal Sound

Noise

White Noise

Sound Data

Noise On/Off

Function

Level

Calculater

Block

Level

Coefficient

Level

Coeffici-

ent

Calculater

Block

LFORE

LFOF

Amplitude Modulation Rate

Adjustment

* Alfo is Attached Here

ALFOS

SELECTOR

4

TO

1

LEO Waveform Generator

Sawtooth

Wave

Square

Wave

Triangle

Wave

ALFOWS

Figure 4.9 Relation of the Noise Generation Block Diagram and LFO

Bit

Function

SBCTL0

Reverse selection for bits other than the source wave form

data sign bit.

SBCTL1

Reverse selection for the source wave form data sign bit.

|

SEGA Confidential

Saturn SCSP User's Manual

37

Each slot utilizes the LFO noise oscillator output to output noise. Here, the LFO

parameters in Figure 4.9 ("LFORE", "LFOF", "ALFOWS", "ALFOS", "PLFOWS",

"PLFOS") will not affect noise as voice data.

Also, when using LFO in low-frequency modulation with the LFO wave form selec-

tion at noise (ALFOWS="3H", or PLFOWS="3H") as in Figure 4.9, reset with the

"LFORE" will not function. The frequency also cannot be changed. This means that

when selecting noise, the LFO can select wave form but cannot change in terms of

other parameters.

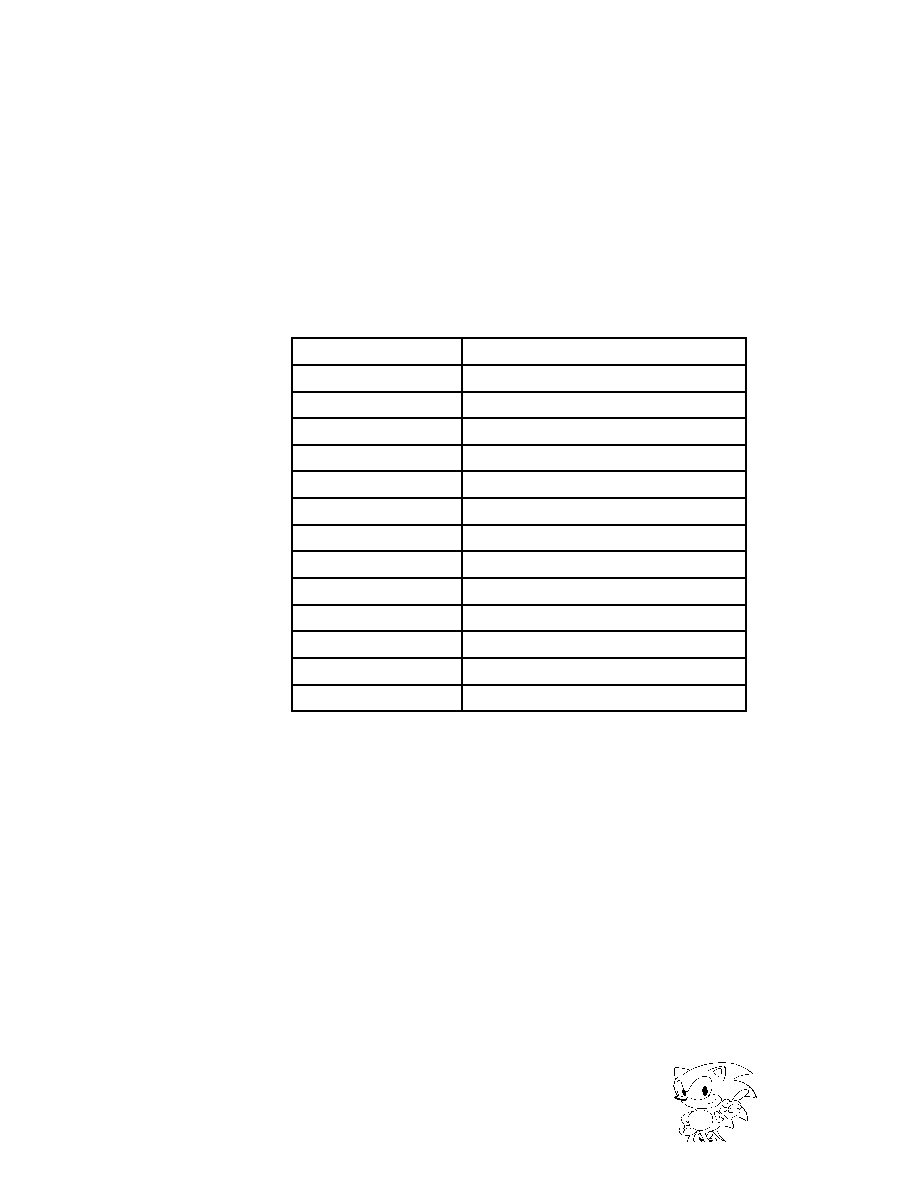

Table 4.12 SSCTL Internal Configuration

SA[19:0] (R/W) ;Start Address

Specifies the waveform data start address in byte address when using memory

waveform data to generate sound. However, if the waveform data is "16 bit PCM"

("PCM8B"="0"), always set the register's lsb (SA0) to "0B".

LSA[15:0] (R/W) ; Loop Start Address

Represents the sound data loop start address in sample count from the "SA".

LEA[15:0] (R/W) ; Loop End Address

Represents the sound data loop end address in sample count from the "SA".

PCM8B (R/W) ; PCM 8Bit

Designates the format of the wave form data.

Table 4.13 Types of Sound Data

SSCTL

Data Used

0

External DRAM data

1

Internally generated data (noise)

2

Internally generated data (ALL "0")

3

Cannot be used

PCM8B

Sound Data

0

16Bit PCM data 2'S complement

1

8Bit PCM data 2'S complement

|

SEGA Confidential

38

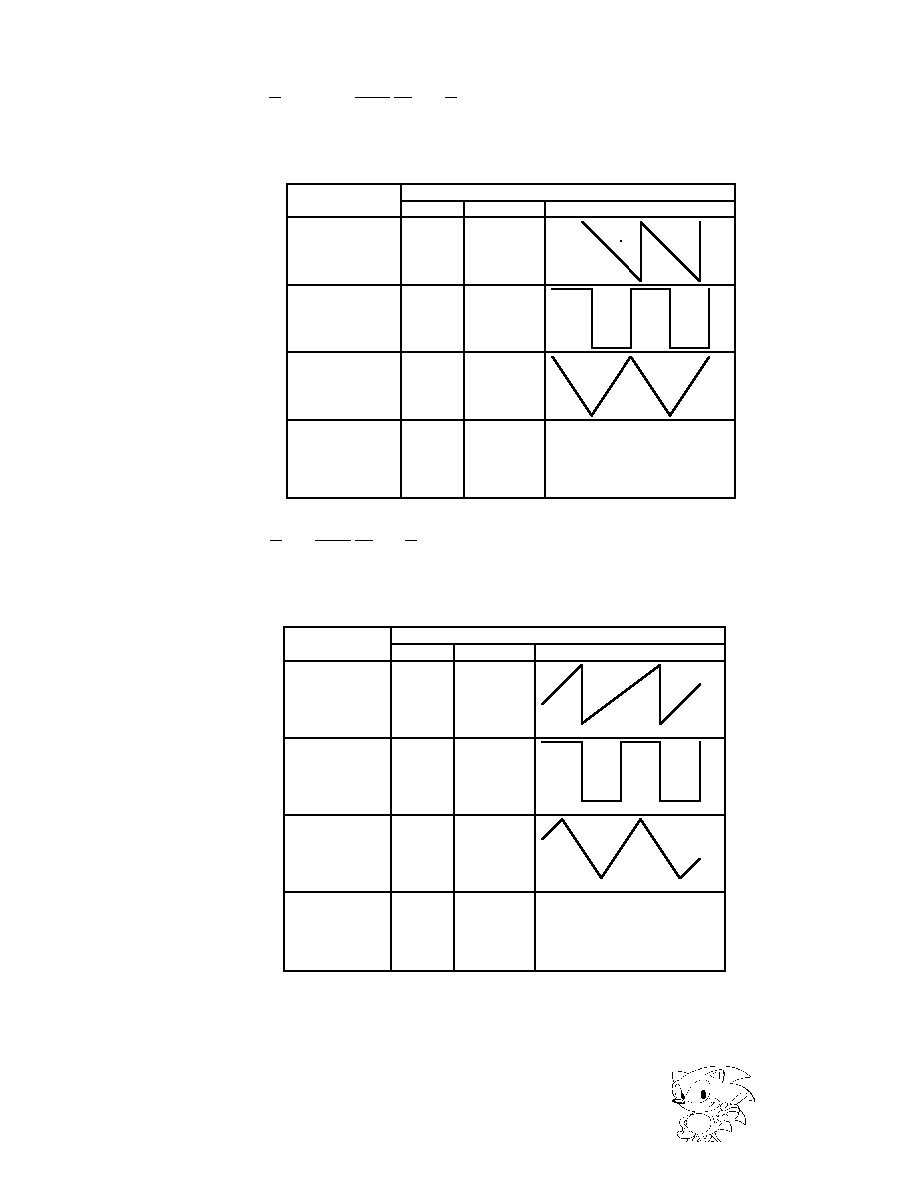

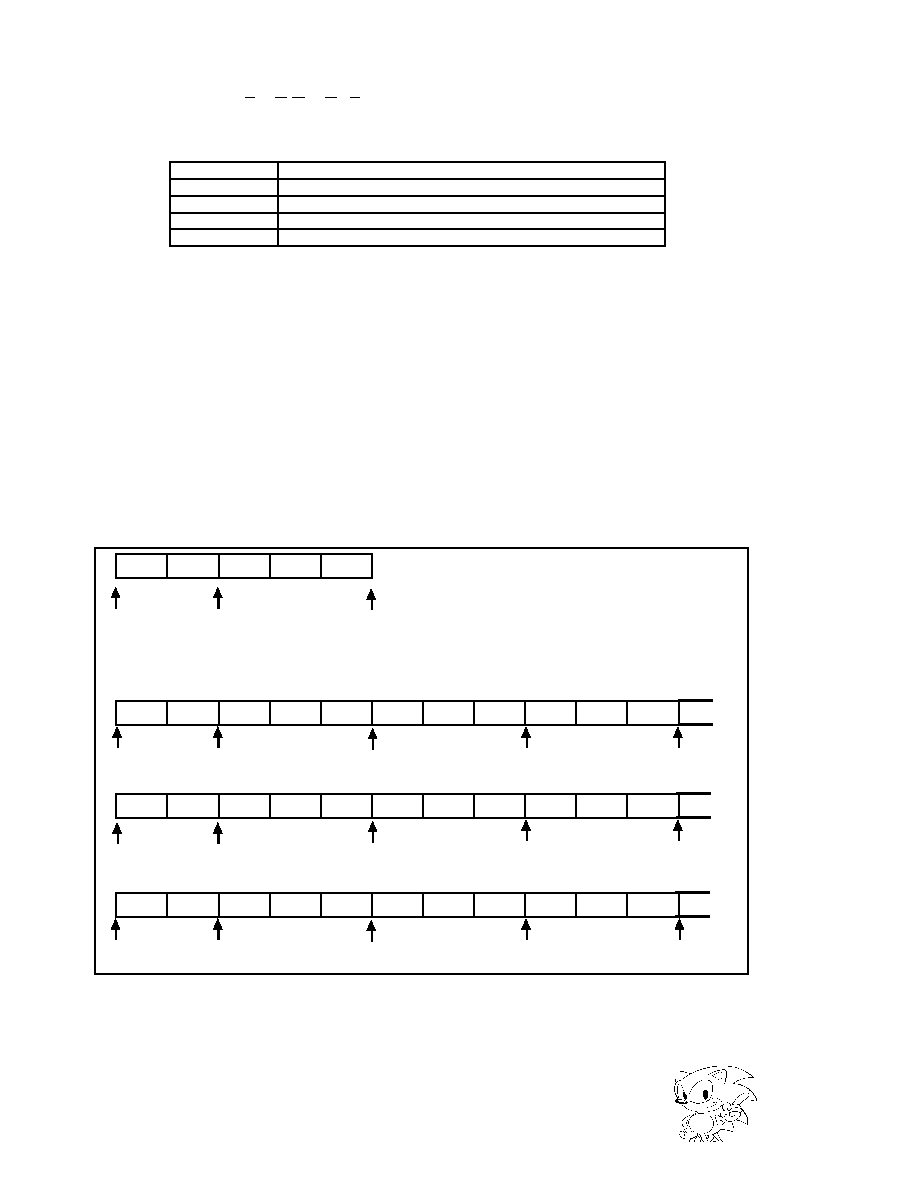

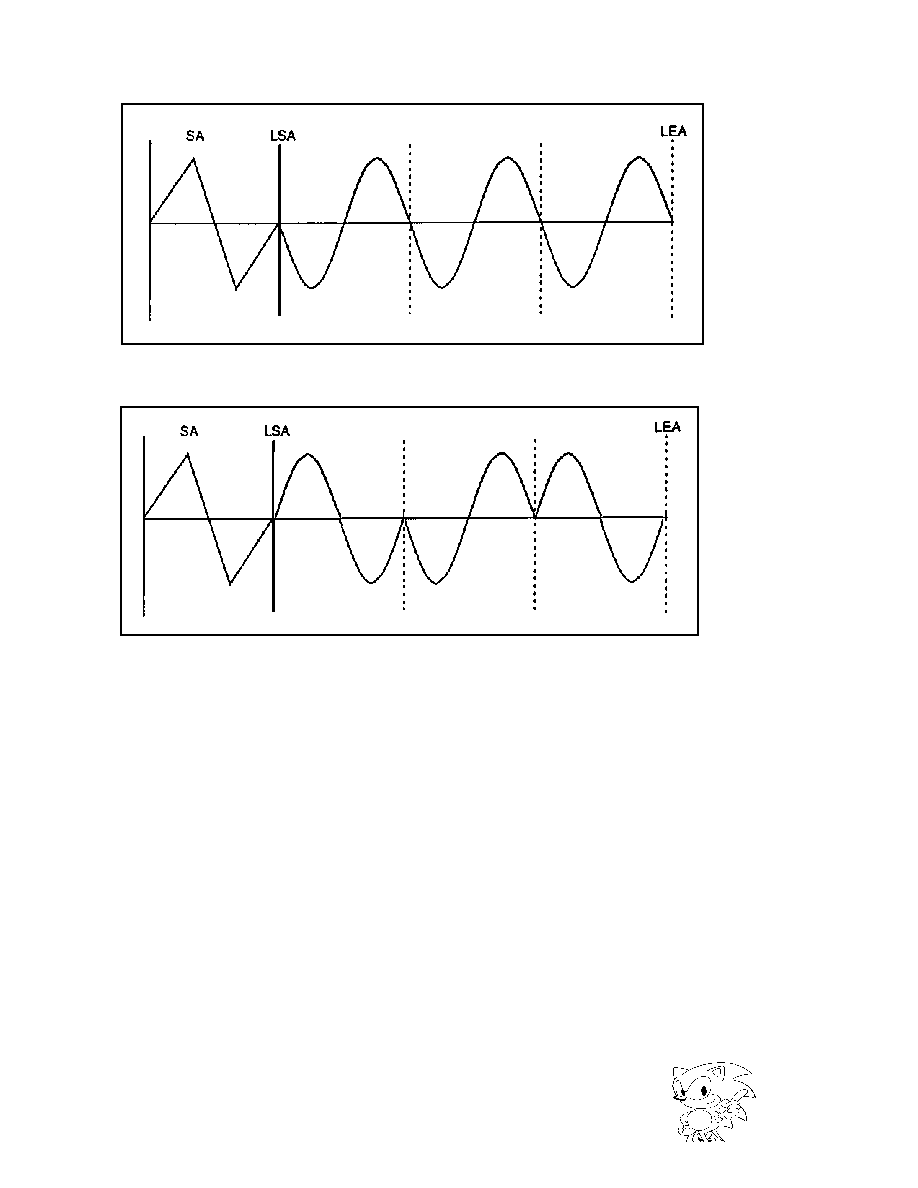

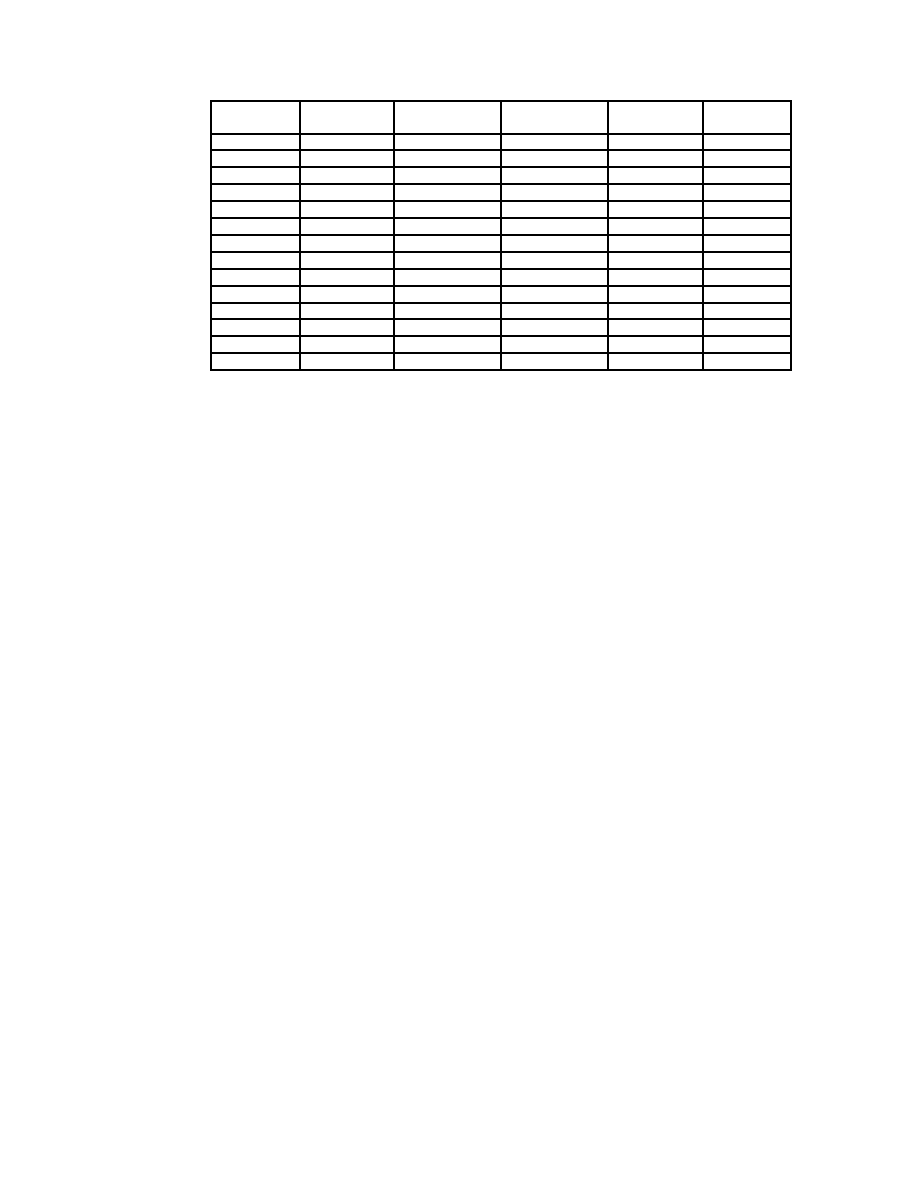

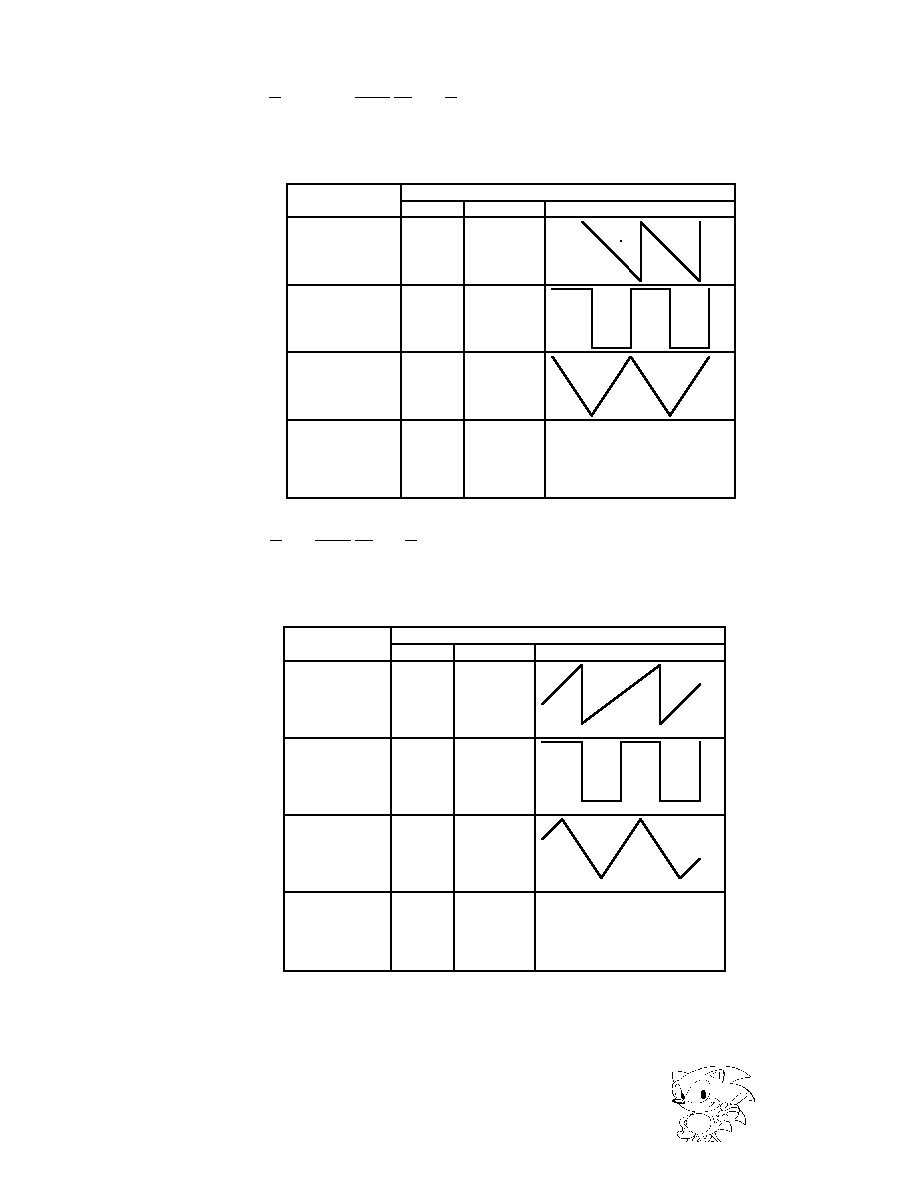

LPCTL[1:0] (R/W) LooP ConTroL

Sets the loop format.

Table 4.14 Types of Loops

Loop processing or sound memory access will end with either of the following two

conditions:

(1)

After release, when the attenuation volume reaches maximum, or

(2)

When the loop is OFF, and the read point reaches the loop end point.

When using normal or reverse loops, set the data corresponding to

"SA+LSA" (loop start address) and the "SA+LEA" (loop end address) to the

same value. Using the same method with the alternative loop can make the

pitch the same as the normal or reverse loops.

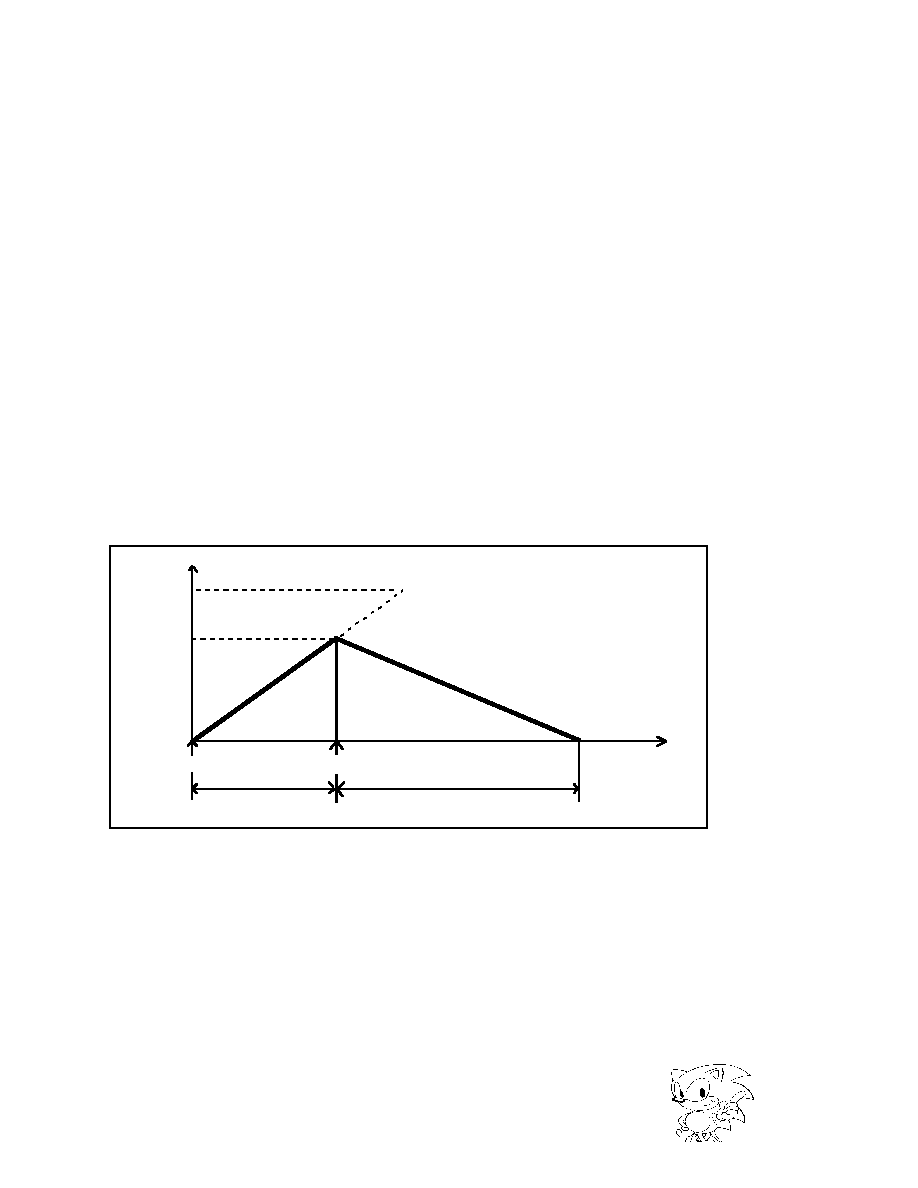

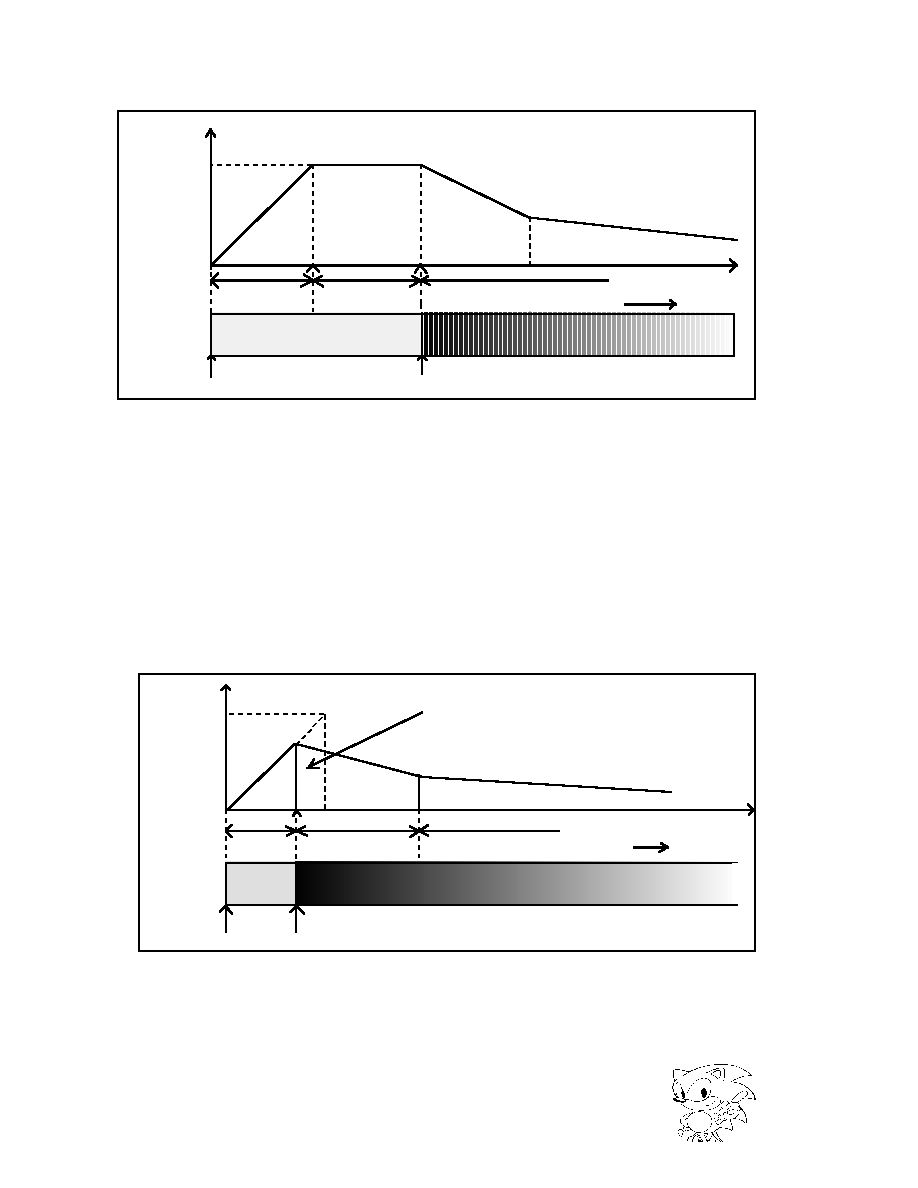

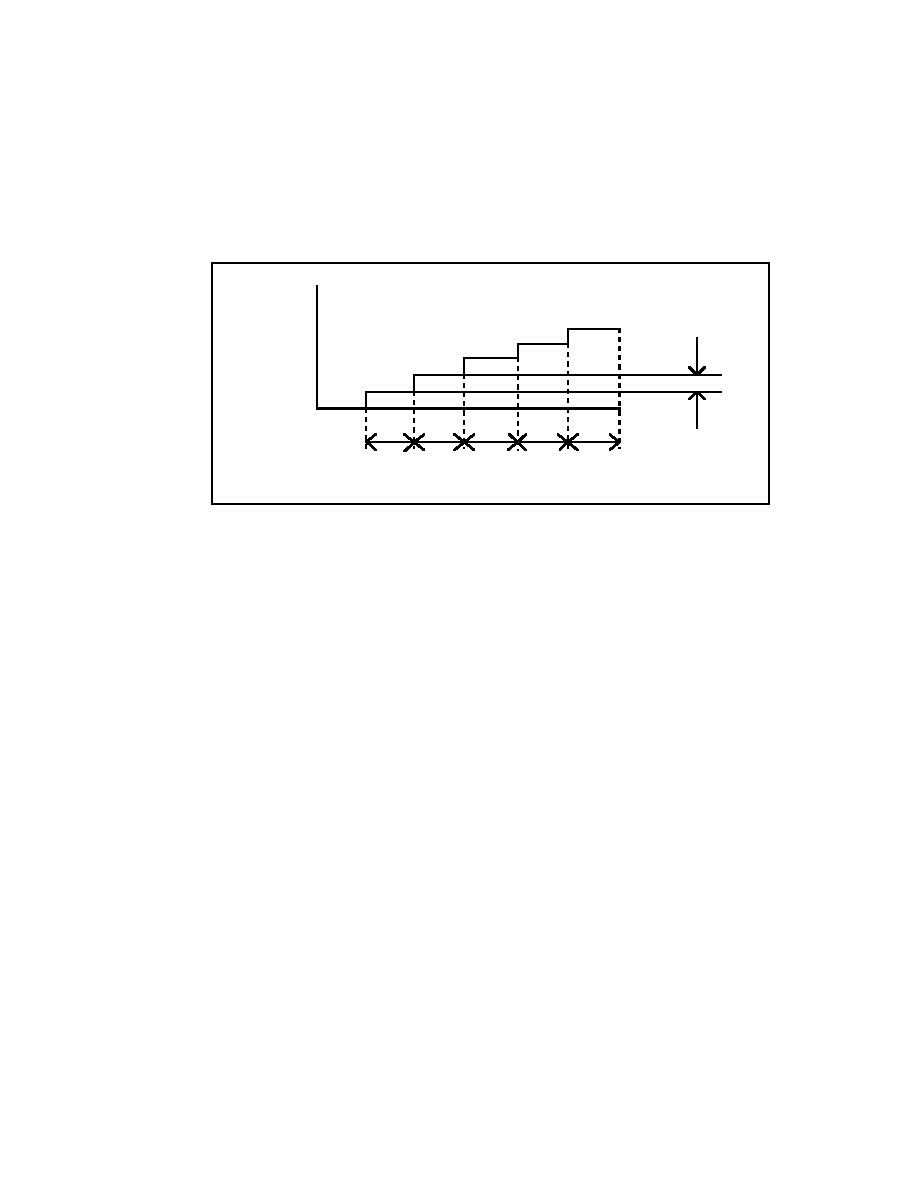

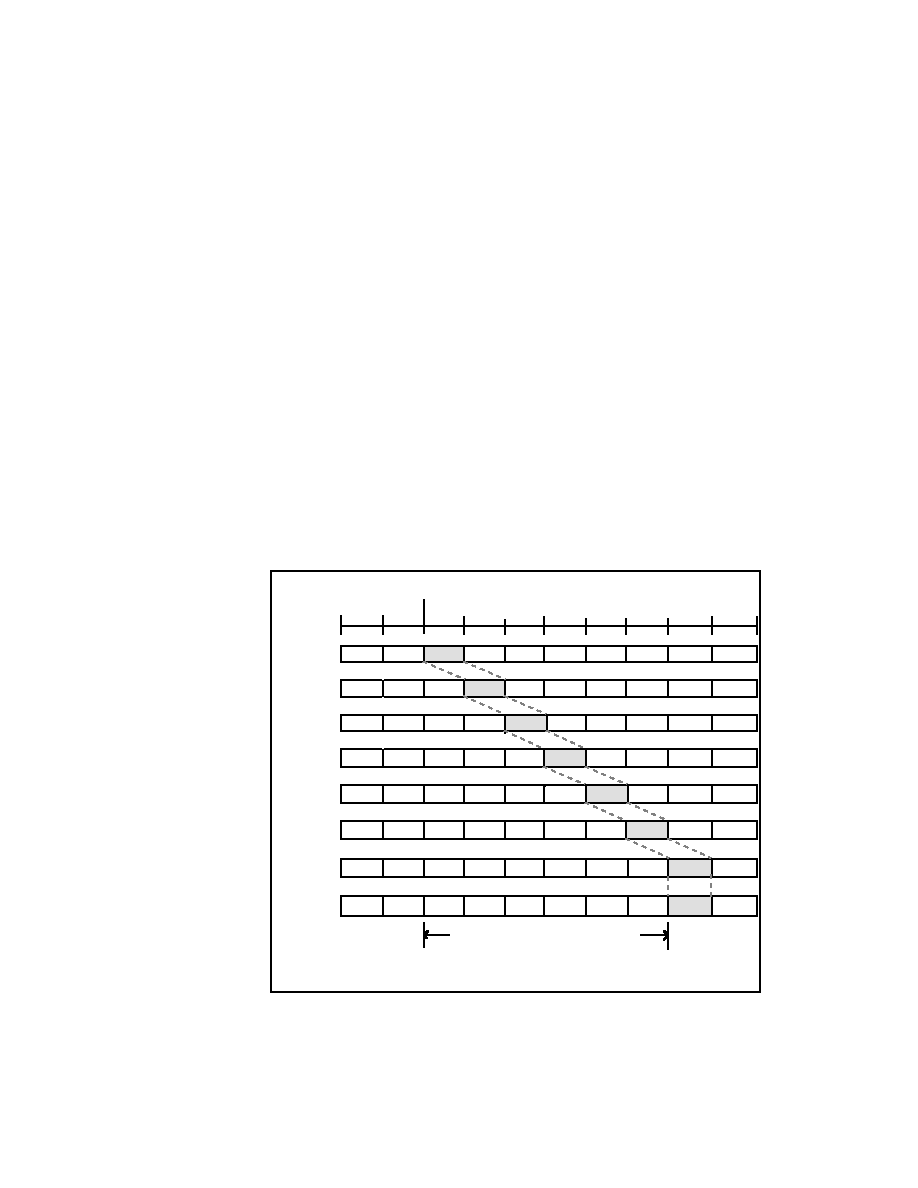

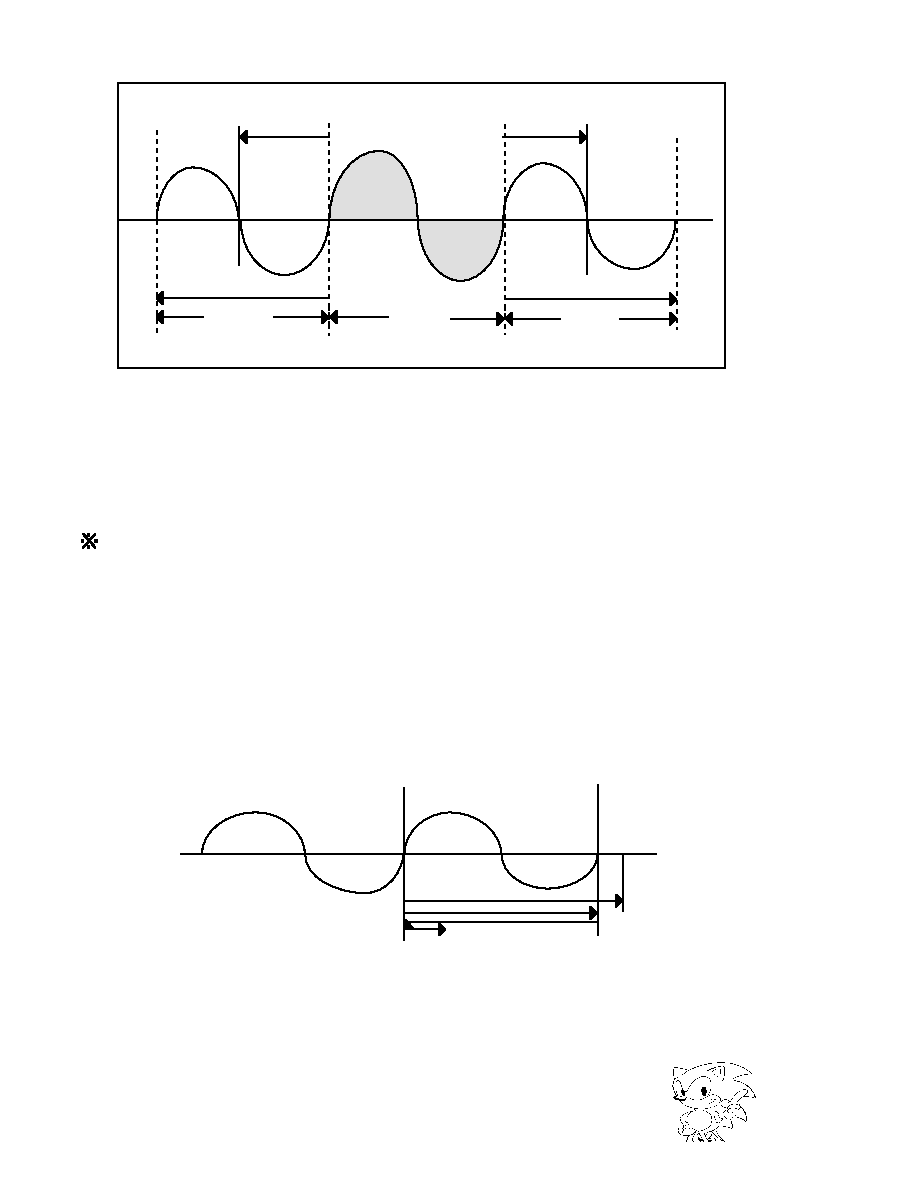

Figure 4.10 shows specific examples of loop types.

Attack Data

Loop Data

Using the sounds "ha- hi- hu- he- ho" as wave form data, the following sounds are produced when the

start address (SA), loop start address (LSA), and loop end address (LEA) are set as shown above.

haaaa

h i i i i huuuu

heeee

hoooo

SA

LSA

LEA

Normal Loop

haaaa

h i i i i huuuu

heeee

hoooo huuuu

heeee

hoooo huuuu

heeee

hoooo huu

q

Reversal Loop

haaaa

h i i i i

q

ooooh eeeeh

uuuuh

ooooh eeeeh

uuuuh

ooooh eeeeh

uuuuh ooo

Alternative Loop

haaaa

h i i i i

q

huuuu

heeee

hoooo ooooh eeeeh

uuuuh

heeee

hoooo ooo

huuuu

SA

SA

SA

LSA

LSA

LEA

LEA

LEA

LSA

LEA(LSA)

LEA(LSA)

LEA(LSA)

LSA(LEA)

LSA(LEA)

LSA(LEA)

Figure 4.10 Loop Types

LPCTL

Loop Format

0

Loop OFF

1

Normal loop

2

Reverse loop

3

Alternative loop

|

SEGA Confidential

Saturn SCSP User's Manual

39

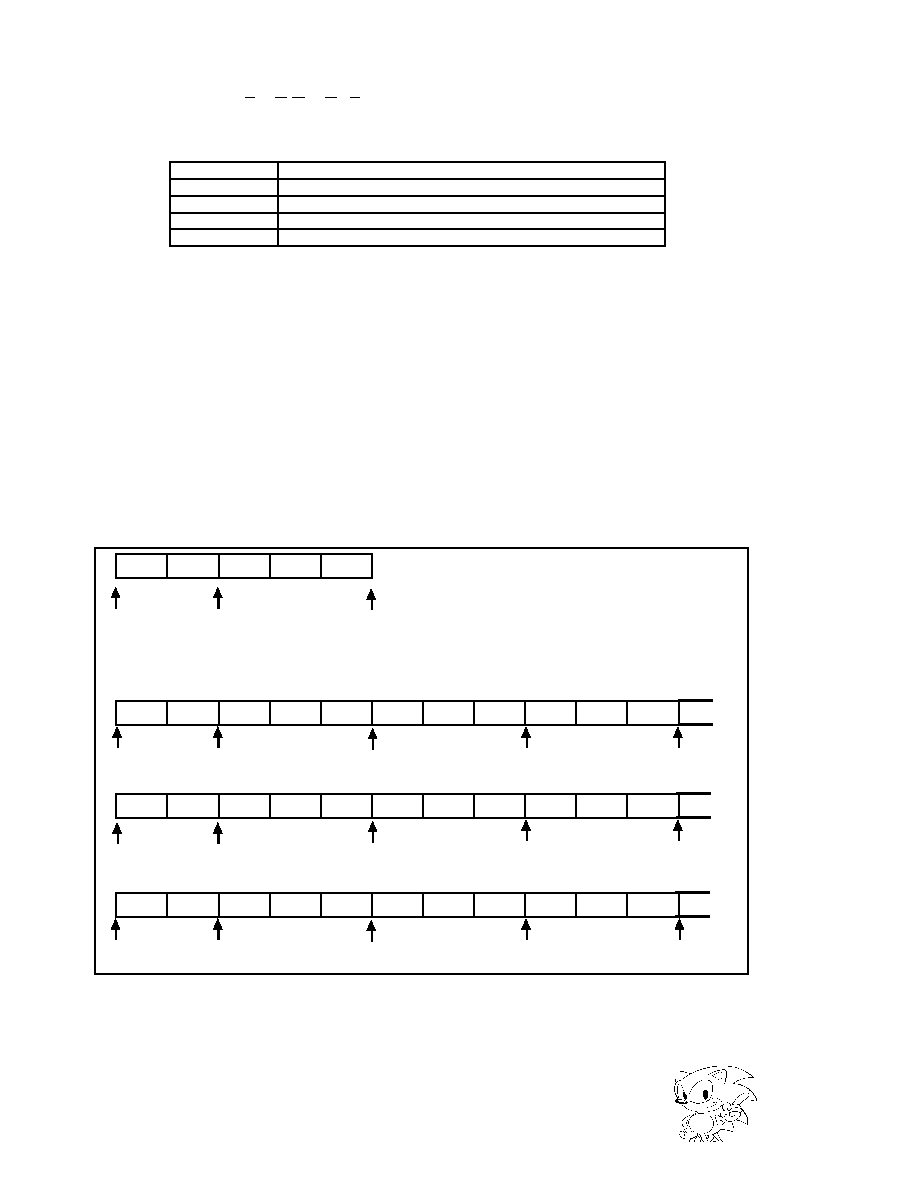

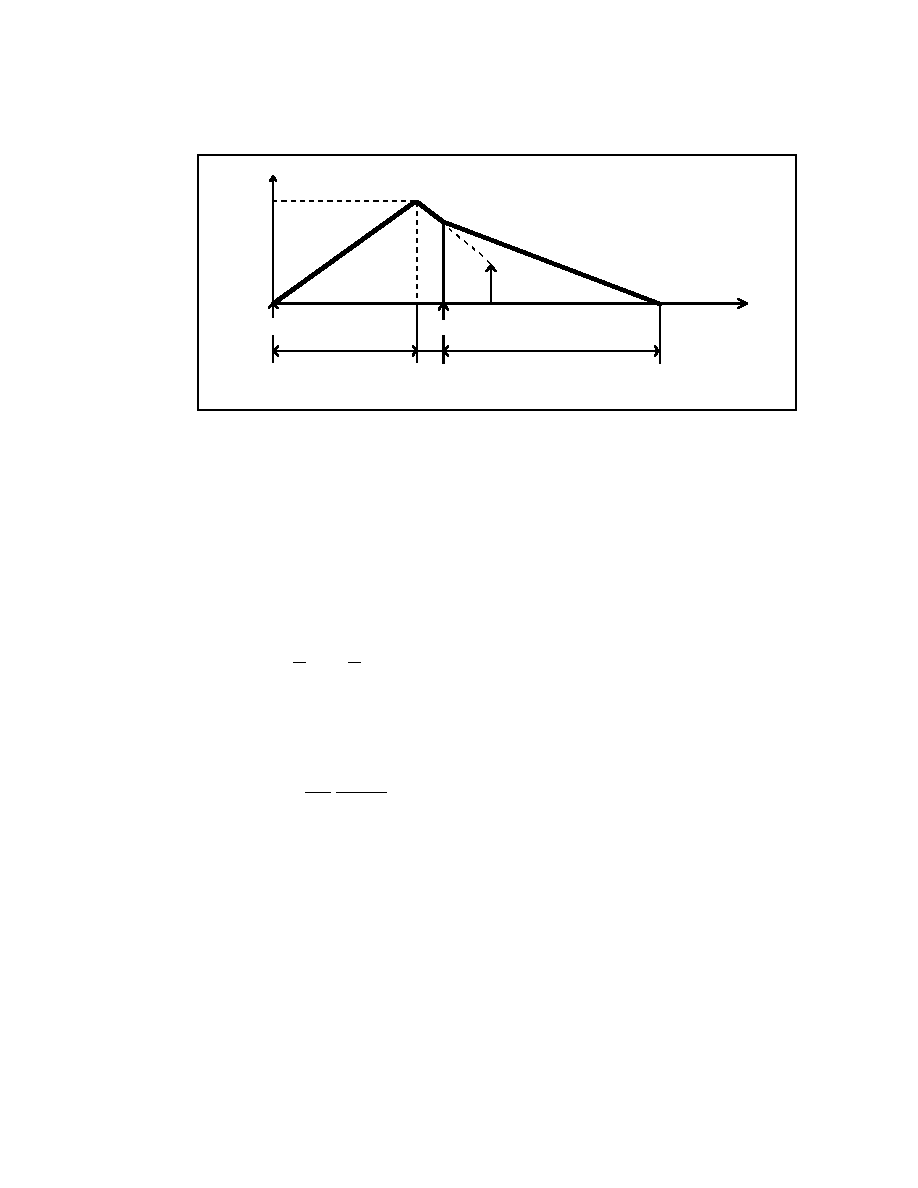

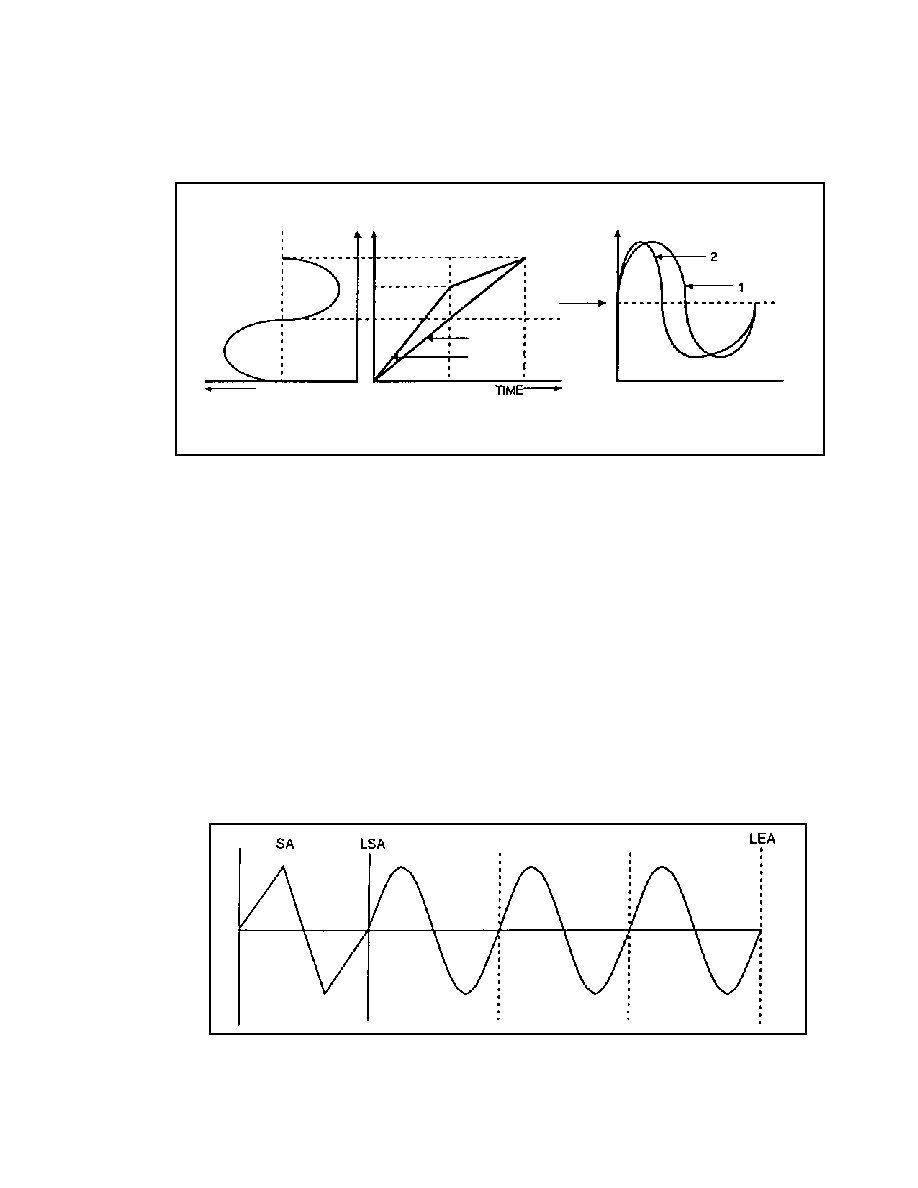

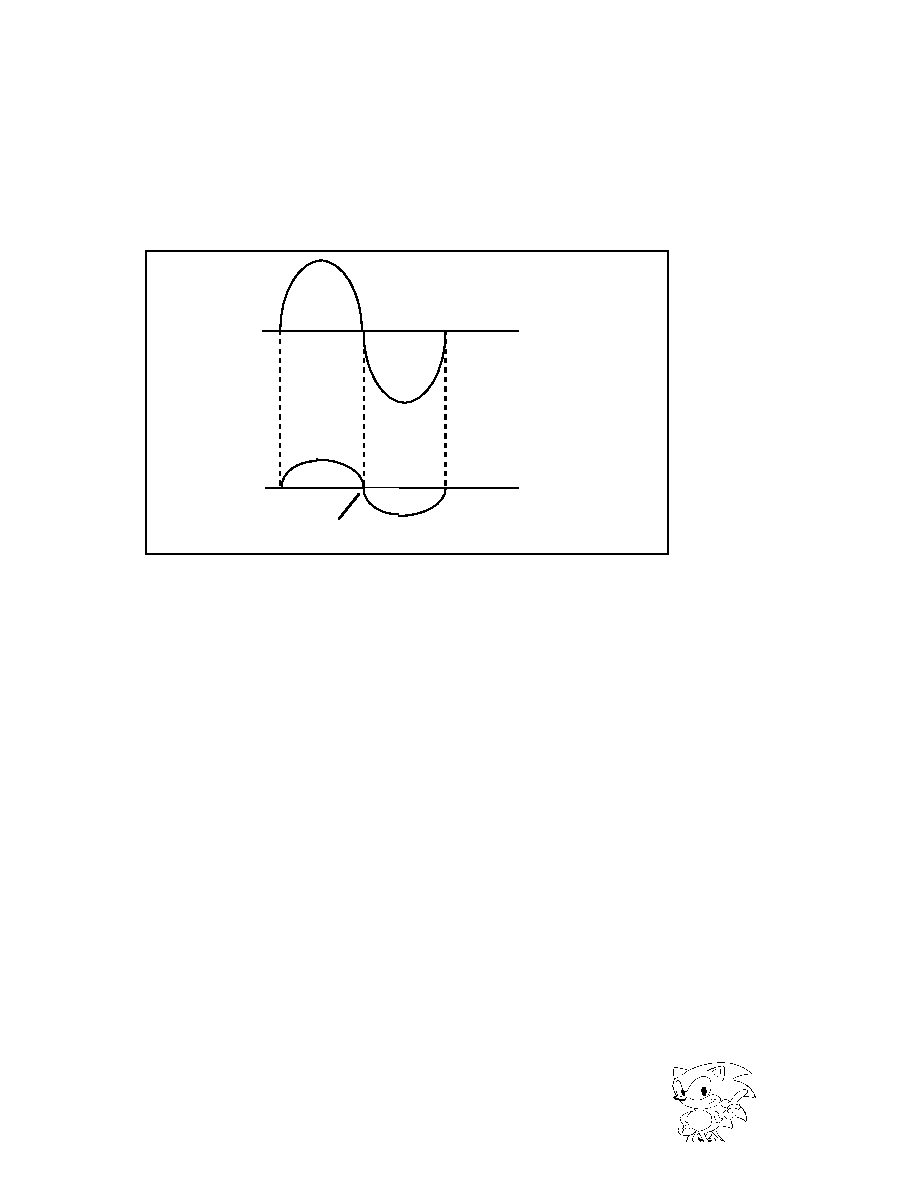

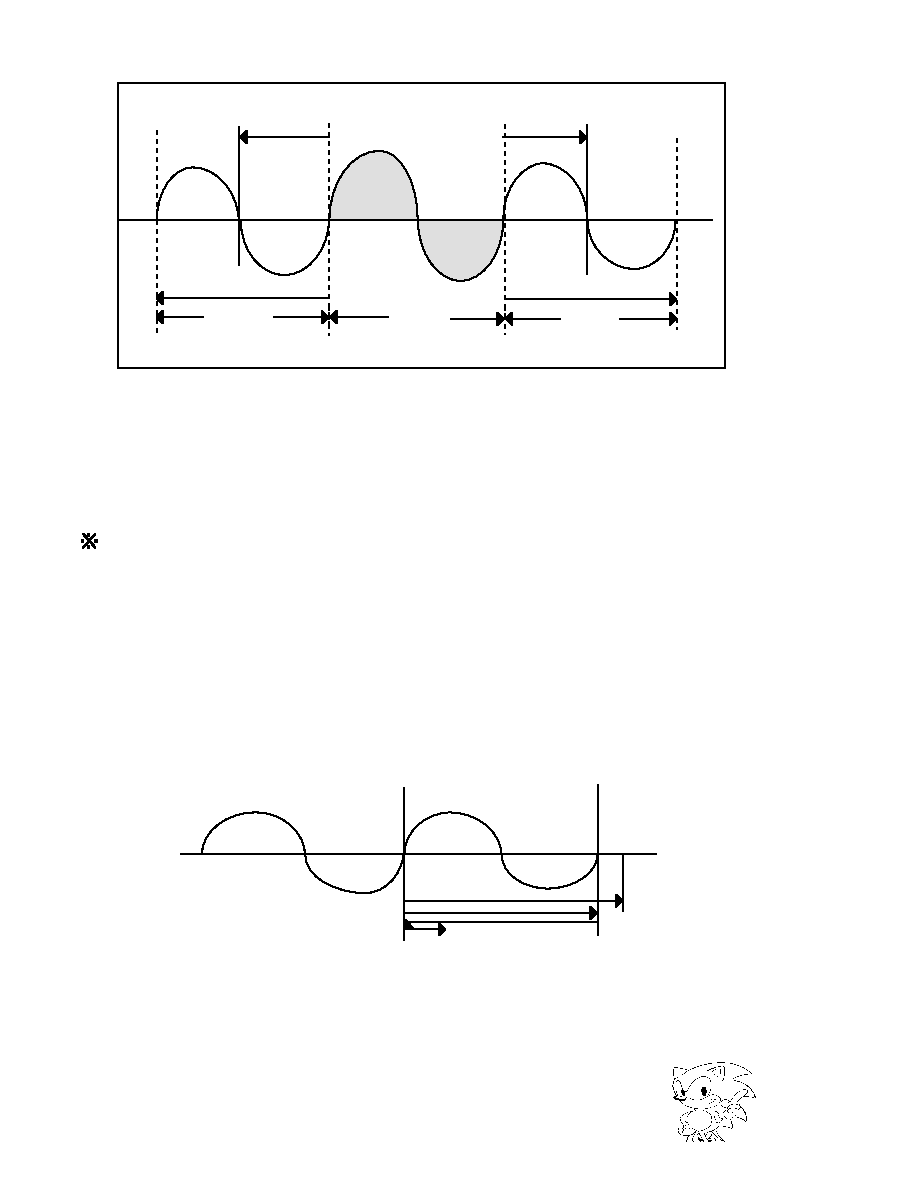

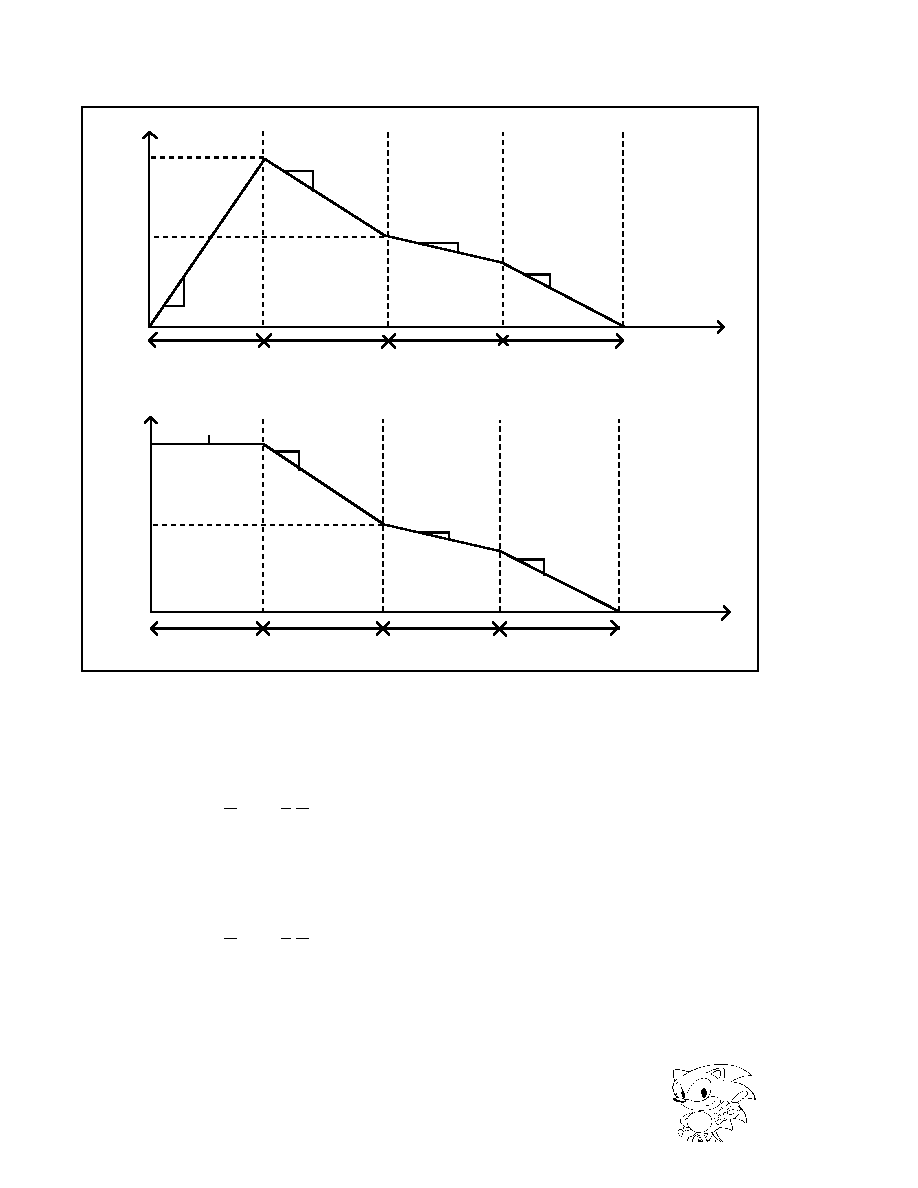

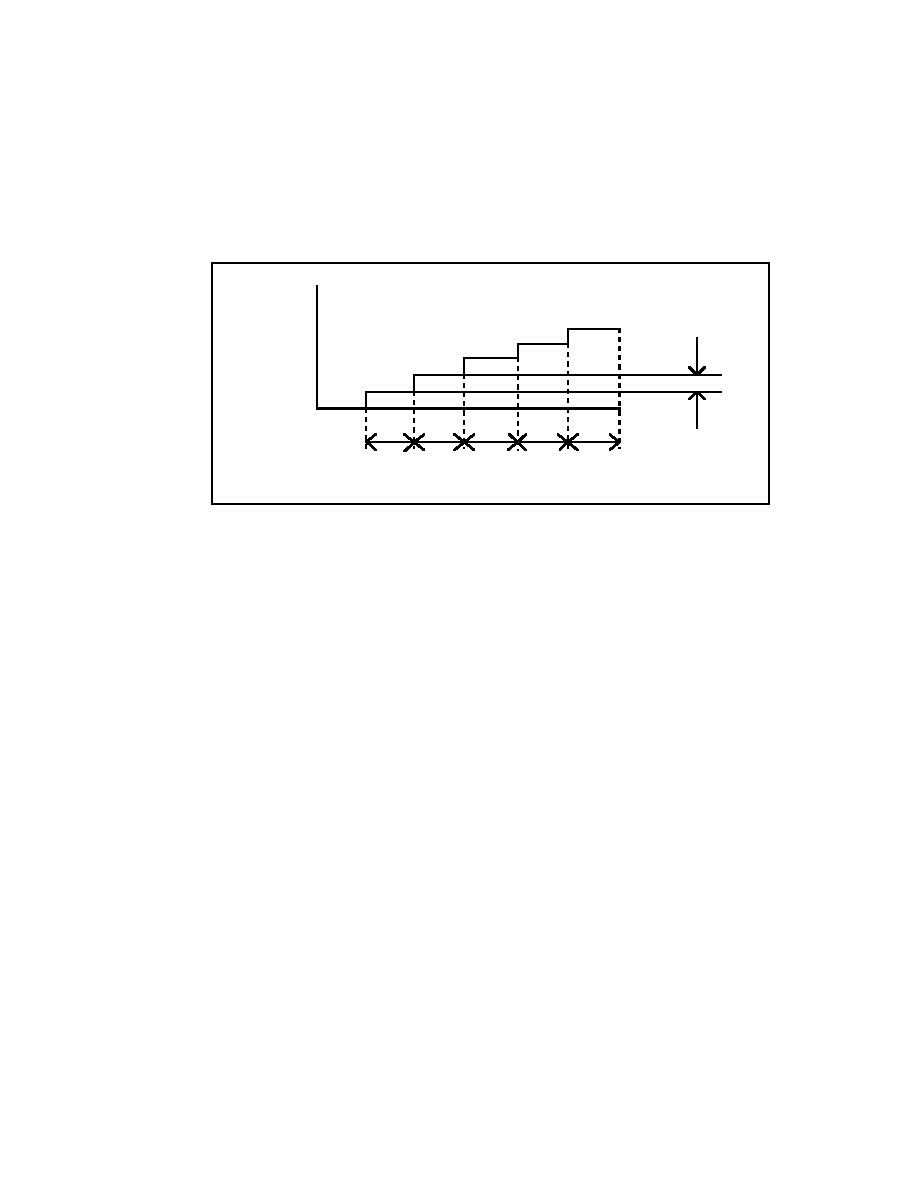

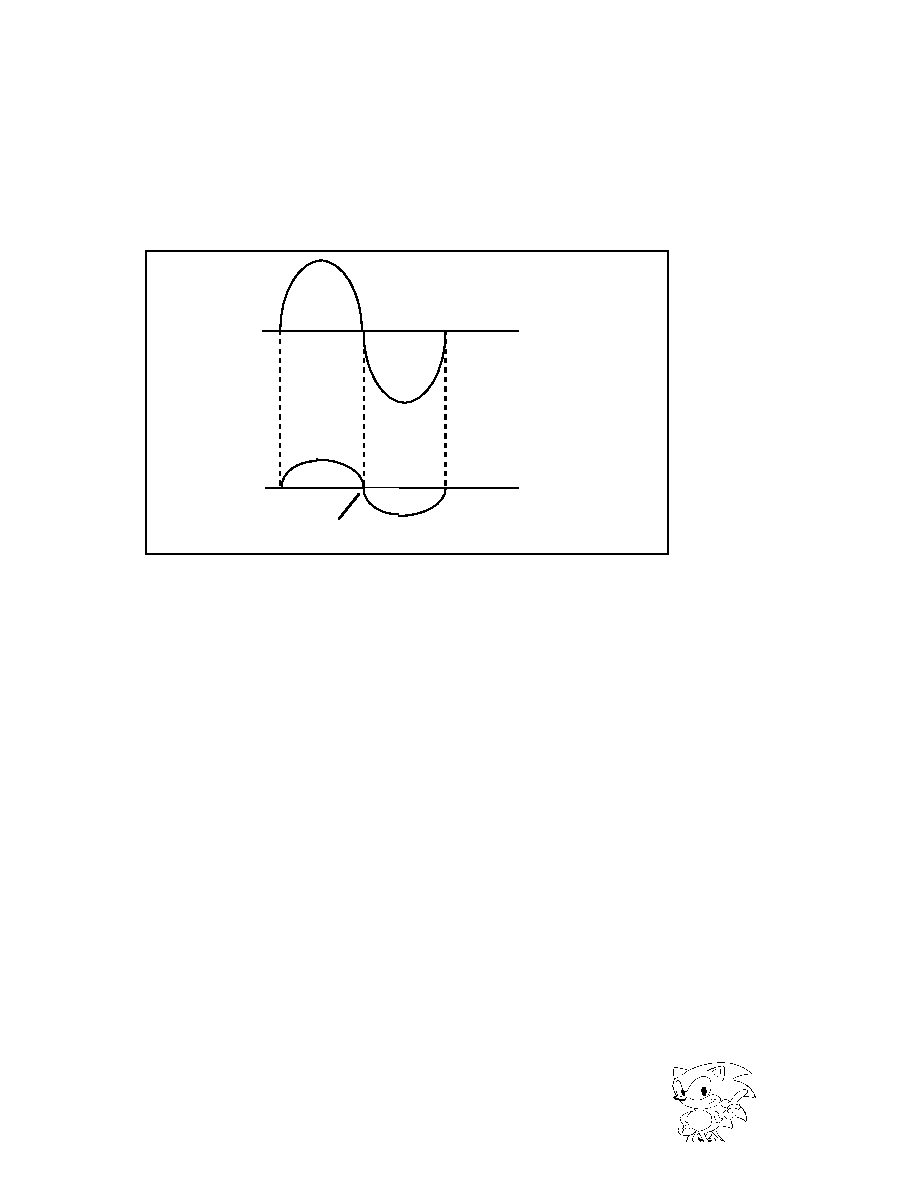

The wave form for each of the normal loop, reversal loop and the alternative loop

can be represented as in figure 4.11. Note that the uuuu, eeee, oooo wave forms are

reversed from huuh, heeh, hooh wave forms.

Attack

Data

Normal Loop

Reversal Loop

Alternative Loop

Attack

Data

Attack

Data

The wave form for each of "huuu, heee, hooo" are defined as shown

below.

Figure 4.11 Loop Wave Forms

|

SEGA Confidential

40

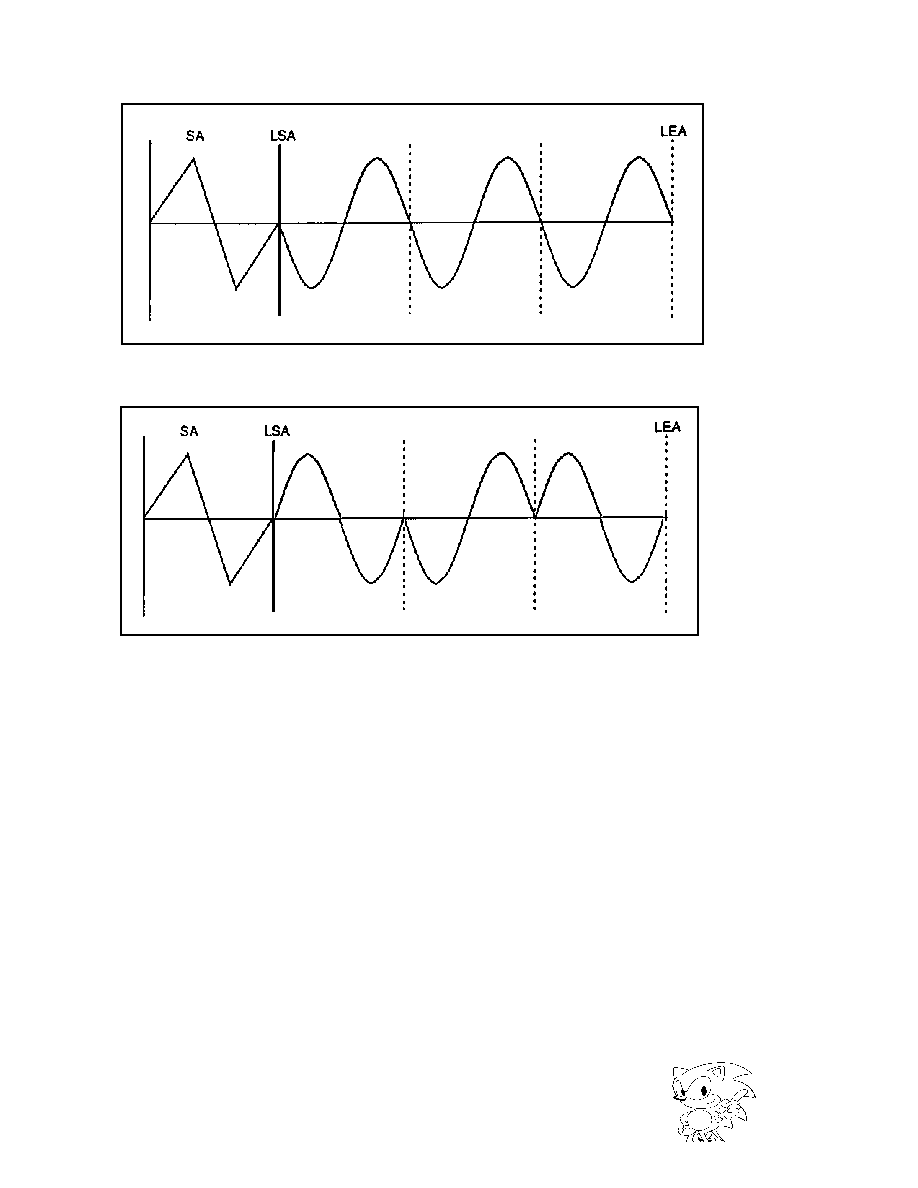

EG Register

EG represents the change occurred by sound attenuation time, and has the following

four states.

· Attack State (Attack segment)

Indicates the start of the sound (start up).

· Decay 1 state (Decay 1 segment)

Indicates attenuation from the maximum volume.

· Decay 2 state (Decay 2 segment)

Indicates attenuation even lower than decay 1.

However, if DR2 is set to "0", the sound is maintained rather than attenuated.

· Release state (Release segment)

Indicates the attenuation until the sound disappears after KEY_OFF.

However, in all cases of sound generation state, EG does not necessarily go through

all four states. Depending on the timing of KEY_OFF various envelope curves are

drawn. An example is shown below.

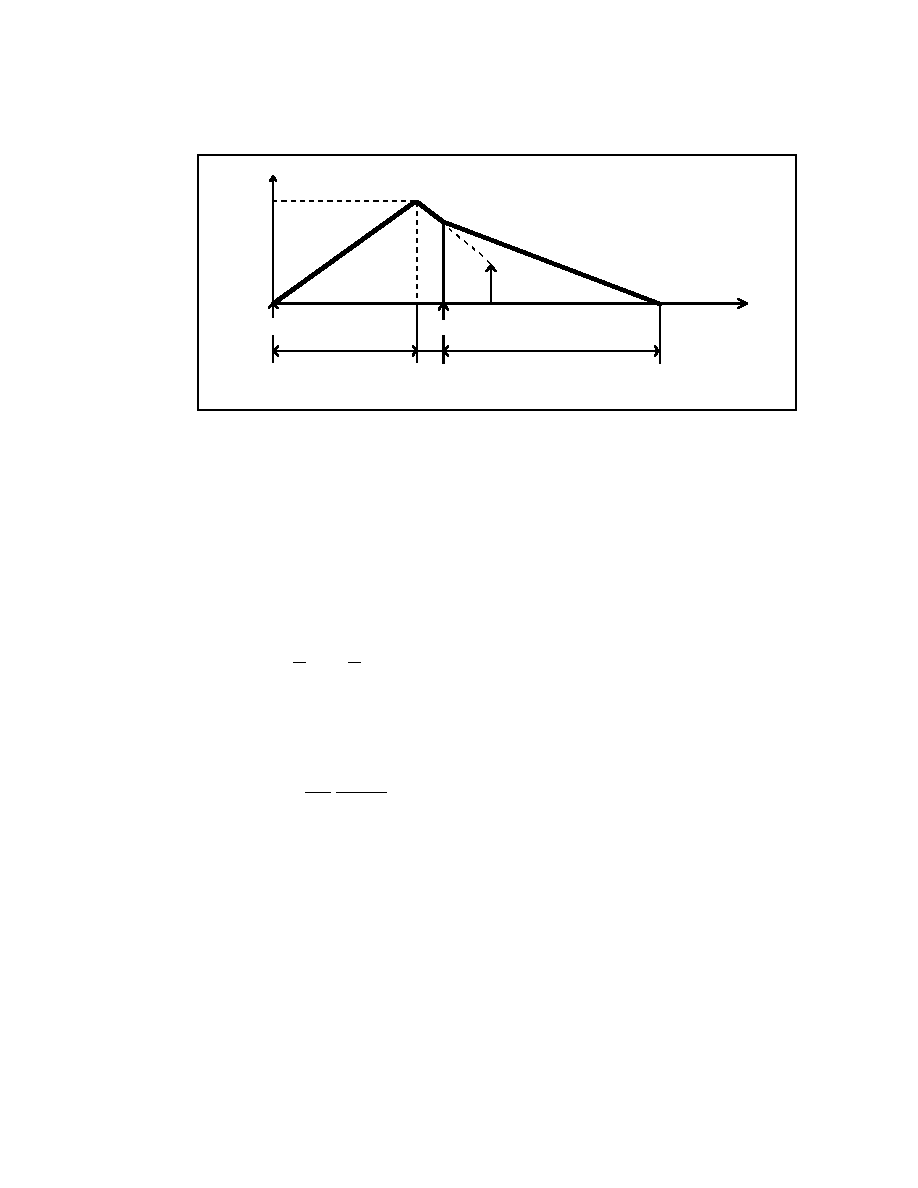

(a)

When KEY_OFF is executed during attack state transition

(Figure 4.12).

EG

000

3FF

KEY-ON

KEY-OFF

Time

KEY-OFF

LEVEL

Attack State

Release State

H

H

Figure 4.12 KEY_OFF During Attack State Transition

When KEY_OFF is executed, from that level (KEY_OFF LEVEL) the

sound is attenuated following the release rate ("RR") setting.

Therefore, in this case, the envelope curve skips the decay 1 and

decay 2 states. In this case, EG value does not reach "000

H

", rather,

with KEY_OFF as a turning point, it increases to "3FF

H

".

|

SEGA Confidential

(b) When KEY_OFF is executed during decay 1 segment transition.

(Figure 4.13).

EG

000

3FF

KEY-ON

KEY-OFF

Time

DL

KEY-OFF

LEVEL

Attack State

Decay 1 State

Release State

H

H

Figure 4.13 KEY_OFF During Decay State Transition

When the decay 1 state starts, it attenuates towards the DL (decay

level) following the D1R (decay 1 rate) set value.

If KEY_OFF is executed during the above operation, the sound starts

to attenuate from the level KEY_OFF was executed (KEY_OFF

LEVEL) according to the value set in RR (release rate).

AR[4:0] (R/W) ; Attack Rate

Designates the change volume of EG in the attack state. When

"AR"="00H", the change volume (level attenuation volume) is

minimum (0). When "AR"="1FH", the change volume (level attenua-

tion volume) is maximum (MAX).

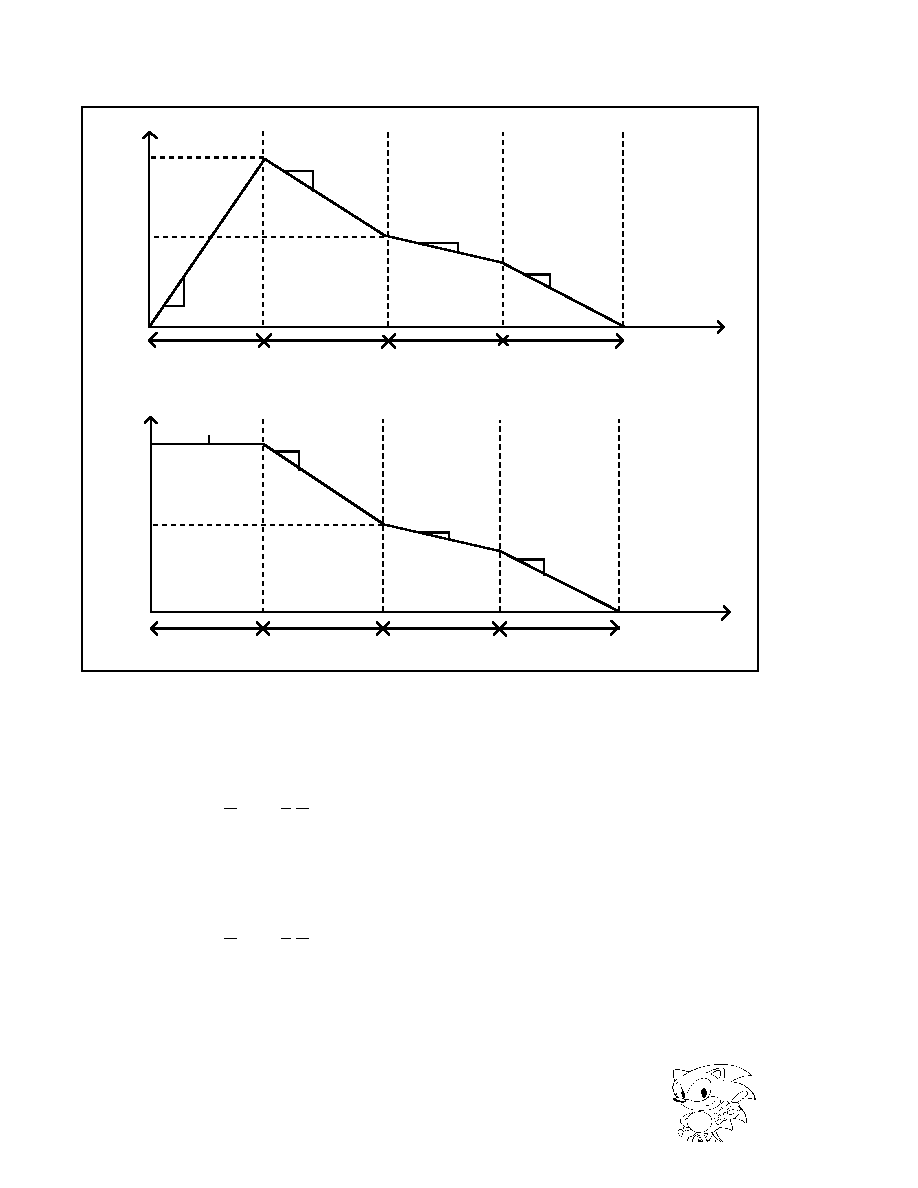

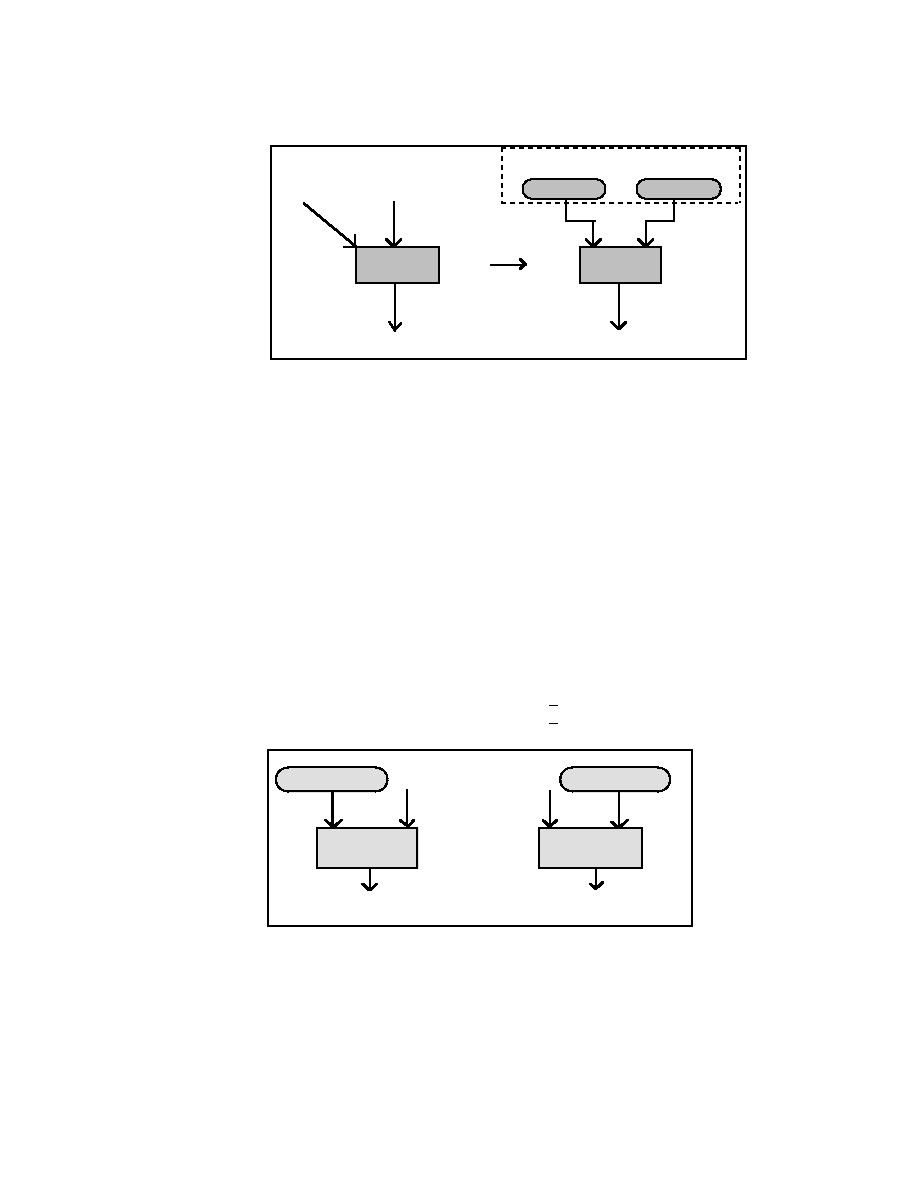

EGHOLD (R/W) EG HOLD mode

Designates whether to maintain or change the attack value. As shown

in Figure 4.12, when this bit is "1B" the attack value is held at "000H".

Also when this bit is "0B", it changes according to the value designated

by the AR register. In the hold mode, the time that EG retains "000H"

(time until it reaches segment 2) is determined by the "AR" value.

Saturn SCSP User's Manual

41

|

SEGA Confidential

When EGHOLD=1

EG

Time

Attack

State

Decay 1

State

Decay 2

State

Release

State

EG

When EGHOLD=0

Time

Attack

State

Decay 1

State

Decay 2

State

Release

State

000H

DL[4:0]

3FFH

000H

DL[4:0]

3FFH

D1R[4:0]

D2R[4:0]

RR[4:0]

AR[4:0]

D1R[4:0]

D2R[4:0]

RR[4:0]

AR[4:0]

Figure 4.14 Change in the Attenuation Volume

D1R[4:0] (R/W) ; Decay-1 Rate

Designates the EG change volume in the decay 1 state. When

"D1R"="00H", the change volume (level attenuation volume) is

minimum (0). When "D1R"="1FH", the change volume (level

attenuation volume) is maximum (MAX).

D2R[4:0] (R/W) ; Decay-2 Rate

Designates the EG change volume in the decay 2 state.When

"D2R"="00H", the change volume (level attenuation volume) is

minimum (0). When "D2R"="1FH", the change volume (level

attenuation volume) is maximum (MAX).

42

|

SEGA Confidential

RR[4:0] (R/W) ; Release Rate

Designates the change volume of the EG in the release state.

When "RR"="00H", the change volume (level attenuation

volume) is minimum (0). When "RR"="1FH", the change

volume (level attenuation volume) is maximum (MAX).

DL{4:0] (R/W) ; Decay Level

Designates the upper 5 bit of the attenuation level (EG) that

moves from decay 1 state to decay 2 state. When the upper

decay 1 state attenuation level upper 5 bits match the DL value,

the state moves to decay state 2. When "DL"="00H", the level

is maximum (MAX). When "DL"="1F

H

", the level is minimum

(MIN).

KRS[3:0] (R/W) Key Rate Scaling

Designates the level of EG key rate scaling condition. 00H

indicates minimum scaling; 0EH designates maximum scaling.

When set to 0FH, it designates that scaling OFF.

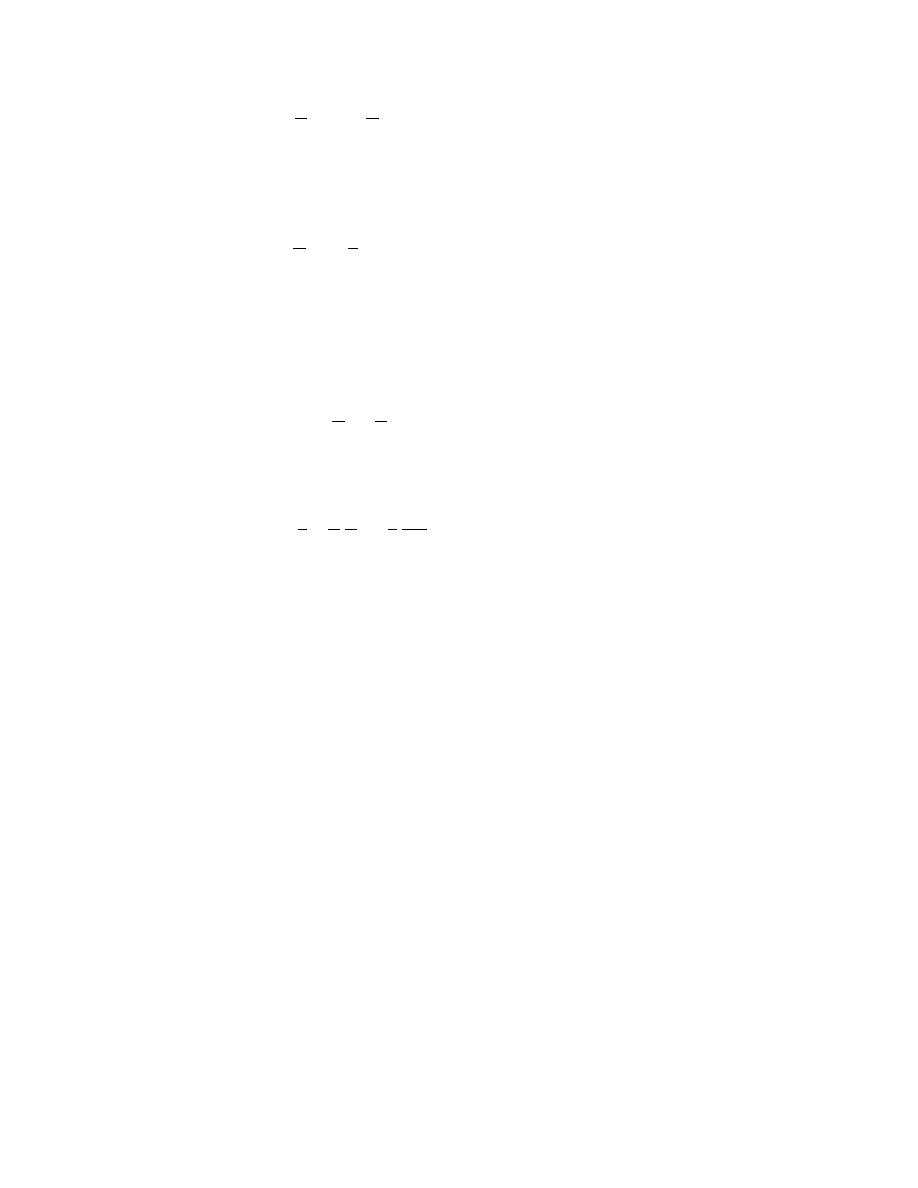

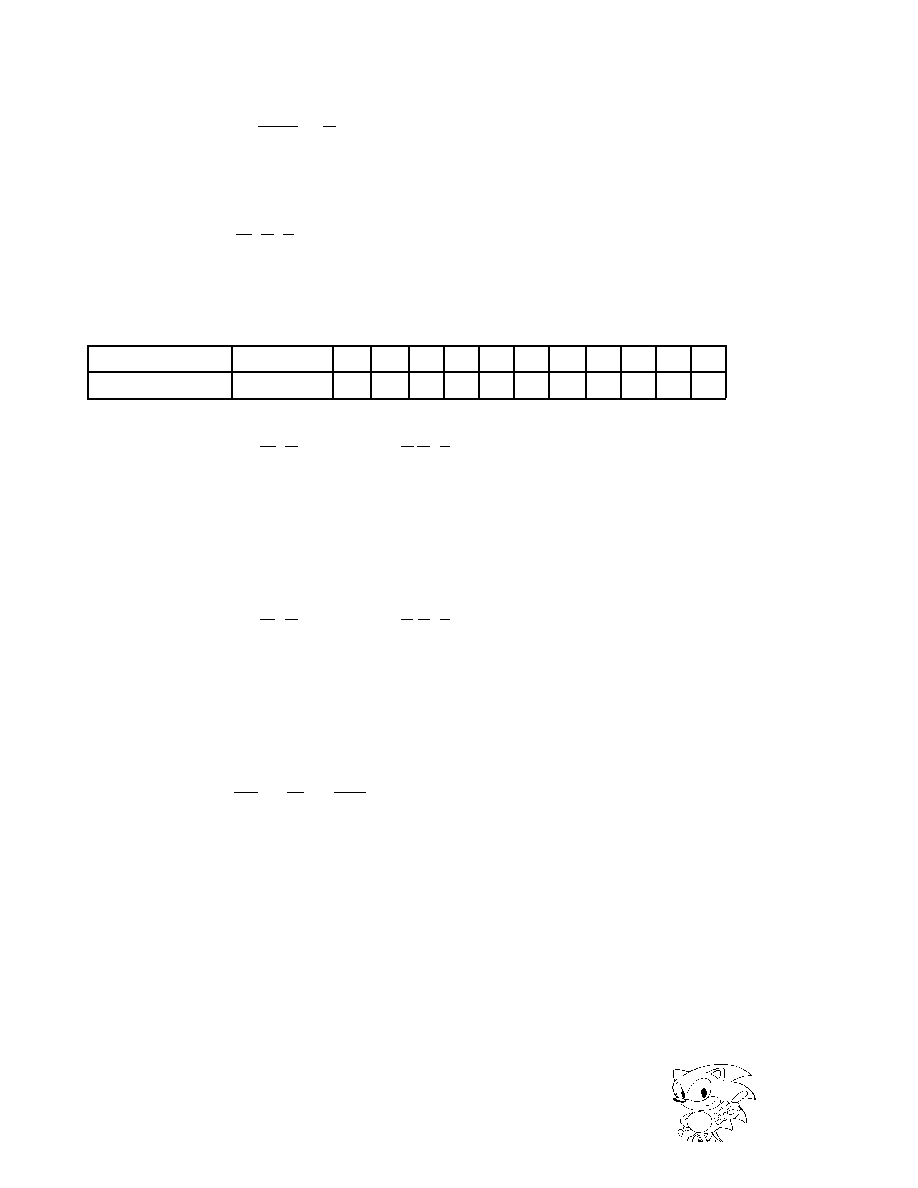

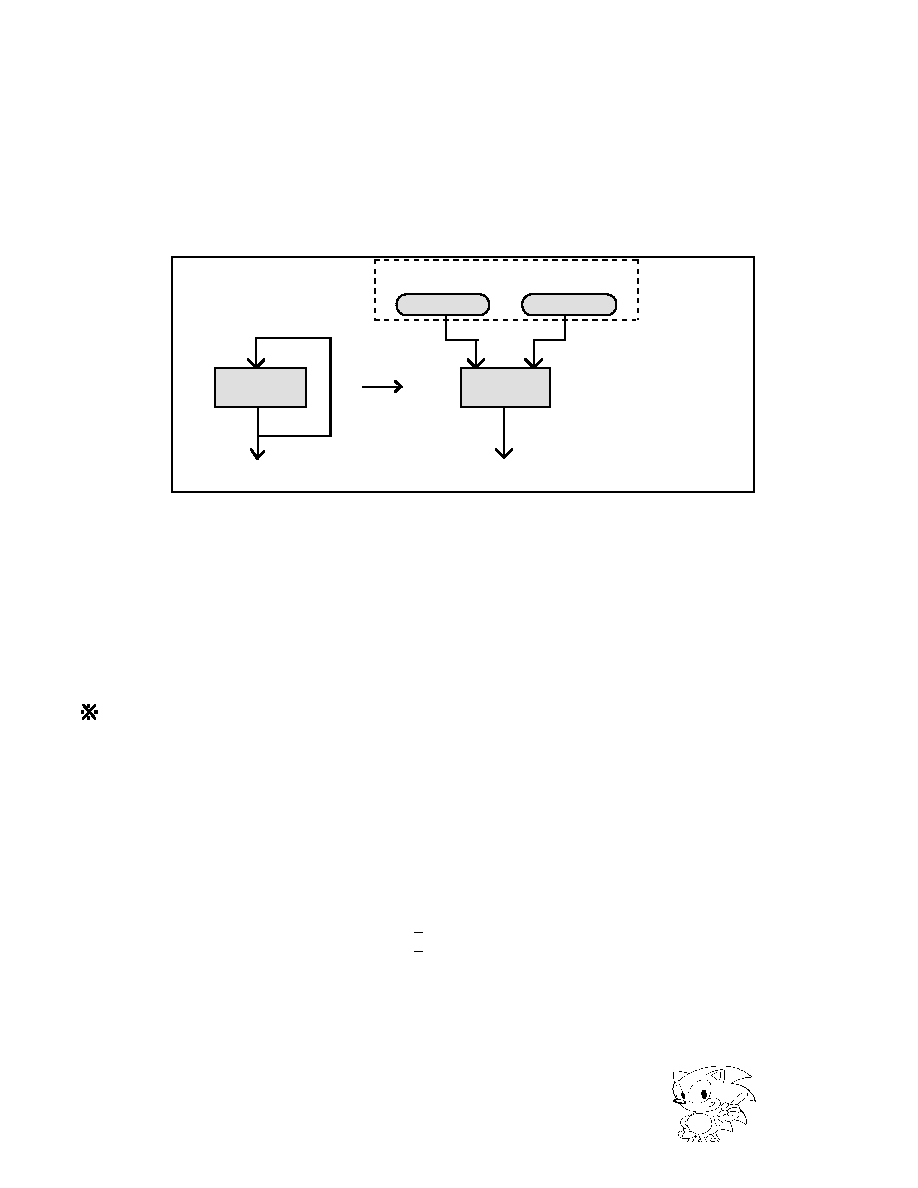

LPSLNK (R/W) ; LooP Start LiNK

The function of the "LPSLNK" (loop start link) is to synchronize

the transition to decay 1 state from the loop start and EG attack

states.

When "LPSLNK" ="0" there is no relation between the EG state

transition and the loop start point position. When "LPSLNK"

="1", the following two changes can be seen.

1) When, in terms of time, EG reaches "000

H

" in the attack state faster than when

the wave form read address reaches the loop start point ("SA"+"LSA") (Figure

4.15). In this case, EG will reach the MAX level first (P.1). However, since

moving to the next segment is not possible (decay 1 state) until the wave form

read address reaches the loop start point, EG is maintained at MAX level. Next,

when the wave form read address reaches the loop start point (P.2) EG will move

to the decay 1 state.

Saturn SCSP User's Manual

43

|

SEGA Confidential

EG

DL

ADDRESS

SA LSP (SA+LSA) :LOOP START POINT

000

3FF

P.1

P.2

Wave Form

Data

Attack

State

Decay 1

State

Time

EG

H

H

Attack

State

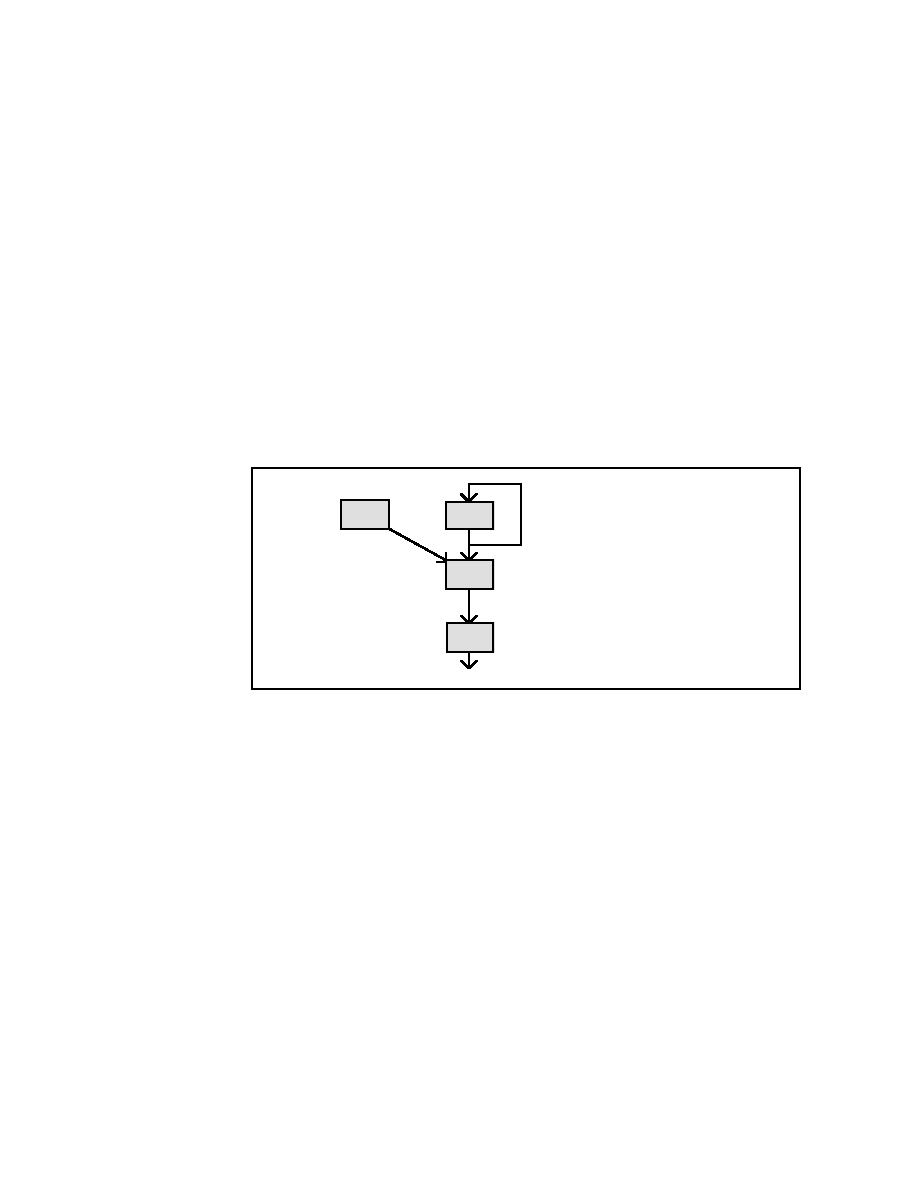

Figure 4.15 Transition (1) from the Attack State to Decay 1

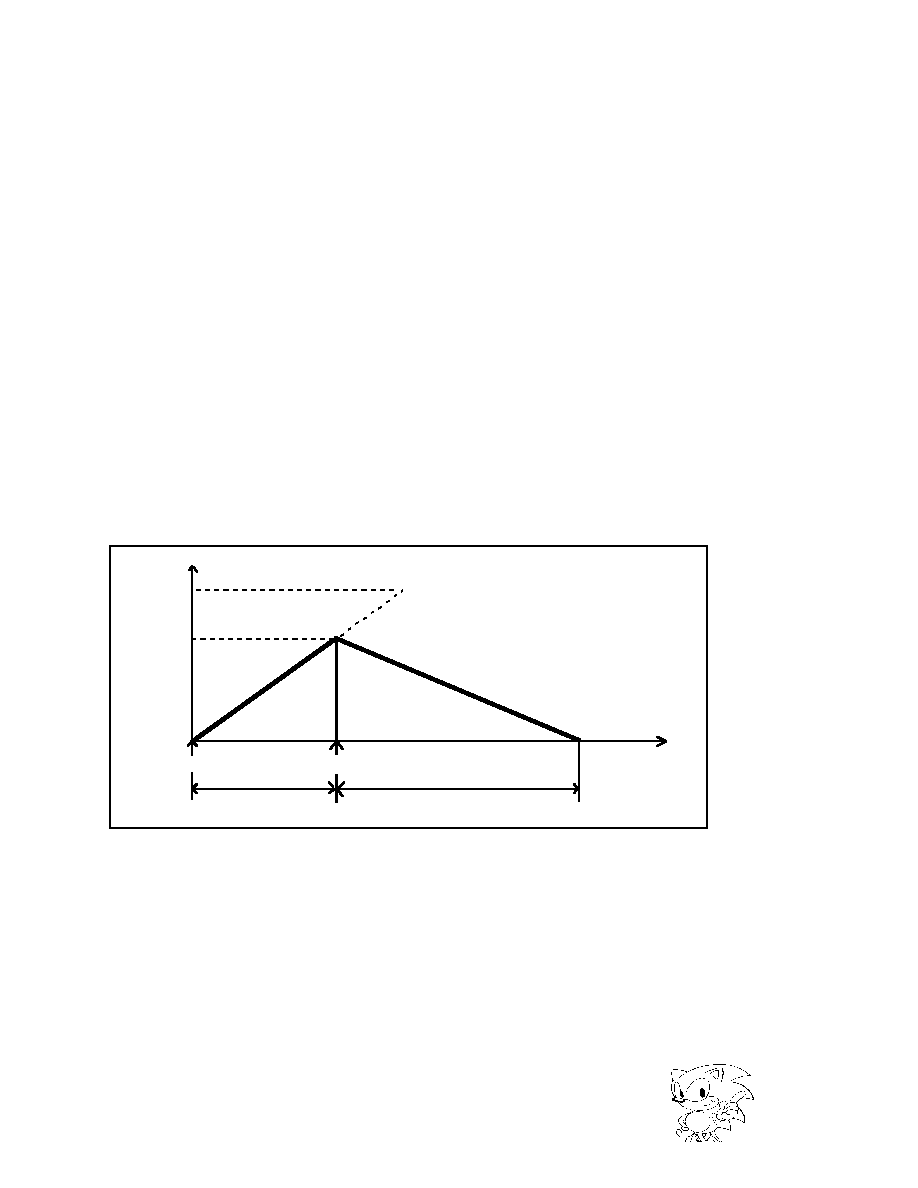

2) In terms of time, EG reaches "000

H

" in the attack state slower than when the

wave form read address reaches the loop start point ("SA"+"LSA").

This pattern has an additional two patterns.

- When the wave form read address reaches the loop start point, and the "SCL"

at this point (EG level) is larger than the "DL" (decay level) (reversed when

compared to the actual EG level). (Figure 4.16)

SA LSP (SA+LSA) :LOOP START POINT

Wave Form

Data

3FF

000

EG

P.

1

P.2

DL

SCL>DL

Time

ADDRESS

Attack

State

Decay 1

State

Decay 2

State

SCL: SEGMENT CHANGE LEVEL

EG

H

H

Figure 4.16 Transition (2) from the Attack State to Decay 1

44

|

SEGA Confidential

After the wave form read address reaches the loop start point, the EG will shift to

the decay 1 state (P.1). Next, when the EG value reaches the DL (decay level), it will

shift to the decay 2 state (P.2).

- When the wave form read address reaches the loop start point, and the "SCL"

at this point (EG level) is smaller than the "DL" (decay level) (reversed when

compared to the actual EG level). (Figure 4.17)

EG

000

3FF

P.1

DL

SCL<DL (SCL=DL)

SCL: SEGMENT CHANGE LEVEL

Time

ADDRESS

Decay 1

Status

Wave Form

Data

SA LSP (SA+LSA) :LOOP START POINT

EG

H

H

Figure 4.17 Transition (3) from the Attack State to Decay 1

After the wave form read address reaches the loop start point, the EG will shift to

the decay 1 state (P.1). After this, since the EG value will no longer reach the

"DL" (decay level), it will continue to retain level 0 (EG value is "3FFH") with-

out moving to decay 2 state.

Saturn SCSP User's Manual

45

|

SEGA Confidential

FM Modulation Control Register

SOUS[15:0] (R/W) ; SOUnd Stack

This is a data buffer for a slot output. It is a 64 word ring buffer

that can hold two generations of sampling data. This is used in

addition to processing between slots and modulation.

MDL[3:0] (R/W) ; MoDuLation level

Specifies the effects (modulation rate) of modulation to the

modulation input source.

Table 4.15 Modulation Rate According to the Register Set Value

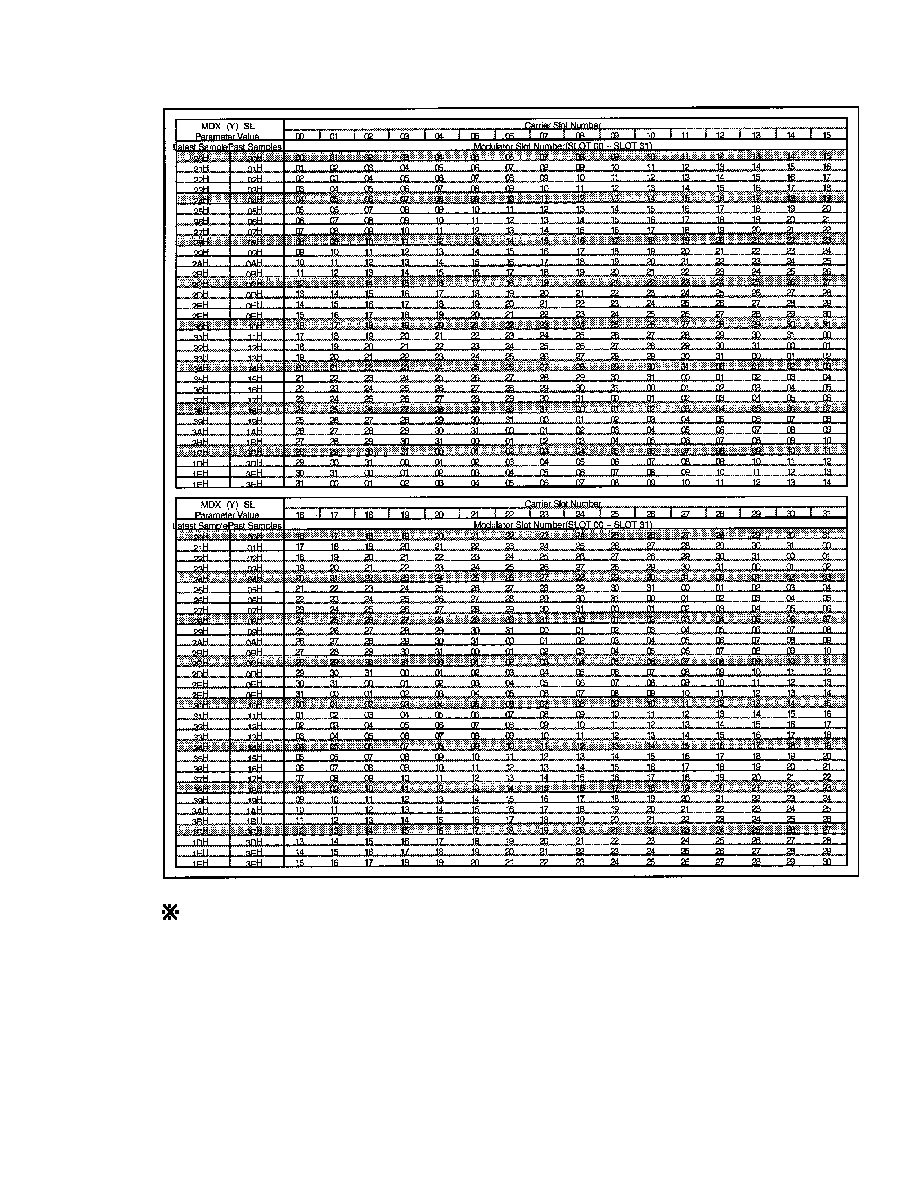

MDXSL[5:0] (R/W) ; MoDulation input-X SeLect

Designates the source to be used as modulation input X. The

modulation input X source slot is specified by two complimen-

tary numbers showing the relative number from the current

slot. Also, when this value is within the range "1C

H

" to 3B

H

" it

shows the latest generation; if out of range it shows one sample

past the latest generation. (See Table 4.16)

MDYSL[5:0] (R/W) ; MoDulation input-Y SeLect

Designates the source to be used as modulation input Y. The

modulator input Y source slot is indicated by two complimen-

tary numbers showing the relative number from the current

slot. Also, when this value is within the range of "1C

H

" to 3B

H

"

it represents the latest generation; if out of range it represents 1

sample past the latest generation. (See Table 4.16)

STWINH (R/W) ; STack Write INHibit

When this bit is "1B", writing the slot output to the direct data

stack ("SOUS") is inhibited. Normally "0B" is fine.

MDL [3:0]

0 ~ 4

5

6

7

8

9

A

B

C

D

E

F

Modulation Rate (

±

n

)

0

1/16

1/8

1/4

1/2

1

2

4

8

16

32

64

46

|

SEGA Confidential

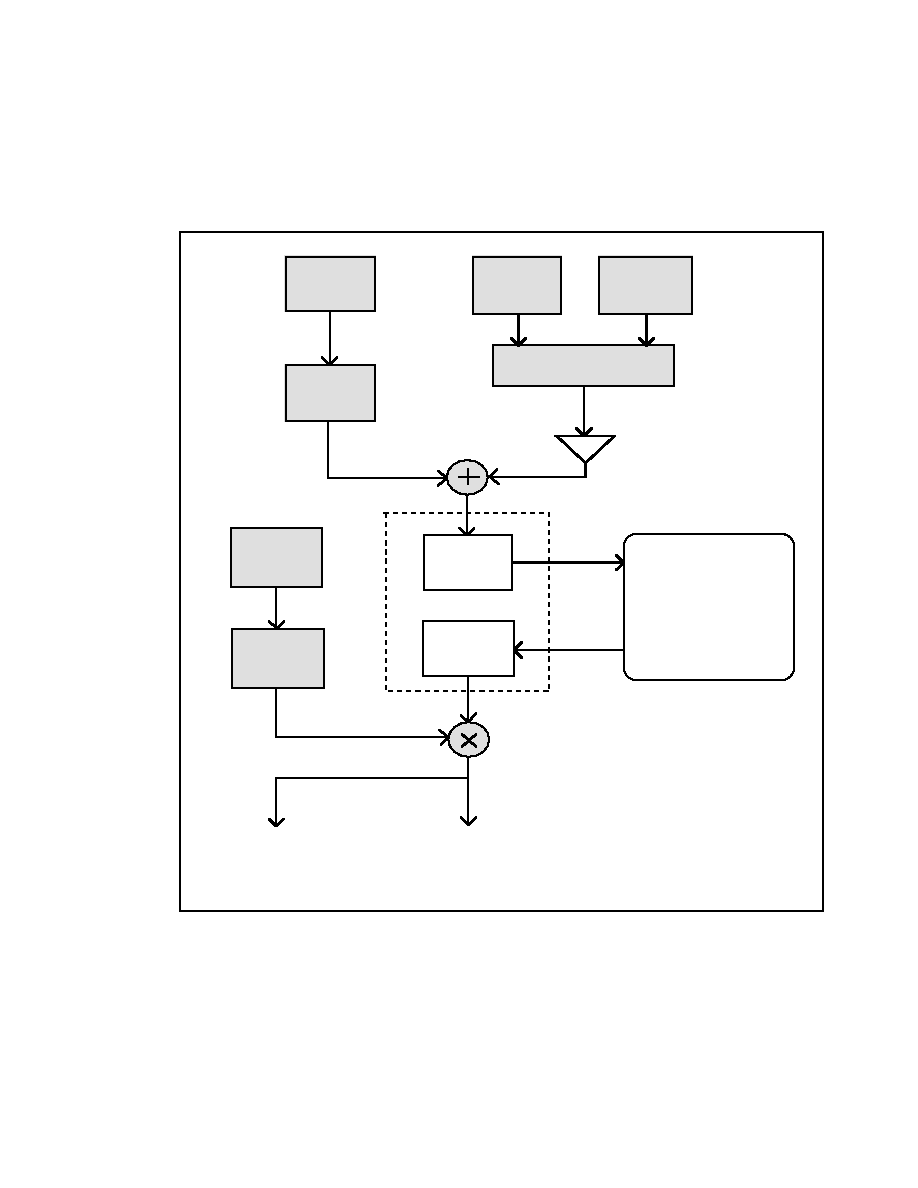

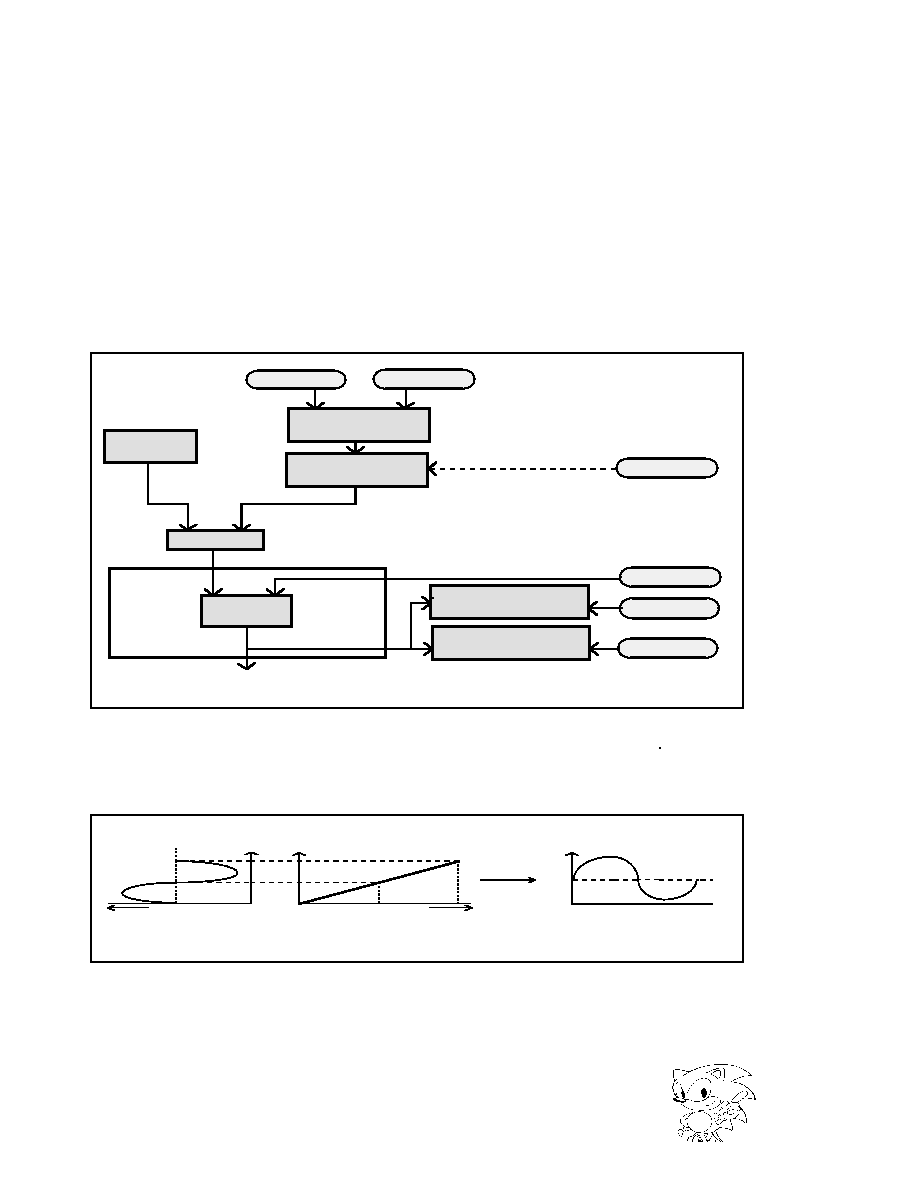

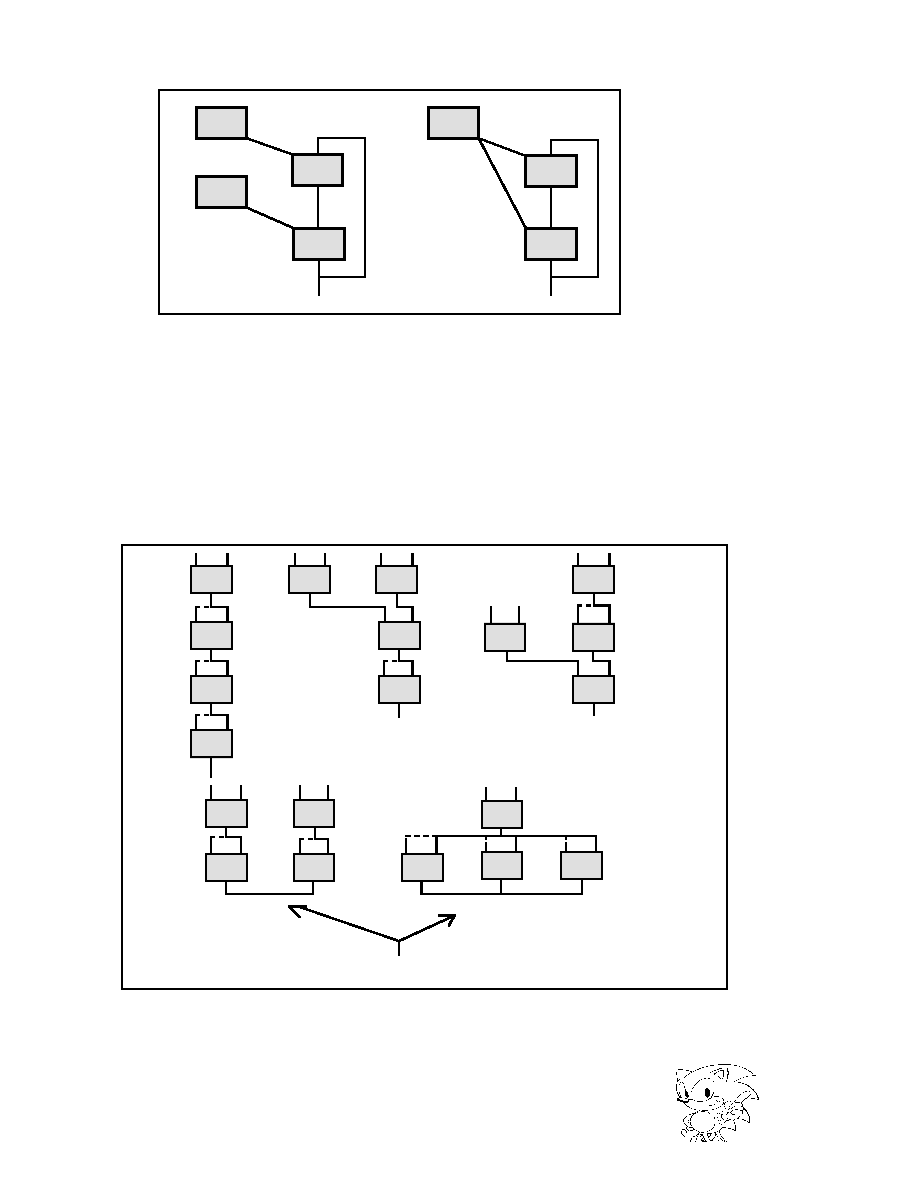

Using the FM Sound Generator Method

The FM sound generator method is a method in which modulation is performed by

adding different wave form generator output to the wave form generator phase

input. FM voice mixing is accomplished by a wave form calculator unit called a slot.

Figure 4.18 shows a block diagram of a slot.

P L F O

P G

SOUND

STACK

DATA

SOUND

STACK

DATA

Averaging Operation

Unit

Waveform Phase

Value

PHASE ADDER

Waveform RAM

MEMORY ADDRESS

WAVE DATA

Waveform

Address

Pointer

Waveform

Data

Buffer

A L F O

E G

Level Coefficient

(Volume)

Waveform Level

Calculation

Output to DIRECT & DSP SLOT OUTPUT

Figure 4.18 SLOT Block Diagram

Saturn SCSP User's Manual

47

|

SEGA Confidential

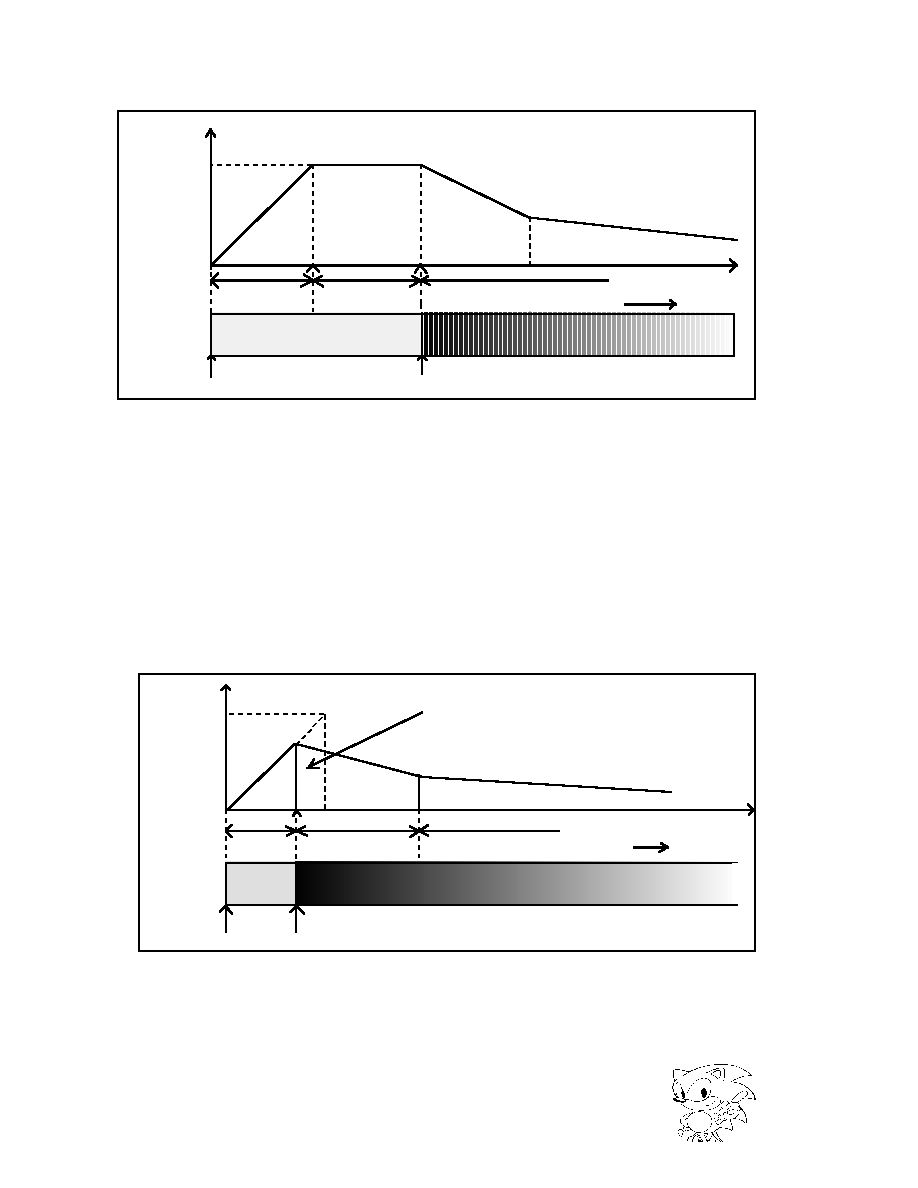

To output a sound from a slot, wave form data required to run the slot is written to

the wave form RAM. Sound is started by the wave form read address, loop start

address, loop end address, sound pitch, sound level, setting the various EG settings,

and turning KEY_ON. SCSP operates as one large cycle of 22.68[

µ

sec] as a whole.

The PG (Phase Generator) controls the reading rate of the waveform, which is deter-

mined by the sound generation frequency setting. As long as the sound frequency

isn't changed, the PG creates a fixed value per 1Fs cycle (22.68[

µ

sec] = 1/44.1KHz),

and it does a cumulative addition per Fs cycle and outputs. As shown in Figure

4.19, this is added to each address pointer. The resulting values are output to the